verilator Model编译之filelist

make -C

/home/cva6/ verilate verilator="verilator --no-timing" target=cv64a6_imafdc_sv39 defines=

make[1]: Entering directory '/home/cva6'

Makefile:153: XCELIUM_HOME not set which is necessary for compiling DPIs when using XCELIUM

[Verilator] Building Model

verilator --no-timing --no-timing verilator_config.vlt

-f core/Flist.cva6 core/cva6_rvfi.sv

/home/cva6/corev_apu/tb/ariane_axi_pkg.sv

/home/cva6/corev_apu/tb/axi_intf.sv

/home/cva6/corev_apu/register_interface/src/reg_intf.sv

/home/cva6/corev_apu/tb/ariane_soc_pkg.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_pkg.sv

/home/cva6/corev_apu/tb/ariane_axi_soc_pkg.sv

/home/cva6/core/cva6_rvfi.sv

/home/cva6/corev_apu/src/ariane.sv

/home/cva6/corev_apu/bootrom/bootrom.sv

/home/cva6/corev_apu/clint/axi_lite_interface.sv

/home/cva6/corev_apu/clint/clint.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb_64_32.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb_wrap.sv

/home/cva6/corev_apu/fpga/src/apb_timer/apb_timer.sv

/home/cva6/corev_apu/fpga/src/apb_timer/timer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_ar_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_aw_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_b_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_r_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_single_slice.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_slice.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_slice_wrap.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_w_buffer.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_res_tbl.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_amos_alu.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_amos.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_atomics.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_atomics_wrap.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_lrsc.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_lrsc_wrap.sv

/home/cva6/corev_apu/axi_mem_if/src/axi2mem.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_csrs.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_cdc.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_jtag.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_jtag_tap.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_mem.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_sba.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_top.sv

/home/cva6/corev_apu/rv_plic/rtl/rv_plic_target.sv

/home/cva6/corev_apu/rv_plic/rtl/rv_plic_gateway.sv

/home/cva6/corev_apu/rv_plic/rtl/plic_regmap.sv

/home/cva6/corev_apu/rv_plic/rtl/plic_top.sv

/home/cva6/corev_apu/riscv-dbg/debug_rom/debug_rom.sv

/home/cva6/corev_apu/register_interface/src/apb_to_reg.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_multicut.sv

/home/cva6/vendor/pulp-platform/common_cells/src/rstgen_bypass.sv

/home/cva6/vendor/pulp-platform/common_cells/src/rstgen.sv

/home/cva6/vendor/pulp-platform/common_cells/src/addr_decode.sv

/home/cva6/vendor/pulp-platform/common_cells/src/stream_register.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_cut.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_join.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_delayer.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_to_axi_lite.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_id_prepend.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_atop_filter.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_err_slv.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_mux.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_demux.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_xbar.sv

/home/cva6/vendor/pulp-platform/common_cells/src/cdc_2phase.sv

/home/cva6/vendor/pulp-platform/common_cells/src/spill_register_flushable.sv

/home/cva6/vendor/pulp-platform/common_cells/src/spill_register.sv

/home/cva6/vendor/pulp-platform/common_cells/src/deprecated/fifo_v1.sv

/home/cva6/vendor/pulp-platform/common_cells/src/deprecated/fifo_v2.sv

/home/cva6/vendor/pulp-platform/common_cells/src/stream_delay.sv

/home/cva6/vendor/pulp-platform/common_cells/src/lfsr_16bit.sv

/home/cva6/vendor/pulp-platform/tech_cells_generic/src/deprecated/cluster_clk_cells.sv

/home/cva6/vendor/pulp-platform/tech_cells_generic/src/deprecated/pulp_clk_cells.sv

/home/cva6/vendor/pulp-platform/tech_cells_generic/src/rtl/tc_clk.sv

/home/cva6/corev_apu/tb/ariane_testharness.sv

/home/cva6/corev_apu/tb/ariane_peripherals.sv

/home/cva6/corev_apu/tb/rvfi_tracer.sv

/home/cva6/corev_apu/tb/common/uart.sv

/home/cva6/corev_apu/tb/common/SimDTM.sv

/home/cva6/corev_apu/tb/common/SimJTAG.sv

+define+ corev_apu/tb/common/mock_uart.sv

+incdir+corev_apu/axi_node

--unroll-count 256 -Wall -Werror-PINMISSING -Werror-IMPLICIT -Wno-fatal

-Wno-PINCONNECTEMPTY -Wno-ASSIGNDLY -Wno-DECLFILENAME

-Wno-UNUSED -Wno-UNOPTFLAT -Wno-BLKANDNBLK -Wno-style

-DPRELOAD=1 -LDFLAGS "-L/home/RISCV_TOOLS/lib

-L/home/cva6/tools/spike/lib

-Wl,-rpath,/home/RISCV_TOOLS/lib

-Wl,-rpath,/home/cva6/tools/spike/lib

-lfesvr -lriscv -ldisasm -lyaml-cpp -lpthread "

-CFLAGS "-I/include

-I/include

-I/home/cva6/tools/verilator-v5.008/share/verilator/include/vltstd

-I/home/RISCV_TOOLS/include

-I/home/cva6/tools/spike/include -std=c++17

-I/home/cva6/corev_apu/tb/dpi -O3 -DVL_DEBUG

-I/home/cva6/tools/spike" --cc --vpi

+incdir+/home/cva6/vendor/pulp-platform/common_cells/include/

+incdir+/home/cva6/vendor/pulp-platform/axi/include/

+incdir+/home/cva6/corev_apu/register_interface/include/

+incdir+/home/cva6/corev_apu/tb/common/

+incdir+/home/cva6/vendor/pulp-platform/axi/include/

+incdir+/home/cva6/verif/core-v-verif/lib/uvm_agents/uvma_rvfi/

+incdir+/home/cva6/verif/core-v-verif/lib/uvm_components/uvmc_rvfi_reference_model/

+incdir+/home/cva6/verif/core-v-verif/lib/uvm_components/uvmc_rvfi_scoreboard/

+incdir+/home/cva6/verif/core-v-verif/lib/uvm_agents/uvma_core_cntrl/

+incdir+/home/cva6/verif/tb/core/

+incdir+/home/cva6/core/include/

+incdir+/home/cva6/tools/spike/include/disasm/

--top-module ariane_testharness --threads-dpi none --Mdir work-ver -O3

--exe corev_apu/tb/ariane_tb.cpp

corev_apu/tb/dpi/SimDTM.cc

corev_apu/tb/dpi/SimJTAG.cc

corev_apu/tb/dpi/remote_bitbang.cc

corev_apu/tb/dpi/msim_helper.cc

filelist 列表

core/Flist.cva6 core/cva6_rvfi.sv

/home/cva6/corev_apu/tb/ariane_axi_pkg.sv

/home/cva6/corev_apu/tb/axi_intf.sv

/home/cva6/corev_apu/register_interface/src/reg_intf.sv

/home/cva6/corev_apu/tb/ariane_soc_pkg.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_pkg.sv

/home/cva6/corev_apu/tb/ariane_axi_soc_pkg.sv

/home/cva6/core/cva6_rvfi.sv

/home/cva6/corev_apu/src/ariane.sv

/home/cva6/corev_apu/bootrom/bootrom.sv

/home/cva6/corev_apu/clint/axi_lite_interface.sv

/home/cva6/corev_apu/clint/clint.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb_64_32.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb_wrap.sv

/home/cva6/corev_apu/fpga/src/apb_timer/apb_timer.sv

/home/cva6/corev_apu/fpga/src/apb_timer/timer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_ar_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_aw_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_b_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_r_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_single_slice.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_slice.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_slice_wrap.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_w_buffer.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_res_tbl.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_amos_alu.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_amos.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_atomics.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_atomics_wrap.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_lrsc.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_lrsc_wrap.sv

/home/cva6/corev_apu/axi_mem_if/src/axi2mem.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_csrs.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_cdc.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_jtag.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_jtag_tap.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_mem.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_sba.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_top.sv

/home/cva6/corev_apu/rv_plic/rtl/rv_plic_target.sv

/home/cva6/corev_apu/rv_plic/rtl/rv_plic_gateway.sv

/home/cva6/corev_apu/rv_plic/rtl/plic_regmap.sv

/home/cva6/corev_apu/rv_plic/rtl/plic_top.sv

/home/cva6/corev_apu/riscv-dbg/debug_rom/debug_rom.sv

/home/cva6/corev_apu/register_interface/src/apb_to_reg.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_multicut.sv

/home/cva6/vendor/pulp-platform/common_cells/src/rstgen_bypass.sv

/home/cva6/vendor/pulp-platform/common_cells/src/rstgen.sv

/home/cva6/vendor/pulp-platform/common_cells/src/addr_decode.sv

/home/cva6/vendor/pulp-platform/common_cells/src/stream_register.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_cut.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_join.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_delayer.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_to_axi_lite.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_id_prepend.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_atop_filter.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_err_slv.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_mux.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_demux.sv

/home/cva6/vendor/pulp-platform/axi/src/axi_xbar.sv

/home/cva6/vendor/pulp-platform/common_cells/src/cdc_2phase.sv

/home/cva6/vendor/pulp-platform/common_cells/src/spill_register_flushable.sv

/home/cva6/vendor/pulp-platform/common_cells/src/spill_register.sv

/home/cva6/vendor/pulp-platform/common_cells/src/deprecated/fifo_v1.sv

/home/cva6/vendor/pulp-platform/common_cells/src/deprecated/fifo_v2.sv

/home/cva6/vendor/pulp-platform/common_cells/src/stream_delay.sv

/home/cva6/vendor/pulp-platform/common_cells/src/lfsr_16bit.sv

/home/cva6/vendor/pulp-platform/tech_cells_generic/src/deprecated/cluster_clk_cells.sv

/home/cva6/vendor/pulp-platform/tech_cells_generic/src/deprecated/pulp_clk_cells.sv

/home/cva6/vendor/pulp-platform/tech_cells_generic/src/rtl/tc_clk.sv

/home/cva6/corev_apu/tb/ariane_testharness.sv

/home/cva6/corev_apu/tb/ariane_peripherals.sv

/home/cva6/corev_apu/tb/rvfi_tracer.sv

/home/cva6/corev_apu/tb/common/uart.sv

/home/cva6/corev_apu/tb/common/SimDTM.sv

/home/cva6/corev_apu/tb/common/SimJTAG.sv

+define+ corev_apu/tb/common/mock_uart.sv

corev_apu/tb/ariane_tb.cpp

corev_apu/tb/dpi/SimDTM.cc

corev_apu/tb/dpi/SimJTAG.cc

corev_apu/tb/dpi/remote_bitbang.cc

corev_apu/tb/dpi/msim_helper.c

core/Flist.cva6

///

//

// Manifest for the CVA6 CORE RTL model.

// - This is a CORE-ONLY manifest.

// - Relevent synthesis and simulation scripts/Makefiles must set the shell

// ENV variable CVA6_REPO_DIR.

//

///

//FPGA memories

${CVA6_REPO_DIR}/vendor/pulp-platform/fpga-support/rtl/SyncDpRam.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/fpga-support/rtl/AsyncDpRam.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/fpga-support/rtl/AsyncThreePortRam.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/fpga-support/rtl/SyncThreePortRam.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/fpga-support/rtl/SyncDpRam_ind_r_w.sv

+incdir+${CVA6_REPO_DIR}/core/include/

+incdir+${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/include/

+incdir+${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/

+incdir+${CVA6_REPO_DIR}/vendor/pulp-platform/axi/include/

+incdir+${CVA6_REPO_DIR}/common/local/util/

// Floating point unit

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_pkg.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_cast_multi.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_classifier.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_divsqrt_multi.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_fma_multi.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_fma.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_noncomp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_opgroup_block.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_opgroup_fmt_slice.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_opgroup_multifmt_slice.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_rounding.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpnew_top.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/defs_div_sqrt_mvp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/control_mvp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/div_sqrt_top_mvp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/iteration_div_sqrt_mvp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/norm_div_sqrt_mvp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/nrbd_nrsc_mvp.sv

${CVA6_REPO_DIR}/core/cvfpu/src/fpu_div_sqrt_mvp/hdl/preprocess_mvp.sv

${CVA6_REPO_DIR}/core/include/config_pkg.sv

${CVA6_REPO_DIR}/core/include/${TARGET_CFG}_config_pkg.sv

${CVA6_REPO_DIR}/core/include/riscv_pkg.sv

// Note: depends on fpnew_pkg, above

${CVA6_REPO_DIR}/core/include/ariane_pkg.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/axi/src/axi_pkg.sv

// Packages

${CVA6_REPO_DIR}/core/include/wt_cache_pkg.sv

${CVA6_REPO_DIR}/core/include/std_cache_pkg.sv

${CVA6_REPO_DIR}/core/include/instr_tracer_pkg.sv

${CVA6_REPO_DIR}/core/include/build_config_pkg.sv

//CVXIF

${CVA6_REPO_DIR}/core/cvxif_compressed_if_driver.sv

${CVA6_REPO_DIR}/core/cvxif_issue_register_commit_if_driver.sv

${CVA6_REPO_DIR}/core/cvxif_example/include/cvxif_instr_pkg.sv

${CVA6_REPO_DIR}/core/cvxif_fu.sv

${CVA6_REPO_DIR}/core/cvxif_example/cvxif_example_coprocessor.sv

${CVA6_REPO_DIR}/core/cvxif_example/instr_decoder.sv

${CVA6_REPO_DIR}/core/cvxif_example/compressed_instr_decoder.sv

${CVA6_REPO_DIR}/core/cvxif_example/copro_alu.sv

// Common Cells

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/cf_math_pkg.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/fifo_v3.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/lfsr.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/lfsr_8bit.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/stream_arbiter.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/stream_arbiter_flushable.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/stream_mux.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/stream_demux.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/lzc.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/rr_arb_tree.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/shift_reg.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/unread.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/popcount.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/exp_backoff.sv

// Common Cells for example coprocessor

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/counter.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/common_cells/src/delta_counter.sv

// Top-level source files (not necessarily instantiated at the top of the cva6).

${CVA6_REPO_DIR}/core/cva6.sv

${CVA6_REPO_DIR}/core/cva6_rvfi_probes.sv

${CVA6_REPO_DIR}/core/alu.sv

// Note: depends on fpnew_pkg, above

${CVA6_REPO_DIR}/core/fpu_wrap.sv

${CVA6_REPO_DIR}/core/branch_unit.sv

${CVA6_REPO_DIR}/core/compressed_decoder.sv

${CVA6_REPO_DIR}/core/macro_decoder.sv

${CVA6_REPO_DIR}/core/controller.sv

${CVA6_REPO_DIR}/core/zcmt_decoder.sv

${CVA6_REPO_DIR}/core/csr_buffer.sv

${CVA6_REPO_DIR}/core/csr_regfile.sv

${CVA6_REPO_DIR}/core/decoder.sv

${CVA6_REPO_DIR}/core/ex_stage.sv

${CVA6_REPO_DIR}/core/instr_realign.sv

${CVA6_REPO_DIR}/core/id_stage.sv

${CVA6_REPO_DIR}/core/issue_read_operands.sv

${CVA6_REPO_DIR}/core/issue_stage.sv

${CVA6_REPO_DIR}/core/load_unit.sv

${CVA6_REPO_DIR}/core/load_store_unit.sv

${CVA6_REPO_DIR}/core/lsu_bypass.sv

${CVA6_REPO_DIR}/core/mult.sv

${CVA6_REPO_DIR}/core/multiplier.sv

${CVA6_REPO_DIR}/core/serdiv.sv

${CVA6_REPO_DIR}/core/perf_counters.sv

${CVA6_REPO_DIR}/core/ariane_regfile_ff.sv

${CVA6_REPO_DIR}/core/ariane_regfile_fpga.sv

// NOTE: scoreboard.sv modified for DSIM (unchanged for other simulators)

${CVA6_REPO_DIR}/core/scoreboard.sv

${CVA6_REPO_DIR}/core/store_buffer.sv

${CVA6_REPO_DIR}/core/amo_buffer.sv

${CVA6_REPO_DIR}/core/store_unit.sv

${CVA6_REPO_DIR}/core/commit_stage.sv

${CVA6_REPO_DIR}/core/axi_shim.sv

${CVA6_REPO_DIR}/core/cva6_accel_first_pass_decoder_stub.sv

${CVA6_REPO_DIR}/core/acc_dispatcher.sv

${CVA6_REPO_DIR}/core/cva6_fifo_v3.sv

// What is "frontend"?

${CVA6_REPO_DIR}/core/frontend/btb.sv

${CVA6_REPO_DIR}/core/frontend/bht.sv

${CVA6_REPO_DIR}/core/frontend/bht2lvl.sv

${CVA6_REPO_DIR}/core/frontend/ras.sv

${CVA6_REPO_DIR}/core/frontend/instr_scan.sv

${CVA6_REPO_DIR}/core/frontend/instr_queue.sv

${CVA6_REPO_DIR}/core/frontend/frontend.sv

// Cache subsystem

${CVA6_REPO_DIR}/core/cache_subsystem/wt_dcache_ctrl.sv

${CVA6_REPO_DIR}/core/cache_subsystem/wt_dcache_mem.sv

${CVA6_REPO_DIR}/core/cache_subsystem/wt_dcache_missunit.sv

${CVA6_REPO_DIR}/core/cache_subsystem/wt_dcache_wbuffer.sv

${CVA6_REPO_DIR}/core/cache_subsystem/wt_dcache.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cva6_icache.sv

${CVA6_REPO_DIR}/core/cache_subsystem/wt_cache_subsystem.sv

${CVA6_REPO_DIR}/core/cache_subsystem/wt_axi_adapter.sv

${CVA6_REPO_DIR}/core/cache_subsystem/tag_cmp.sv

${CVA6_REPO_DIR}/core/cache_subsystem/axi_adapter.sv

${CVA6_REPO_DIR}/core/cache_subsystem/miss_handler.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cache_ctrl.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cva6_icache_axi_wrapper.sv

${CVA6_REPO_DIR}/core/cache_subsystem/std_cache_subsystem.sv

${CVA6_REPO_DIR}/core/cache_subsystem/std_nbdcache.sv

-F ${HPDCACHE_DIR}/rtl/hpdcache.Flist

${HPDCACHE_DIR}/rtl/src/utils/hpdcache_mem_resp_demux.sv

${HPDCACHE_DIR}/rtl/src/utils/hpdcache_mem_to_axi_read.sv

${HPDCACHE_DIR}/rtl/src/utils/hpdcache_mem_to_axi_write.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cva6_hpdcache_subsystem.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cva6_hpdcache_subsystem_axi_arbiter.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cva6_hpdcache_if_adapter.sv

${CVA6_REPO_DIR}/core/cache_subsystem/cva6_hpdcache_wrapper.sv

${HPDCACHE_DIR}/rtl/src/common/macros/behav/hpdcache_sram_1rw.sv

${HPDCACHE_DIR}/rtl/src/common/macros/behav/hpdcache_sram_wbyteenable_1rw.sv

${HPDCACHE_DIR}/rtl/src/common/macros/behav/hpdcache_sram_wmask_1rw.sv

// Physical Memory Protection

// NOTE: pmp.sv modified for DSIM (unchanged for other simulators)

${CVA6_REPO_DIR}/core/pmp/src/pmp.sv

${CVA6_REPO_DIR}/core/pmp/src/pmp_entry.sv

${CVA6_REPO_DIR}/core/pmp/src/pmp_data_if.sv

// Tracer (behavioral code, not RTL)

${CVA6_REPO_DIR}/common/local/util/instr_tracer.sv

${CVA6_REPO_DIR}/common/local/util/tc_sram_wrapper.sv

${CVA6_REPO_DIR}/common/local/util/tc_sram_wrapper_cache_techno.sv

${CVA6_REPO_DIR}/vendor/pulp-platform/tech_cells_generic/src/rtl/tc_sram.sv

${CVA6_REPO_DIR}/common/local/util/sram.sv

${CVA6_REPO_DIR}/common/local/util/sram_cache.sv

// MMU

${CVA6_REPO_DIR}/core/cva6_mmu/cva6_mmu.sv

${CVA6_REPO_DIR}/core/cva6_mmu/cva6_ptw.sv

${CVA6_REPO_DIR}/core/cva6_mmu/cva6_tlb.sv

${CVA6_REPO_DIR}/core/cva6_mmu/cva6_shared_tlb.sv

// end of manifest

corev_apu

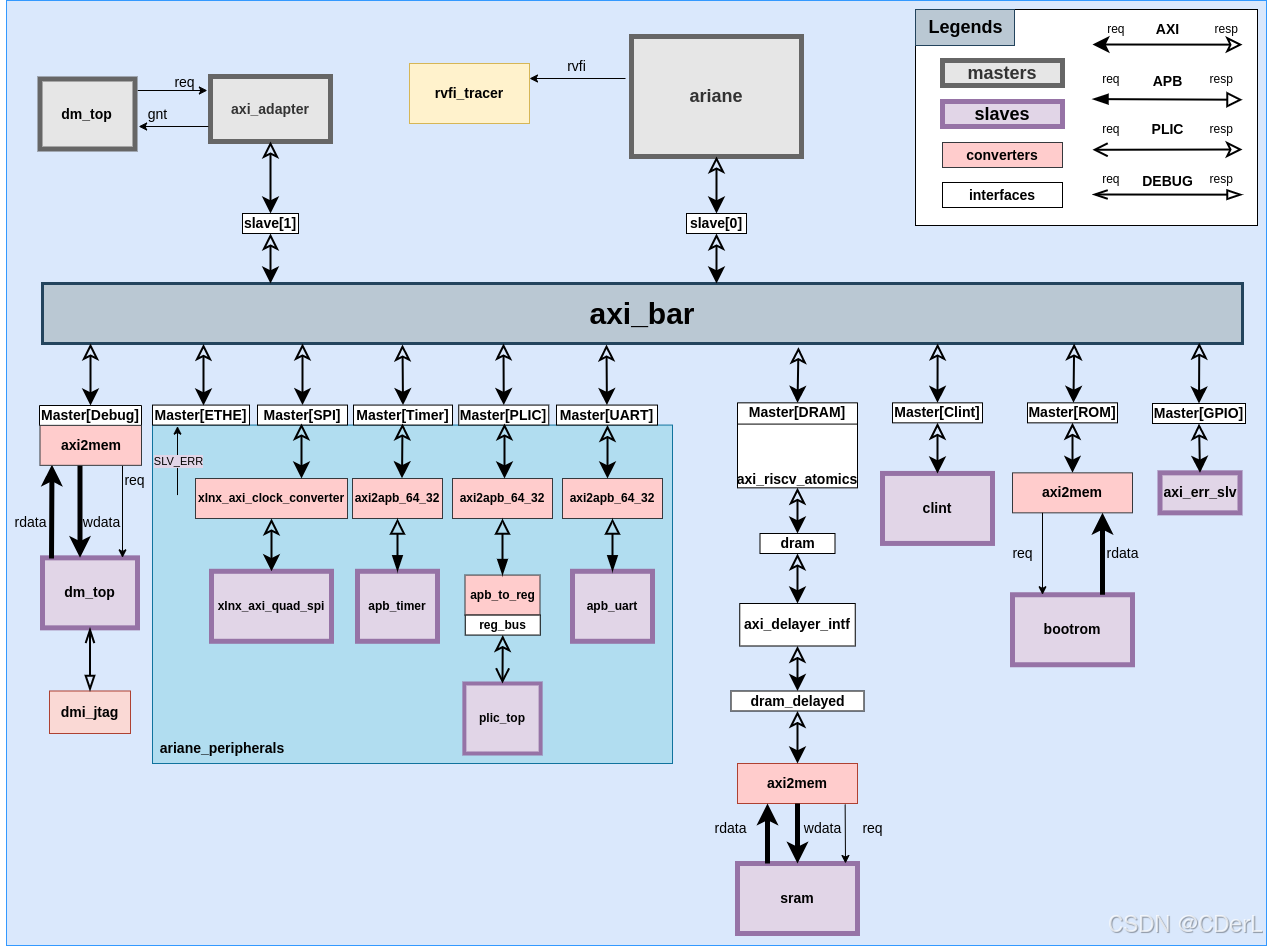

The CVA6 APU describes an Application Processor Unit built around the CVA6.

/home/cva6/corev_apu/tb/ariane_axi_pkg.sv

/home/cva6/corev_apu/tb/axi_intf.sv

/home/cva6/corev_apu/register_interface/src/reg_intf.sv

/home/cva6/corev_apu/tb/ariane_soc_pkg.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_pkg.sv

/home/cva6/corev_apu/tb/ariane_axi_soc_pkg.sv

/home/cva6/corev_apu/src/ariane.sv

/home/cva6/corev_apu/bootrom/bootrom.sv

/home/cva6/corev_apu/clint/axi_lite_interface.sv

/home/cva6/corev_apu/clint/clint.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb_64_32.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb.sv

/home/cva6/corev_apu/fpga/src/axi2apb/src/axi2apb_wrap.sv

/home/cva6/corev_apu/fpga/src/apb_timer/apb_timer.sv

/home/cva6/corev_apu/fpga/src/apb_timer/timer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_ar_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_aw_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_b_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_r_buffer.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_single_slice.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_slice.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_slice_wrap.sv

/home/cva6/corev_apu/fpga/src/axi_slice/src/axi_w_buffer.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_res_tbl.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_amos_alu.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_amos.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_atomics.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_atomics_wrap.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_lrsc.sv

/home/cva6/corev_apu/src/axi_riscv_atomics/src/axi_riscv_lrsc_wrap.sv

/home/cva6/corev_apu/axi_mem_if/src/axi2mem.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_csrs.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_cdc.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_jtag.sv

/home/cva6/corev_apu/riscv-dbg/src/dmi_jtag_tap.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_mem.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_sba.sv

/home/cva6/corev_apu/riscv-dbg/src/dm_top.sv

/home/cva6/corev_apu/rv_plic/rtl/rv_plic_target.sv

/home/cva6/corev_apu/rv_plic/rtl/rv_plic_gateway.sv

/home/cva6/corev_apu/rv_plic/rtl/plic_regmap.sv

/home/cva6/corev_apu/rv_plic/rtl/plic_top.sv

/home/cva6/corev_apu/riscv-dbg/debug_rom/debug_rom.sv

/home/cva6/corev_apu/register_interface/src/apb_to_reg.sv

/home/cva6/corev_apu/tb/ariane_testharness.sv

/home/cva6/corev_apu/tb/ariane_peripherals.sv

/home/cva6/corev_apu/tb/rvfi_tracer.sv

/home/cva6/corev_apu/tb/common/uart.sv

/home/cva6/corev_apu/tb/common/SimDTM.sv

/home/cva6/corev_apu/tb/common/SimJTAG.sv

+define+ corev_apu/tb/common/mock_uart.sv

corev_apu/tb/ariane_tb.cpp

corev_apu/tb/dpi/SimDTM.cc

corev_apu/tb/dpi/SimJTAG.cc

corev_apu/tb/dpi/remote_bitbang.cc

corev_apu/tb/dpi/msim_helper.c

原图链接:点击, 如侵权,请联系删除

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?