1、现状

PCIe 6.0已经废弃了该协议,至于废弃的原因PCIe 6.0 ver0.9版本没有说。

YY一下原因:

(1)把cacheline的内容copy到EP保存,在cacheline内容更新时让host发LN message通知EP更新,这种方式看起来就挺不靠谱。首先就存在延时问题,也就说host那边更新了cacheline,然后发送LN message通知EP更新保存在EP的cacheline的副本,这两个时间之内,两边的cache是不一致的。其次即使不考虑延时问题,LN message丢失了怎么办?如果LN message本身就出了PCIe错误怎么办?

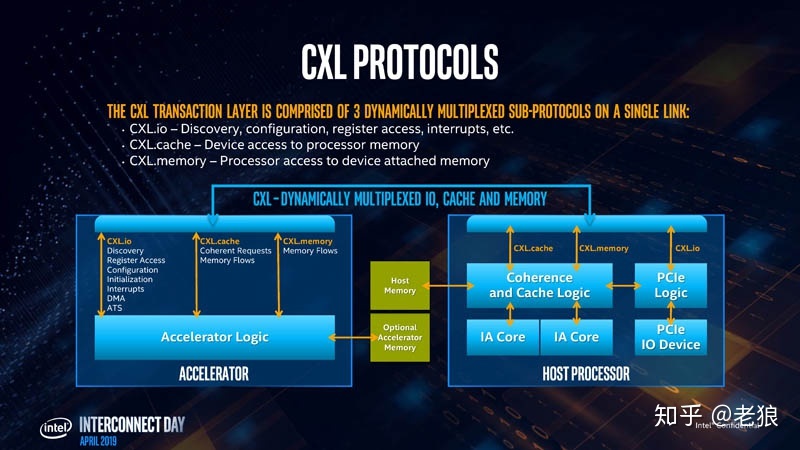

(2)intel的CXL协议有对应CXL.memory,但是CXL把cache一致性问题放在CPU端其实也有点不靠谱。CXL.cache是解决了Device访问host memory的cache问题,让Device访问host memory可以先从cache访问,cache miss后再从memory访问。但是processor访问device内的memory,如果对应的BAR不映射成uncache的,感觉也存在LN一样的问题(没有研究过CXL协议,仅从框图猜测)

2、Lightweight Notification (LN) Protocol

LN协议使得EP可以感知host memory的cacheline的变化。

LN机制利用EP端的Cache来降低系统带宽需求并降低时延。LN协议允许EP注册host memory中的Cacheline,所谓注册Cacheline是指把host memory Cacheline的内容copy一份放到EP本地,并且Cacheline内容改变时,LNC需要通知该EP。

PCIe系统中采用LN协议有以下潜在优点:

3、典型的LN系统

在EP端的LN Requester(LNR)发送LN read/write请求并接受LN message。在host端的LN Completer(LNC)接受LN read/write请求,并在cacheline更新时发送LN message通知LNR。

(1)LN read:LN bit为1的memory read请求。

(2)LN write:LN bit 为1的memory write的请求。

(3)LN completion:LN bit 为1的completion with data请求。

(4)LN message:携带64bit address(cacheline)的Vendor-defined type1 MsgD。

4、LN protocol操作

4、LN protocol操作

LN read

- LNR发出LN read从host memory中copy cacheline的内容到EP本地(LN为1的memory 读)。

- LNC通过LN completion返回cacheline的内容(completion with data),并且记录该LNR已经注册了该cacheline(即该LNR关心该cacheline内容的变化)。

- 当LNC的cacheline的内容发生变化时,LNC使用LN message通知LNR,cacheline的内容更新了。

LN write

- LNR向host memory的cacheline发起LN write,请求写host memory的cacheline(LN为1的memory写请求)。

- LNC记录该LNR已经注册了该cacheline(memory写请求,不用回复completion)。

- 当LNC的cacheline的内容发生变化时,LNC使用LN message通知LNR,cacheline的内容更新了。

5、LN相关的寄存器

(1)针对EP的LN requester extended cap寄存器

(2)针对RootPort的LN system CLS

1003

1003

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?