从二进制到计算机——手把手造八位CPU

为什么是二进制

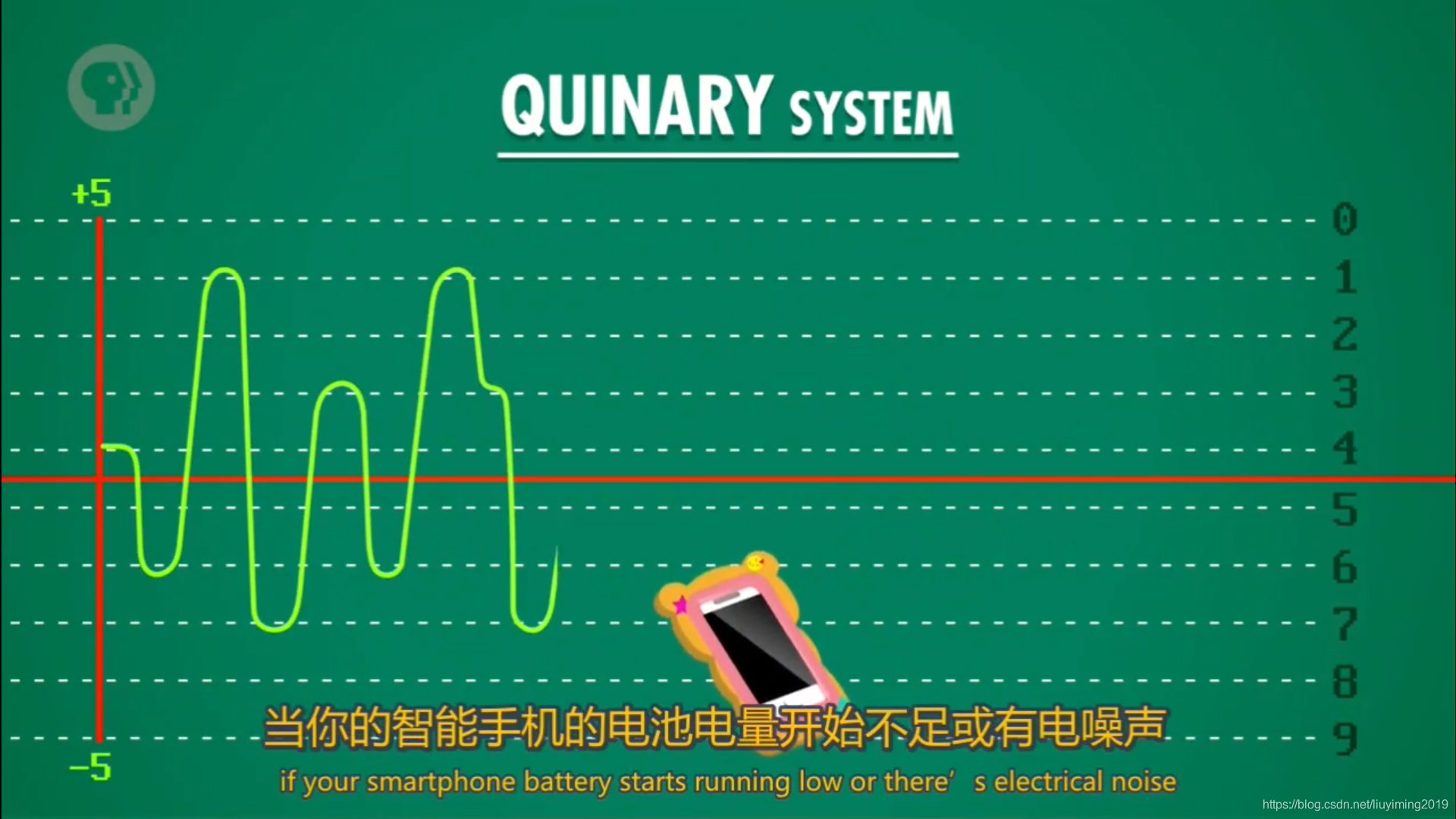

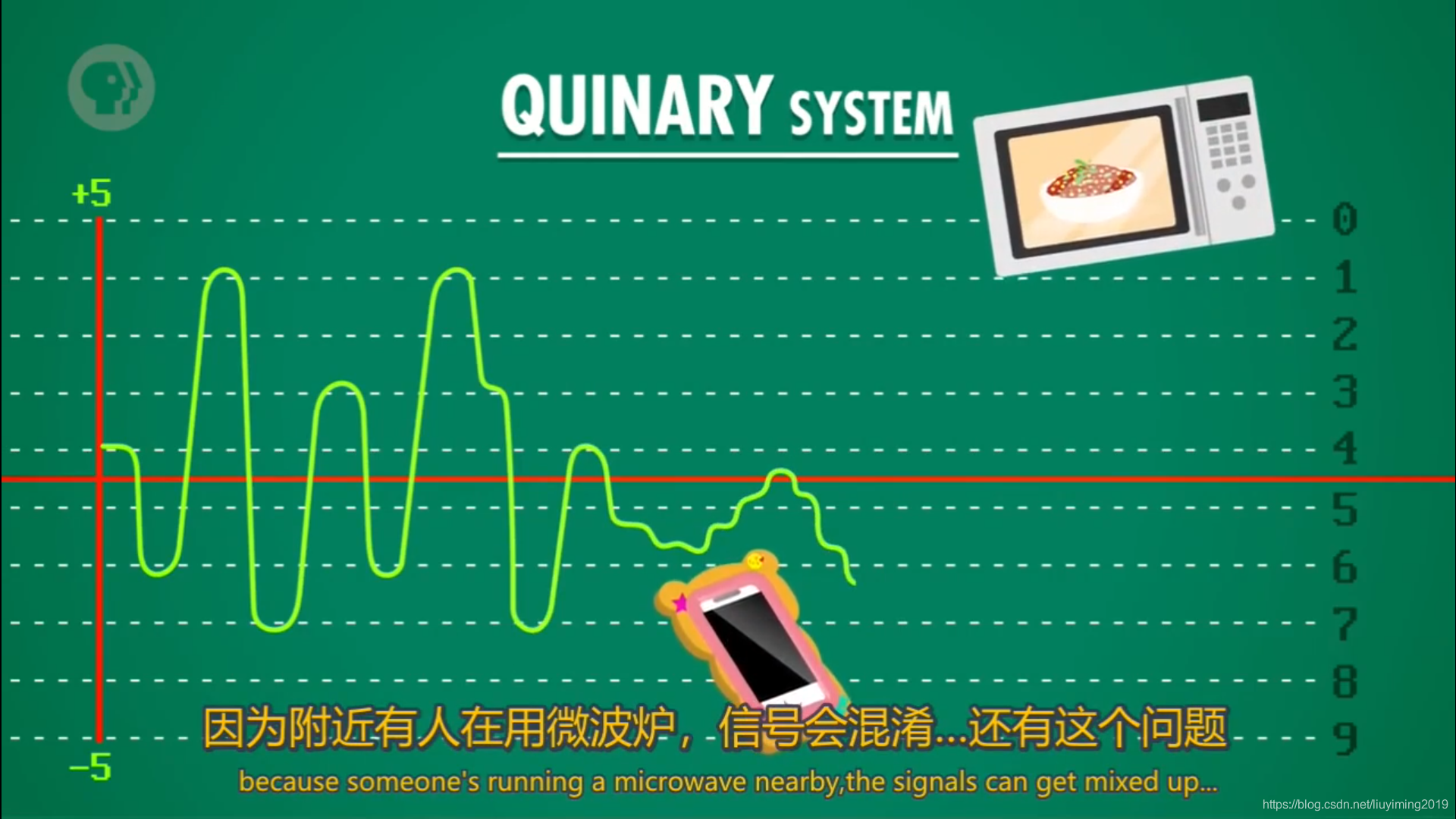

二进制表示准确不混淆

二进制没法表示太多意思,但可以表示开关两种状态,准确表示两个值

"

t

u

r

e

"

"ture"

"ture"和

"

f

a

l

s

e

"

"false"

"false",那么为何不采取其他进制呢,因为当手机电量不足或者周围有电噪声时信号会混淆,并随着上百万次状态变得越来越糟。把信号放在相对较远的地方——

0

0

0和

1

1

1可以有效解决这个问题

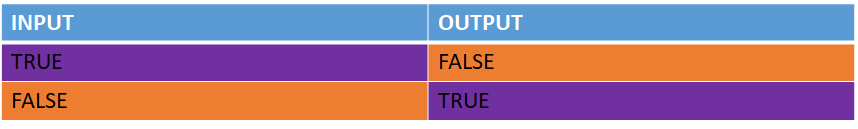

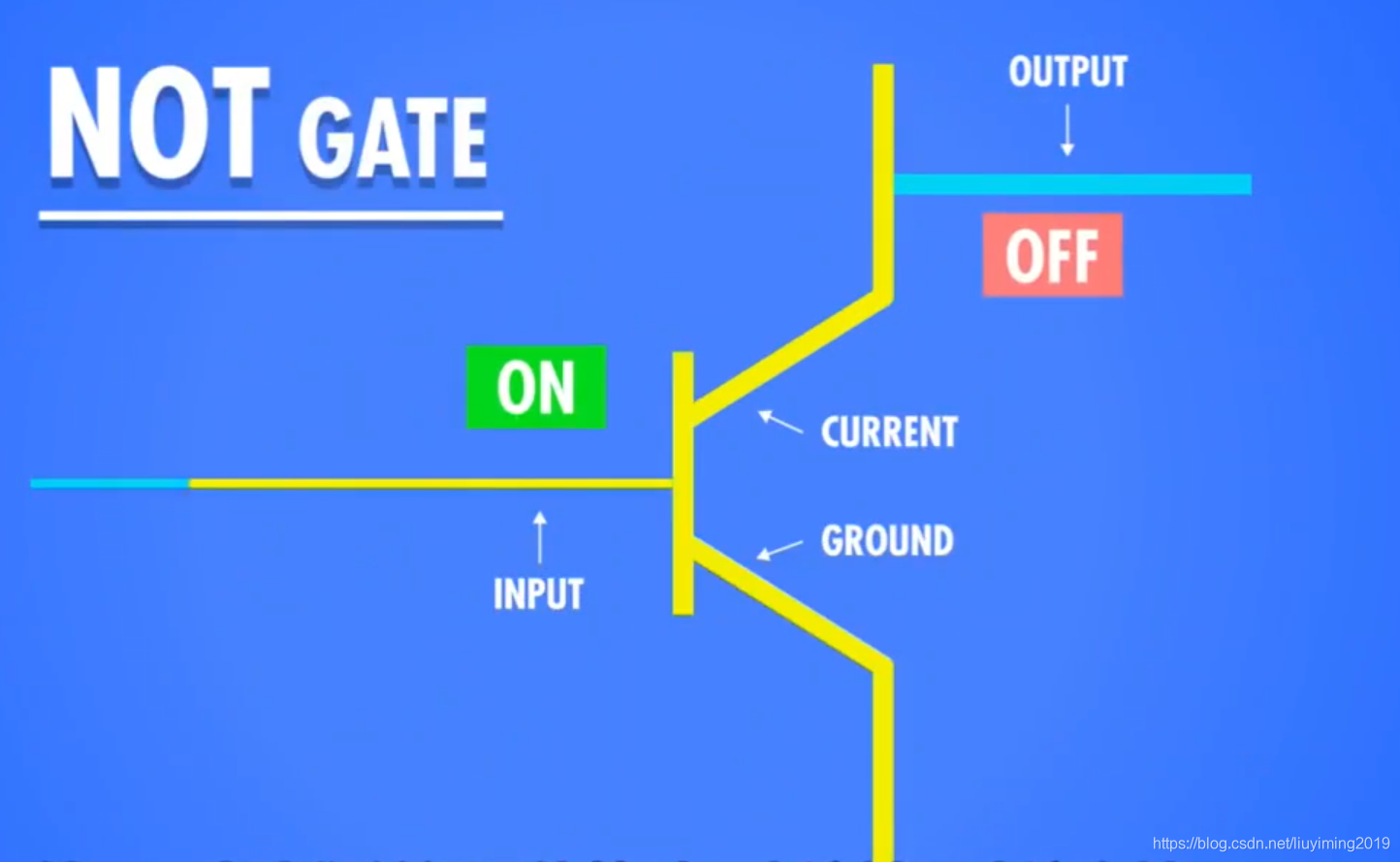

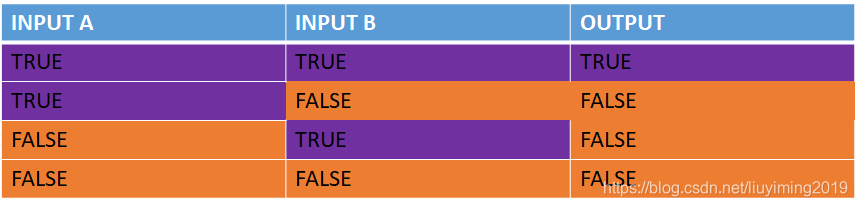

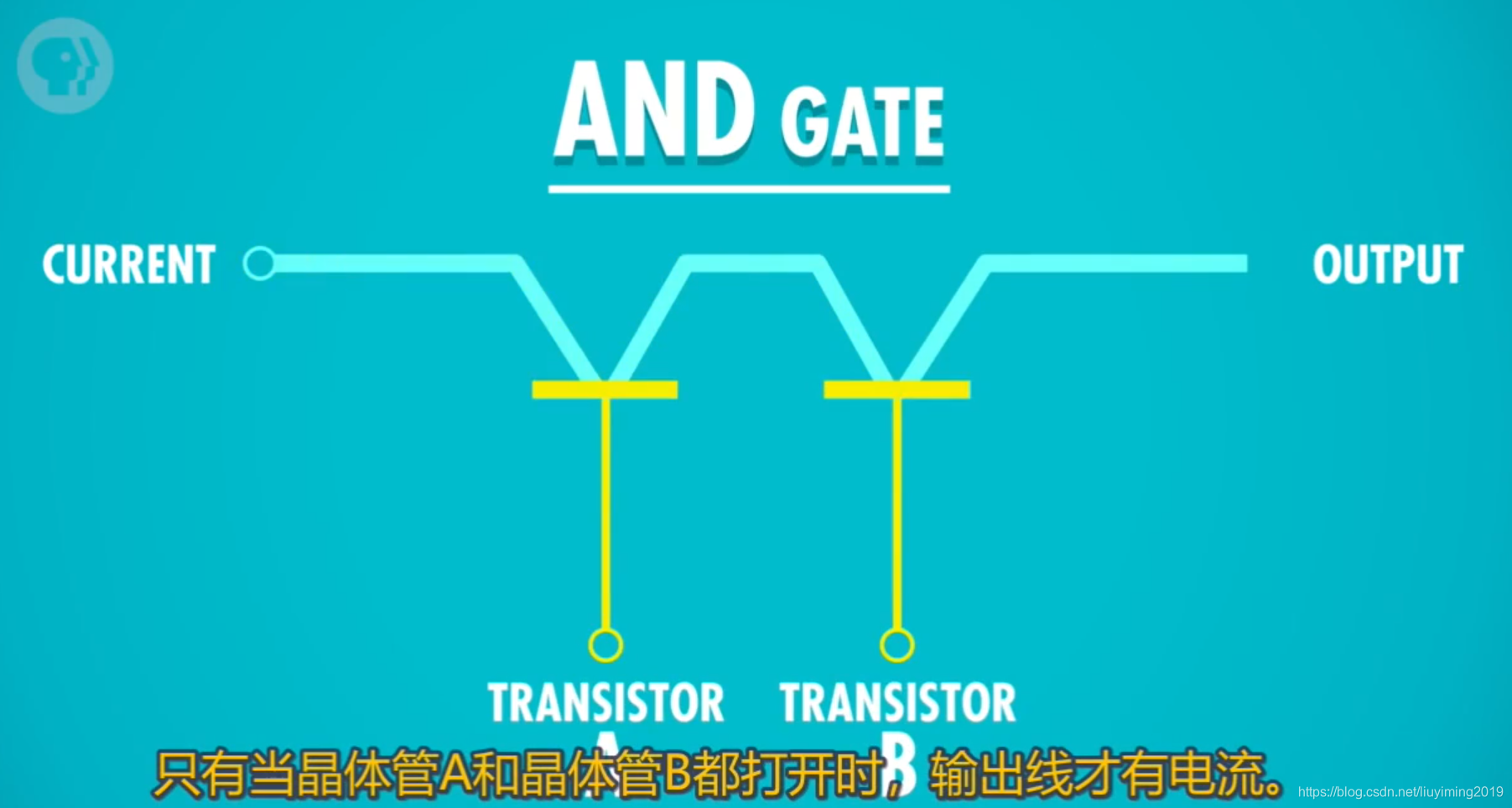

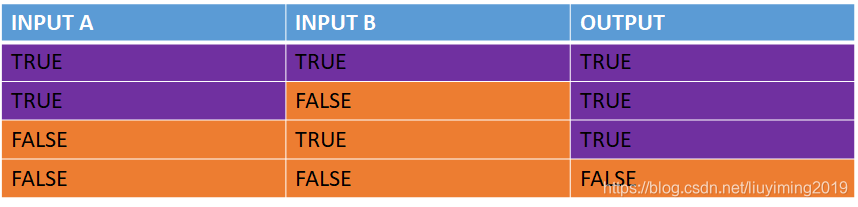

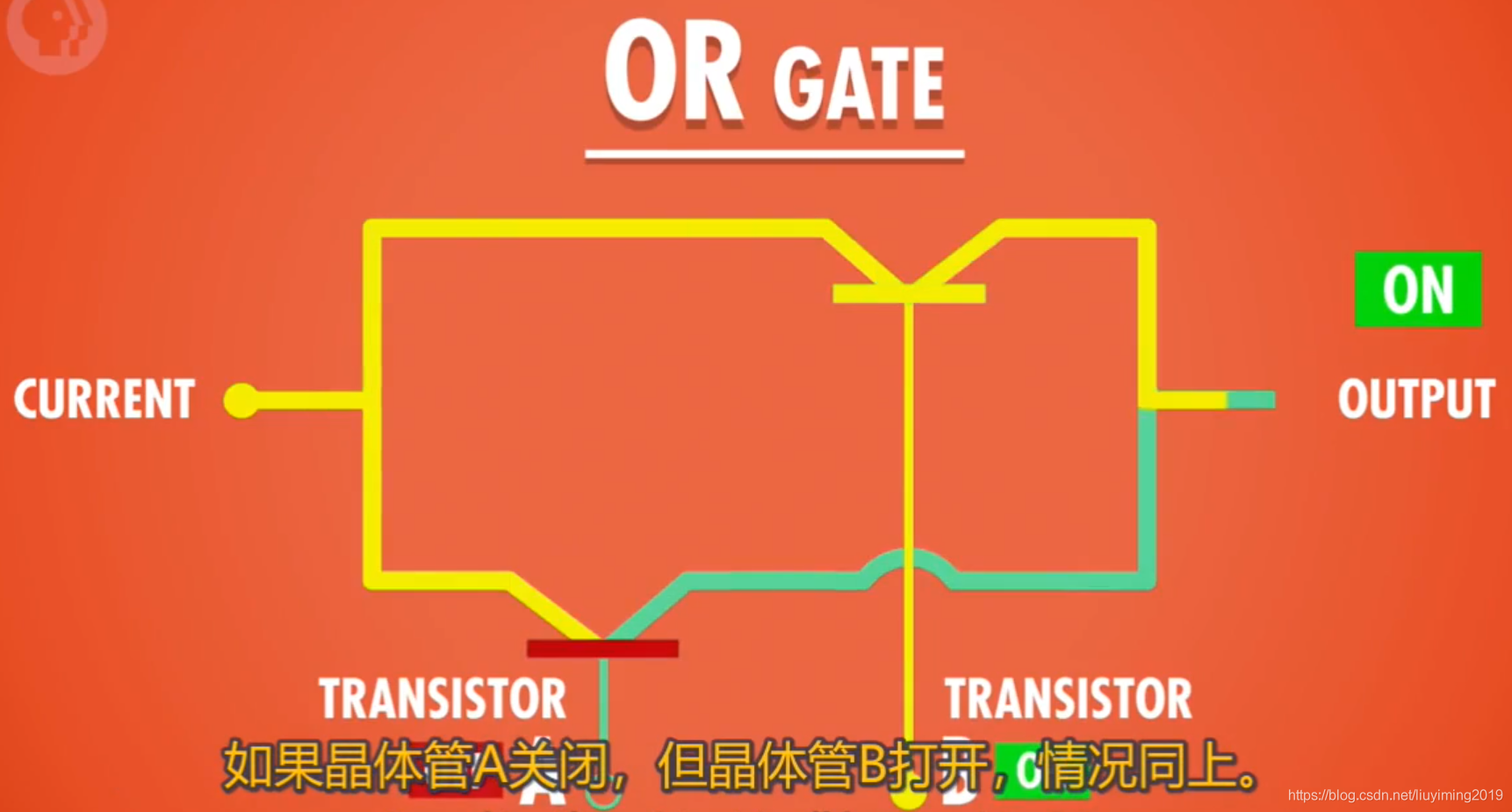

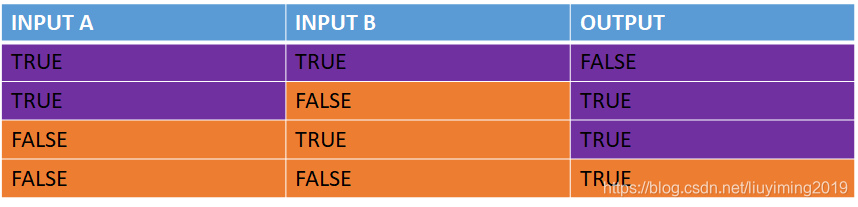

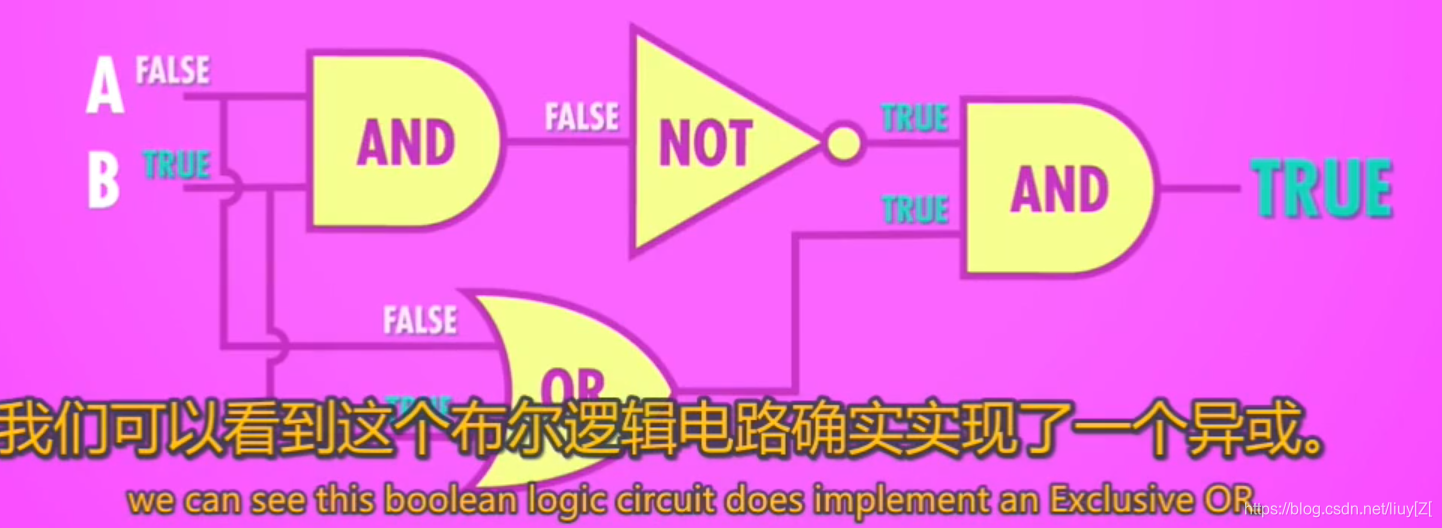

二进制成熟的数学分支——布尔代数和逻辑门

n o t not not(非)

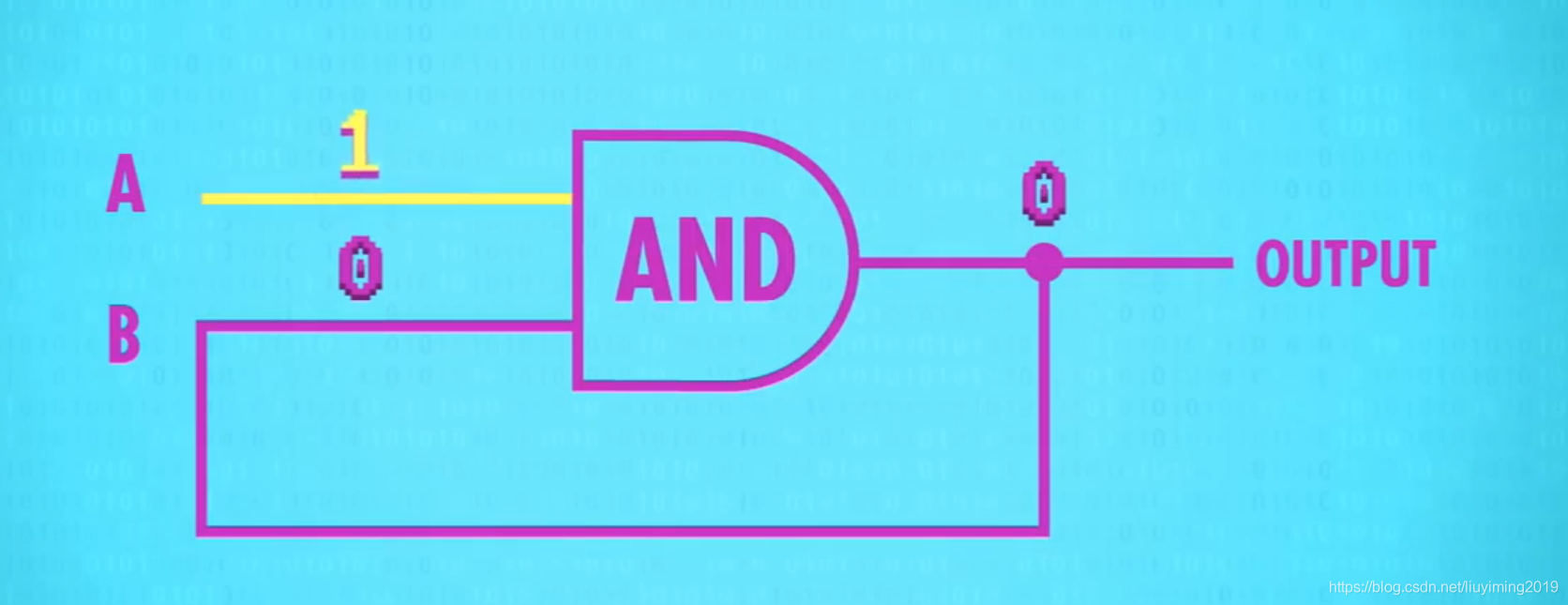

a n d and and(与)

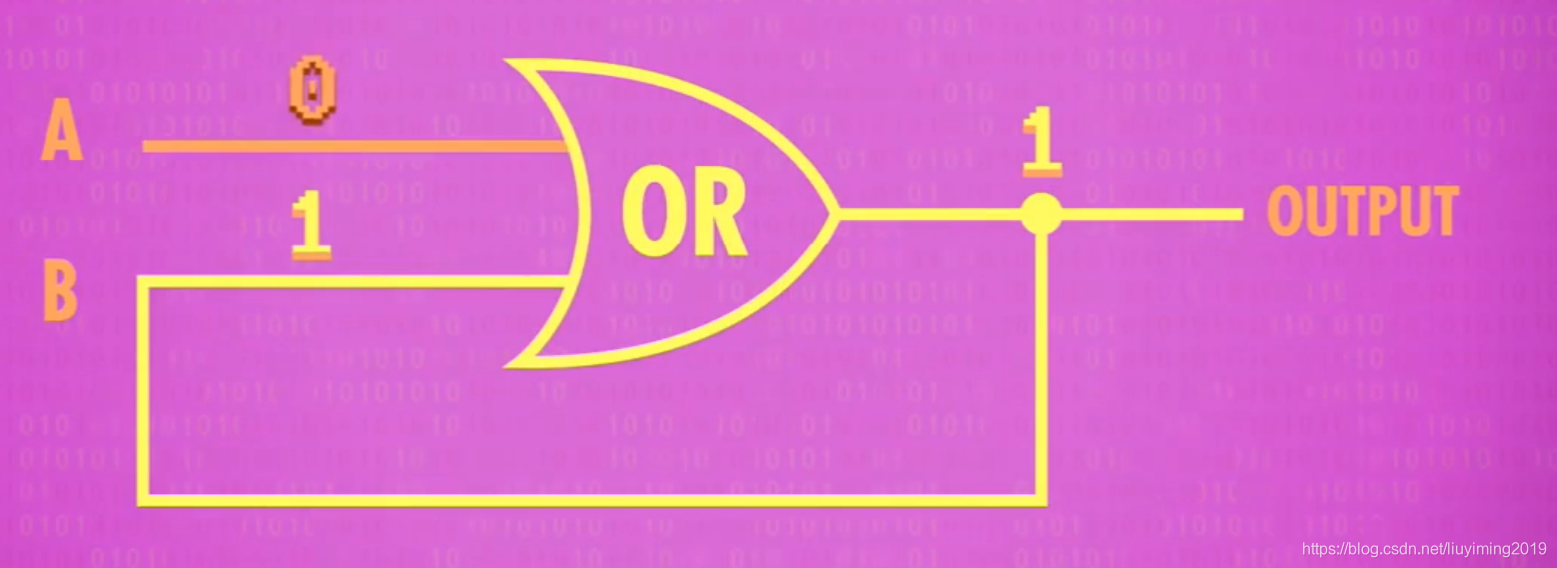

o r or or(或)

X O R XOR XOR(异或)

我们可以设置一种对应关系,用多位二进制表示指定字符,如

A

S

C

I

I

ASCII

ASCII:

我们可以设置一种对应关系,用多位二进制表示指定字符,如

A

S

C

I

I

ASCII

ASCII:

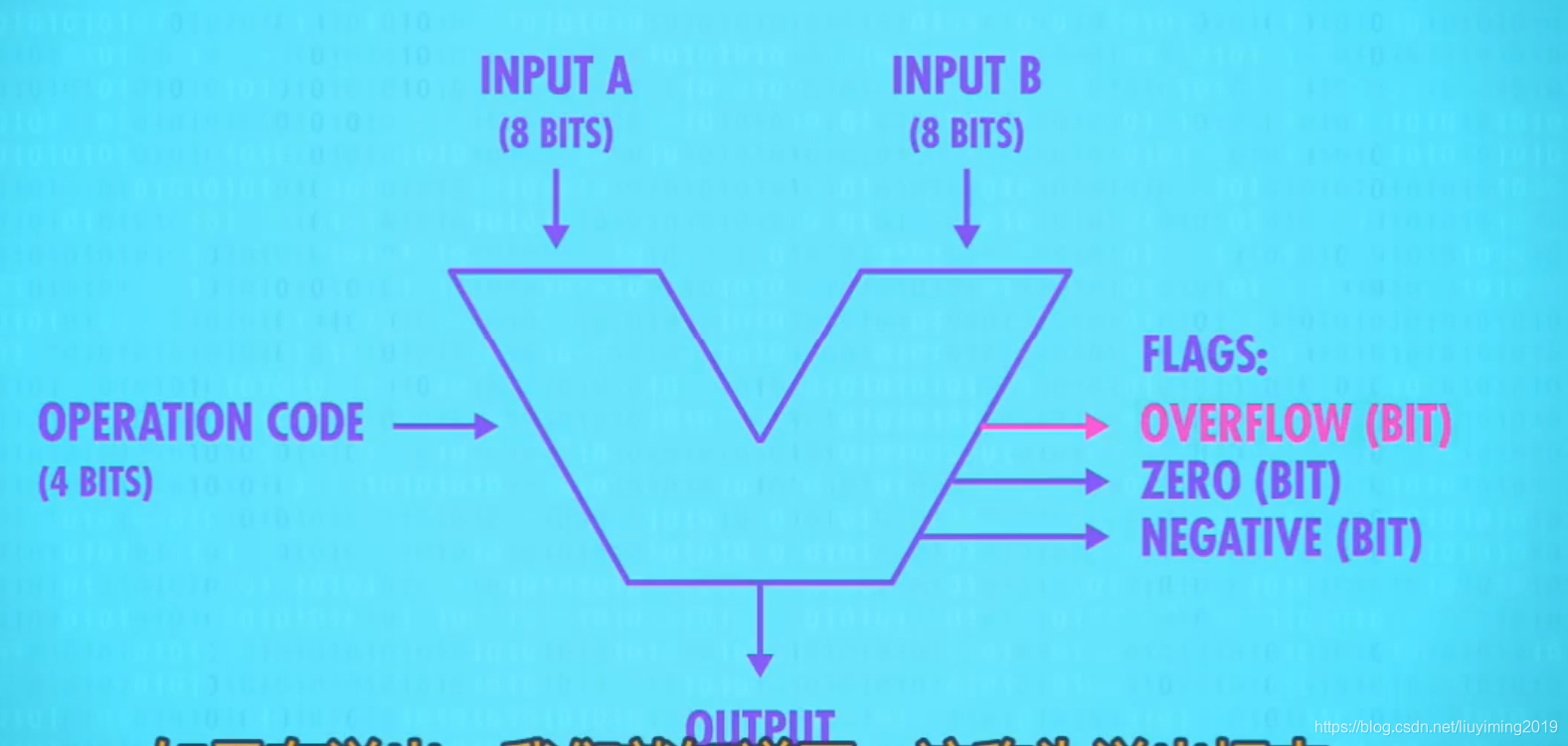

算数逻辑单元(ALU)

A L U ALU ALU是执行 A r i t h m e t i c Arithmetic Arithmetic和 L o g i c Logic Logic的单元,是表示和存储数字是计算机的一个重要功能,但真正的目标是计算,或者以结构和有目的的操作数字,如两个数相加,这些操作由计算机的"算数逻辑单元"处理。

算数单元讲解

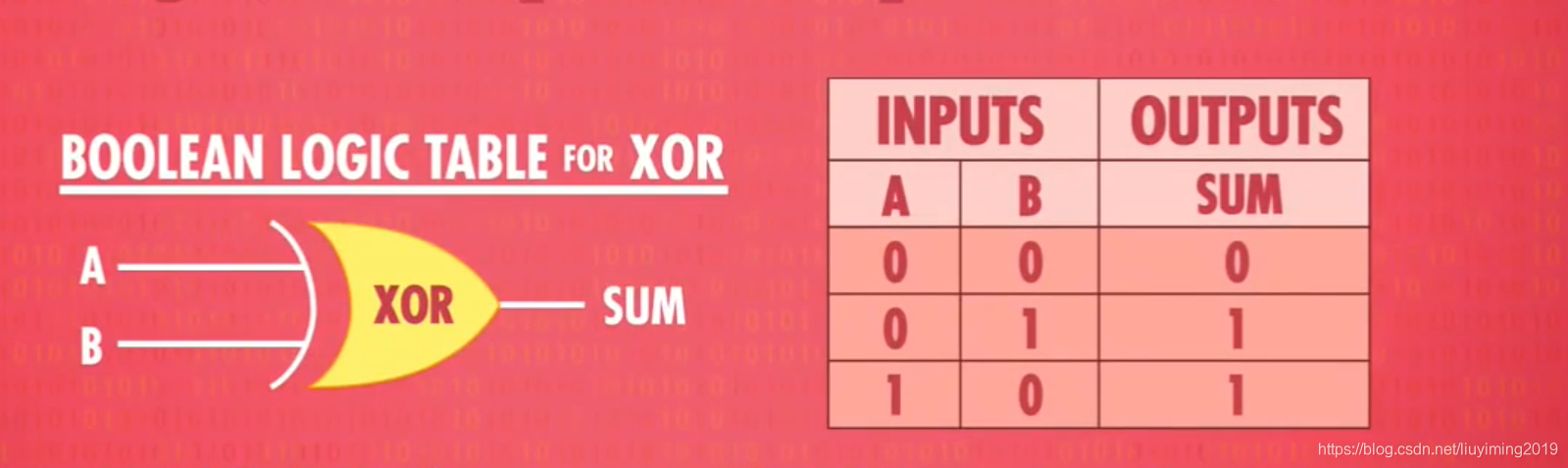

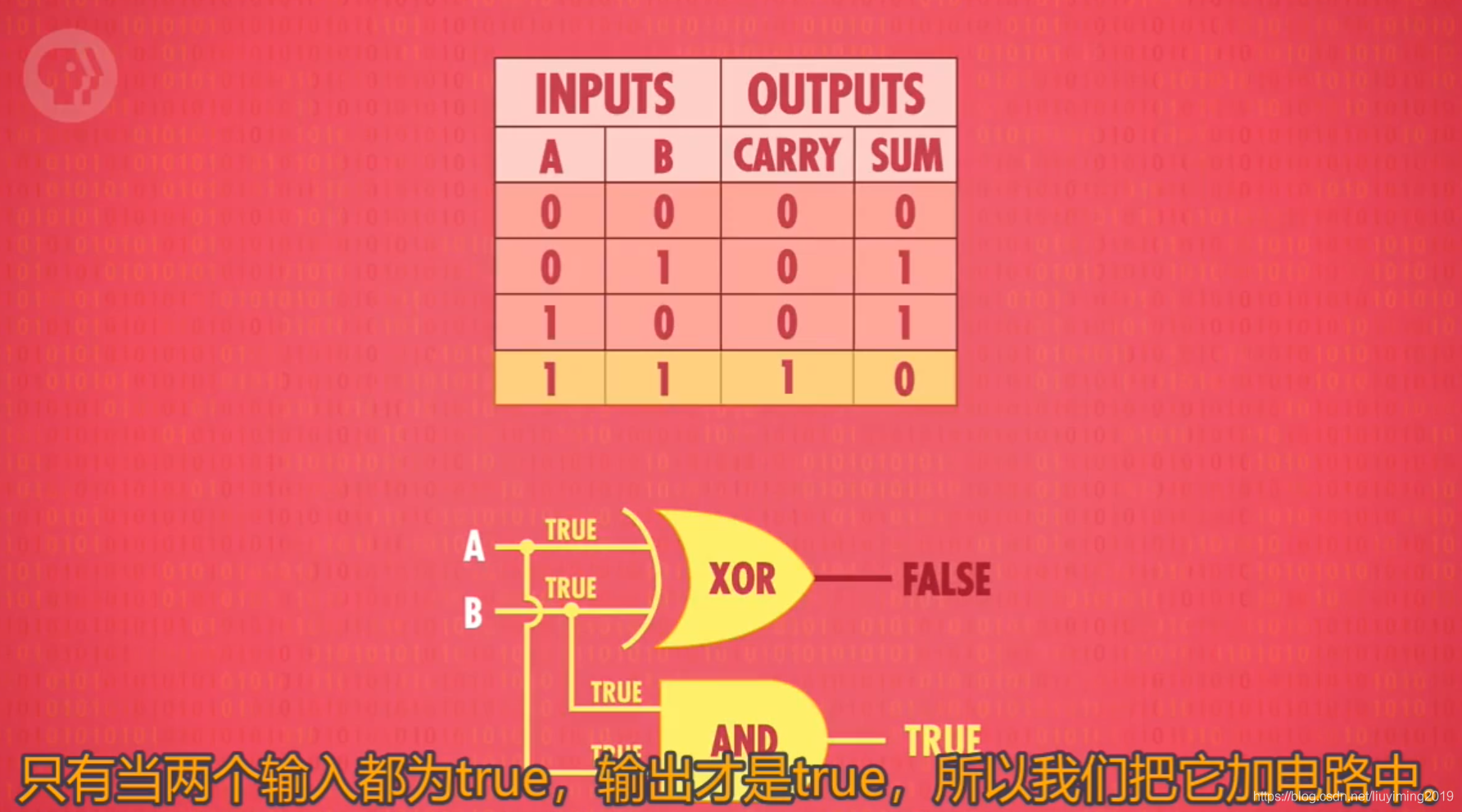

半加器

无进位(这不是半加器)

有进位(即半加器)

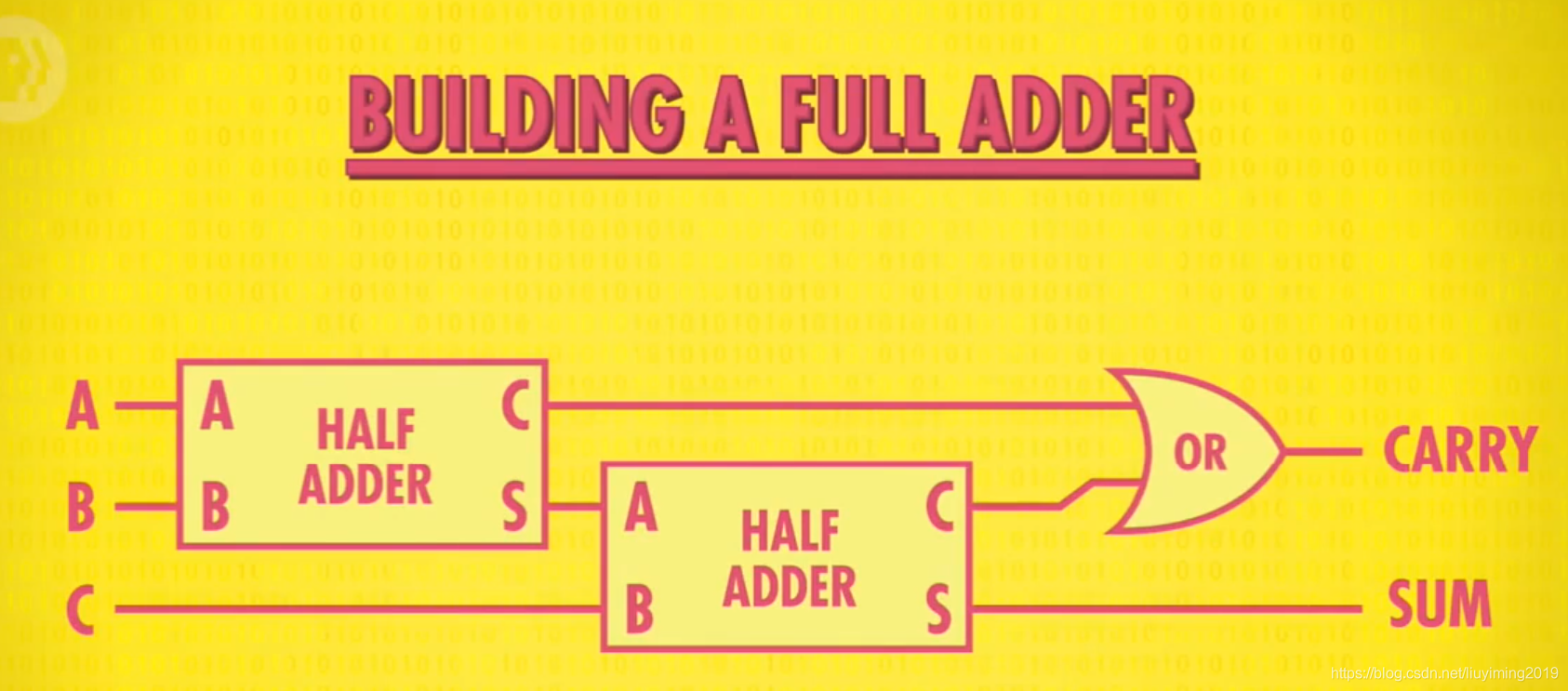

全加器

- 全加器可用两个半加器和一个“或“门组成。这个得记住

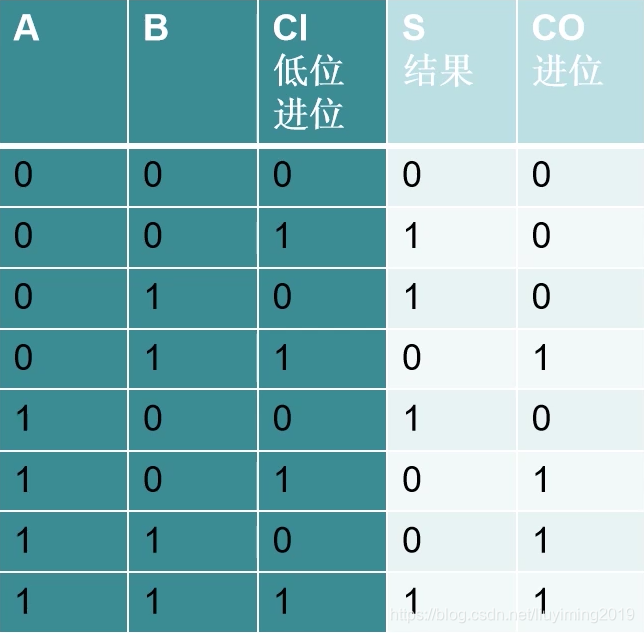

- 或者用真值表现推:

S ( 和 ) = ( A ′ B ′ C I ′ + A ′ B ∗ C I + A B ′ C I + A B C I ′ ) ′ C O ( 进 位 ) = ( A ′ B ′ + B ′ C I ′ + A ′ C I ′ ) ′ S(和)=(A^{'}B^{'}CI^{'}+A^{'}B*CI+AB^{'}CI+ABCI^{'})^{'}\\CO(进位)=(A^{'}B^{'}+B^{'}CI^{'}+A^{'}CI^{'})^{'} S(和)=(A′B′CI′+A′B∗CI+AB′CI+ABCI′)′CO(进位)=(A′B′+B′CI′+A′CI′)′

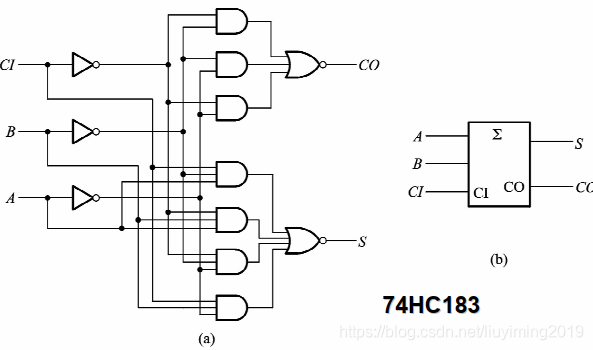

多位加法器

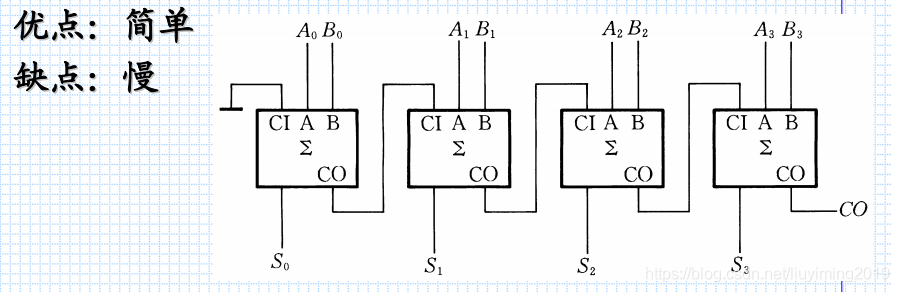

串行进位加法器

(

C

I

)

i

=

(

C

O

)

i

−

1

S

i

=

A

i

⊕

B

i

⊕

(

C

I

)

i

(

C

O

)

i

=

A

i

B

i

+

(

A

i

+

B

i

)

(

C

I

)

i

(CI)_i=(CO)_{i-1}\\S_i=A_i \oplus B_i \oplus(CI)_i \\(CO)_i=A_iB_i+(A_i+B_i)(CI)_i

(CI)i=(CO)i−1Si=Ai⊕Bi⊕(CI)i(CO)i=AiBi+(Ai+Bi)(CI)i

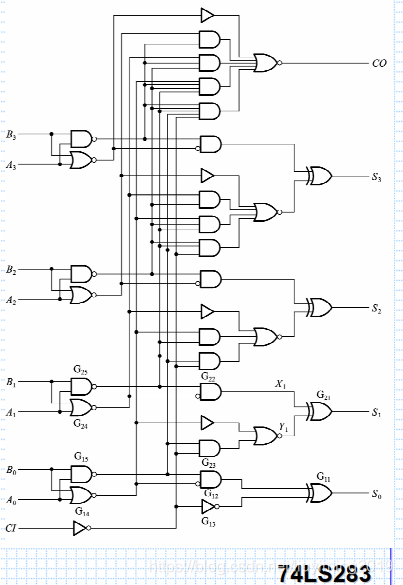

超前进位加法器

- 串行加法器的不足

我们发现串行进位加法器只有前一全加器输出后一全加器才能计算,这在实际应用中会导致延时。 - 超前进位加法器原理:第

i

i

i位的进位输入信号是两个加数第

i

i

i位以前各位

(

0

∼

j

−

1

)

(0\sim j-1)

(0∼j−1)的函数,可在相加前确定

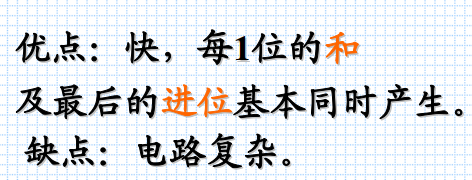

溢出

如果是八位行波进位加法器,注意最后是有进位的输出,如果第九位有进位,就表示两个数的总和太大而超过了

8

8

8位,这称为溢出,溢出通常会导致错误和意外结果。

如果是八位行波进位加法器,注意最后是有进位的输出,如果第九位有进位,就表示两个数的总和太大而超过了

8

8

8位,这称为溢出,溢出通常会导致错误和意外结果。

ALU的减法乘法除法

减法同理可由电路得出。乘法是多个加法的和,或者乘除法也可以设置特有的逻辑单元,具体操作类似于加法

逻辑单元讲解

设置

1

1

1为与门

设置

0

0

0为或门

A L U ALU ALU封装

做好之后我们将其封装起来,通常用

V

V

V表示

左上方近正方体是与或电路,右下方平躺长方体是加减电路

故封装后的结果为

故封装后的结果为

寄存器和内存

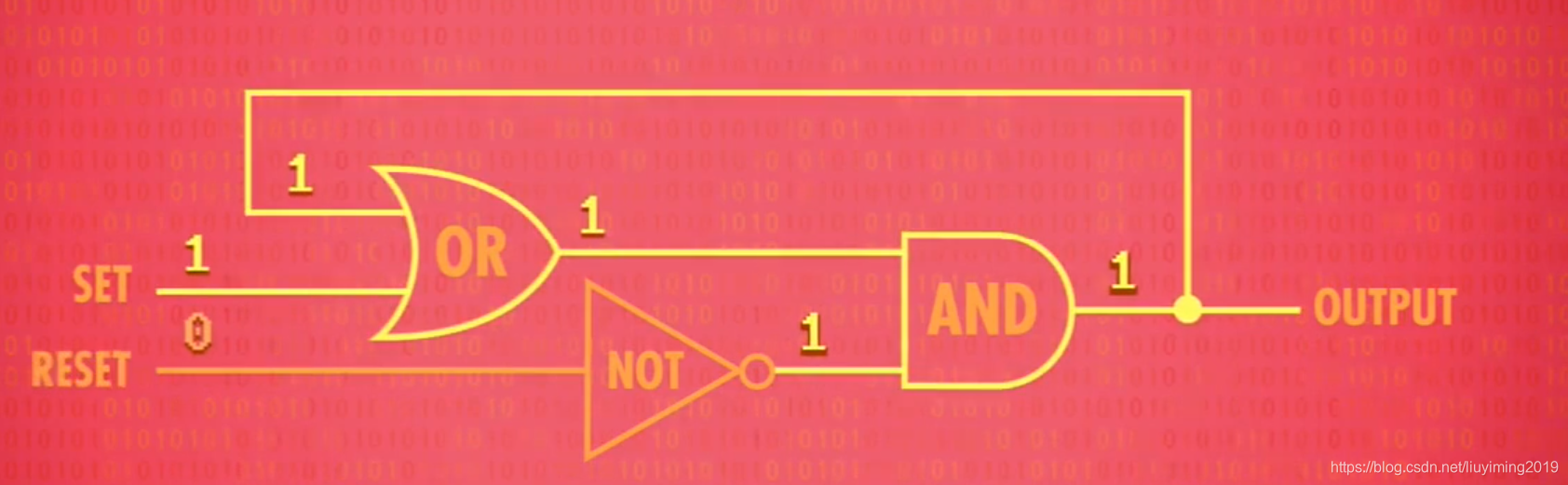

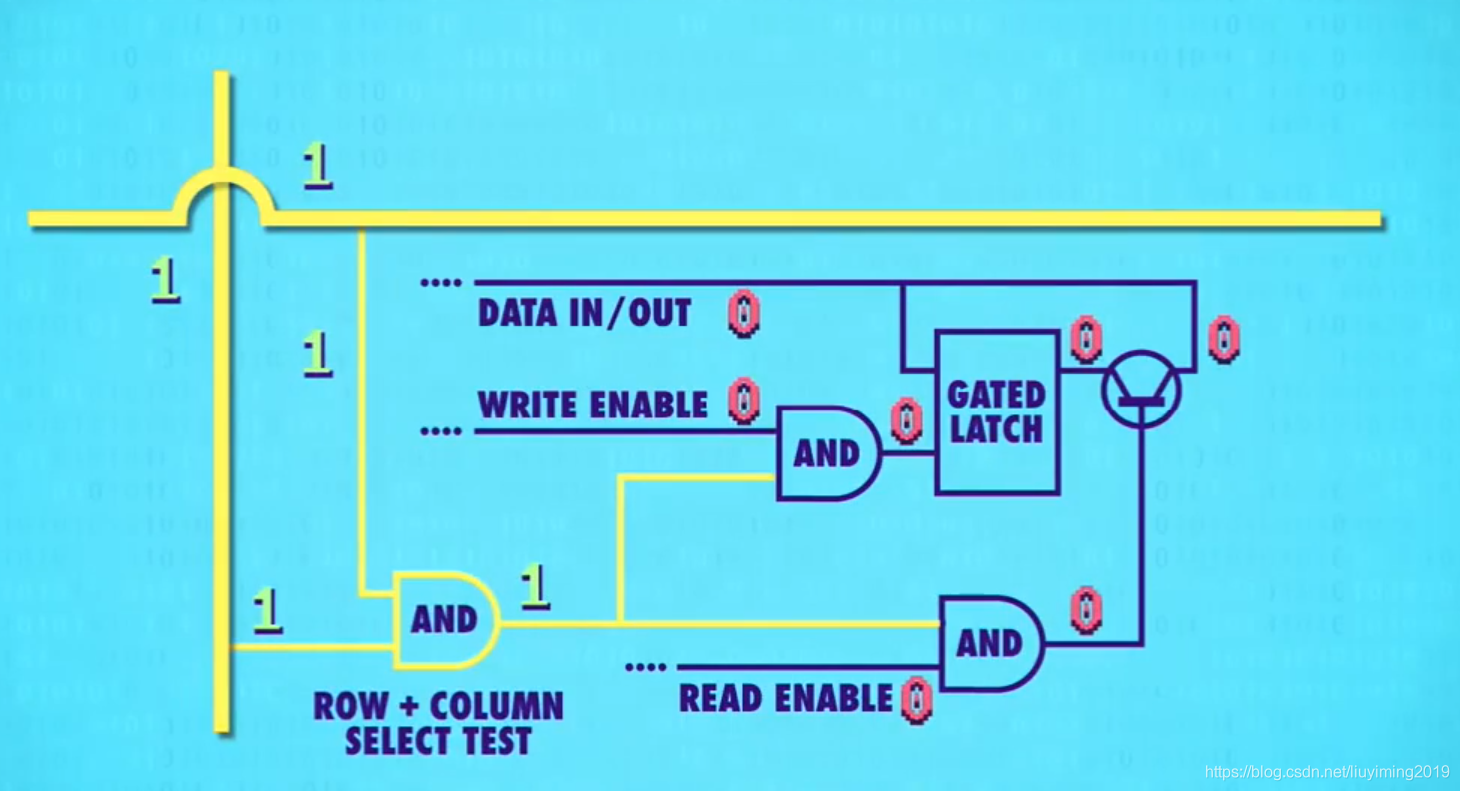

"AND-OR"锁存器,

接下来我们以建立一个可以存储单个 b i t bit bit的电路,之后再扩大成为我们自己的内存模块,先看下面几个电路:

- A开始输1后永久为1

- A输0后永久为0

- 为了进行有效存储,创造出"AND-OR"锁存器,他有两个输入,

s

e

t

set

set输

1

1

1置1,

r

e

s

e

t

reset

reset输

1

1

1置

0

0

0,如果输入输出都是

0

0

0则会保持当初存入的内容

这样记住了一个比特的信息,由于他**锁定了一个特定的值并保持状态,所以称之为锁存器**

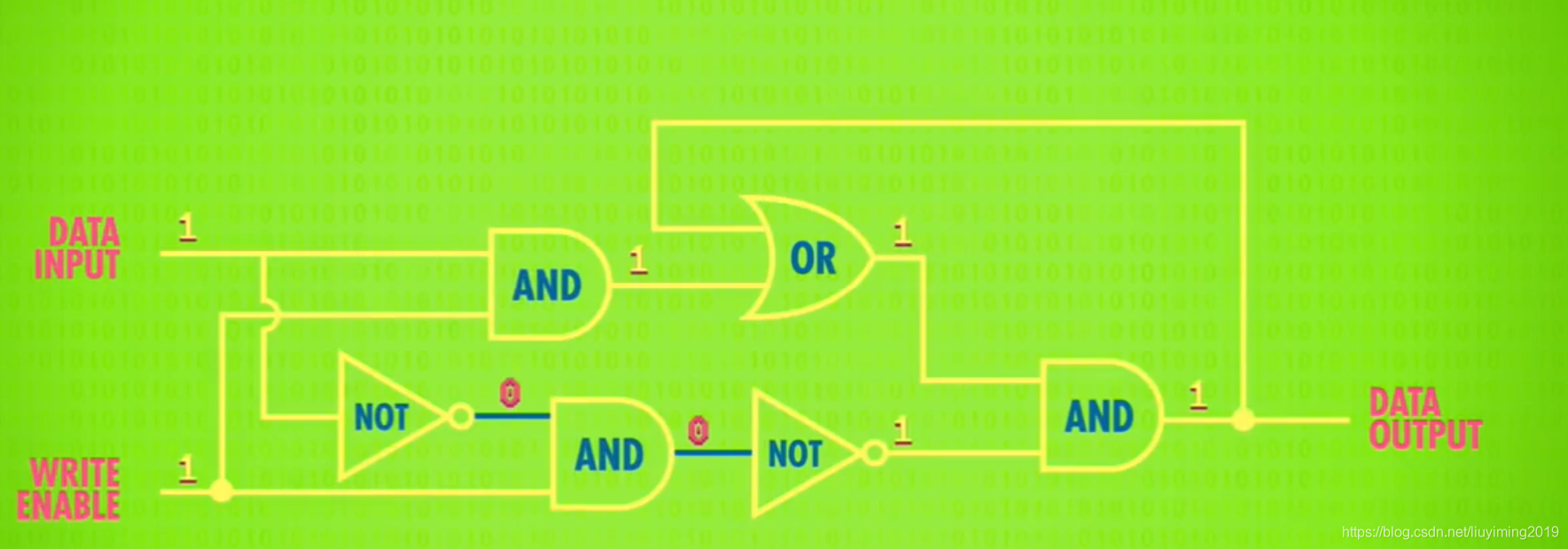

门锁

两条线设值有点难以理解,所以我们修改一下电路,用一条线输入,另一条线设置“允许写入权限”,由于可以打开和关闭,我们称之为门锁。

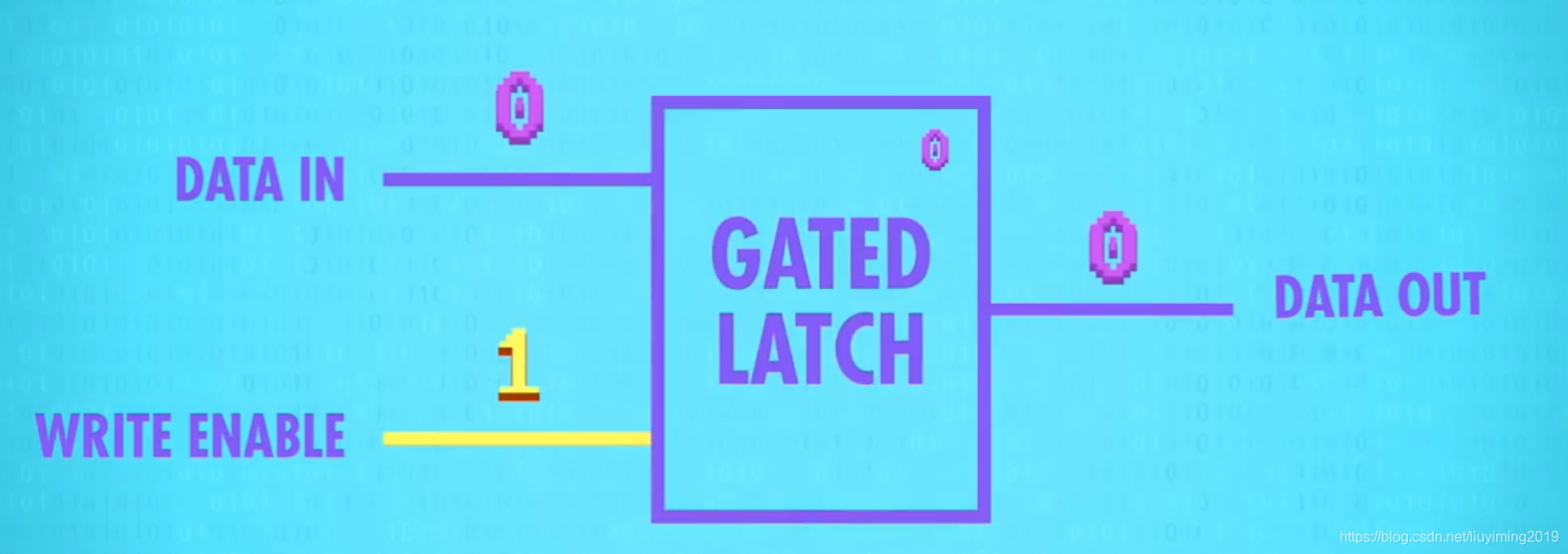

封装带门锁的锁存器

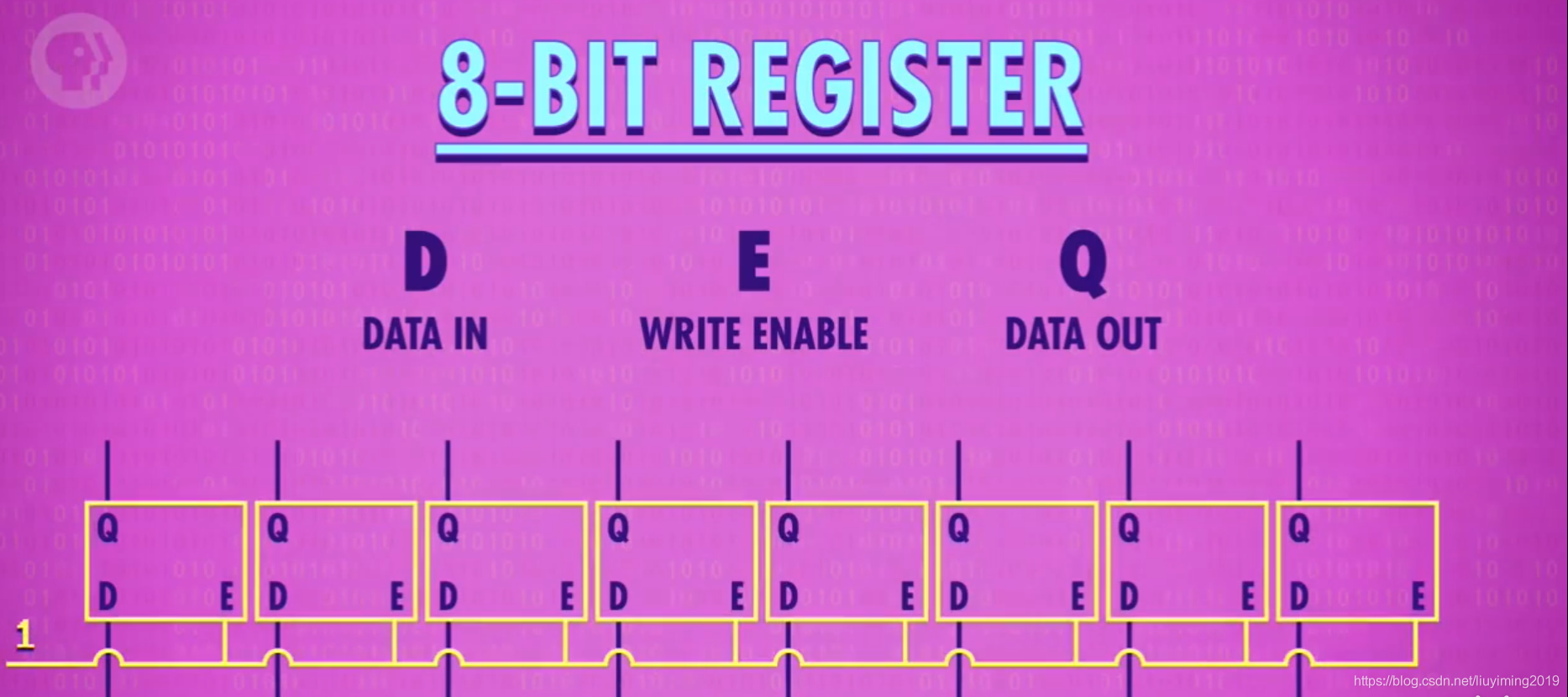

寄存器

像这样一组的锁存器称为寄存器,它能存储一个数字,寄存器能存多少

b

i

t

bit

bit叫位宽,写入前,我们用一根连接到所有启用输入的单线来实现这一点,将其设置为

1

1

1。

这样就存入了一个八位的数字10110101!!!

这样就存入了一个八位的数字10110101!!!

寄存器改进——矩阵放置

按原本的放置方式,64位寄存器,可能需要129根线,存256位要513根线,解决方式是一个矩阵

只有行线列线同时为1才能导通。

只有行线列线同时为1才能导通。

此时256位的数据只需38根线即可。如果这个数据存储在8行12列的话,12=1100,8=1000,所以刚刚用的锁存器地址可以写成11001000

此时256位的数据只需38根线即可。如果这个数据存储在8行12列的话,12=1100,8=1000,所以刚刚用的锁存器地址可以写成11001000

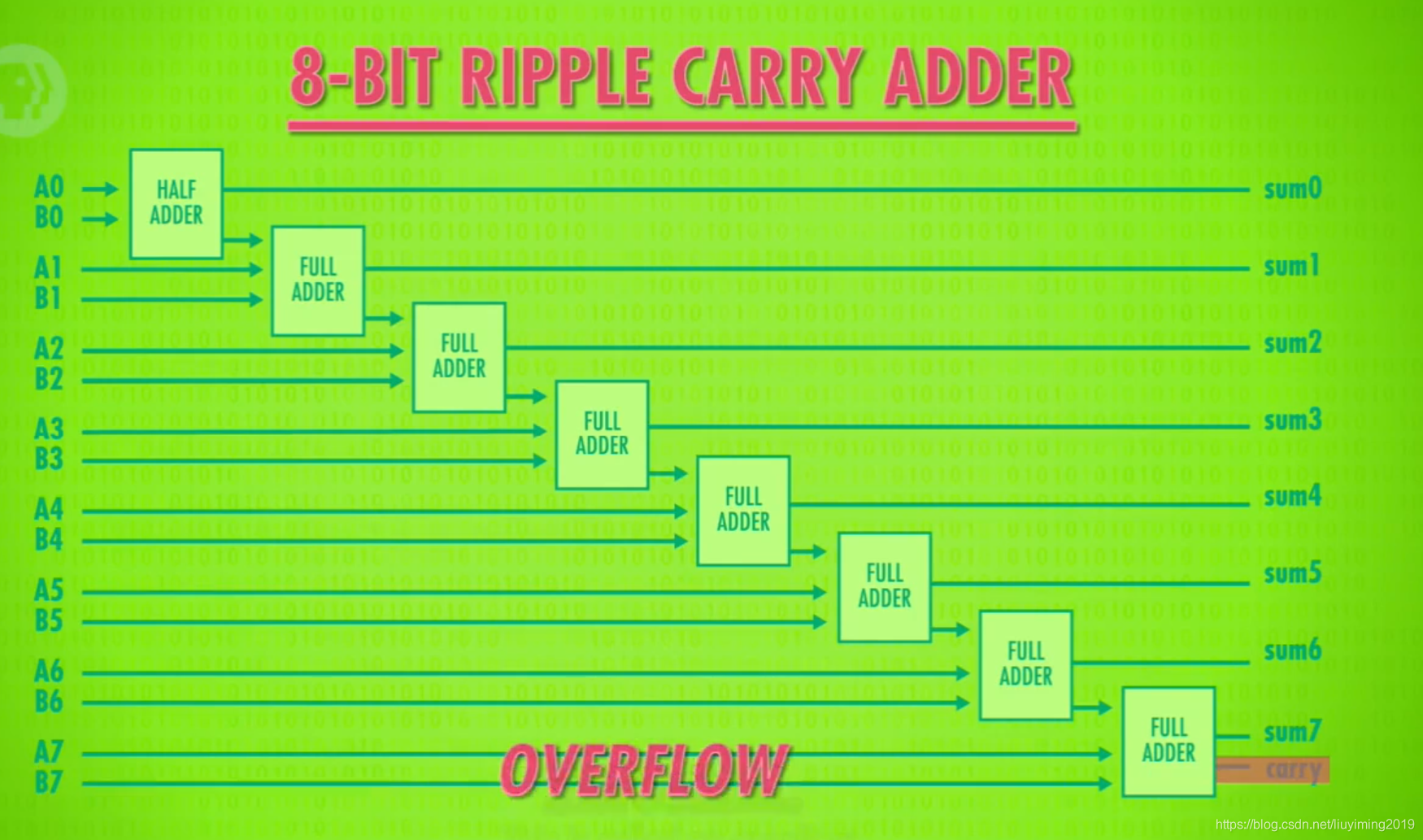

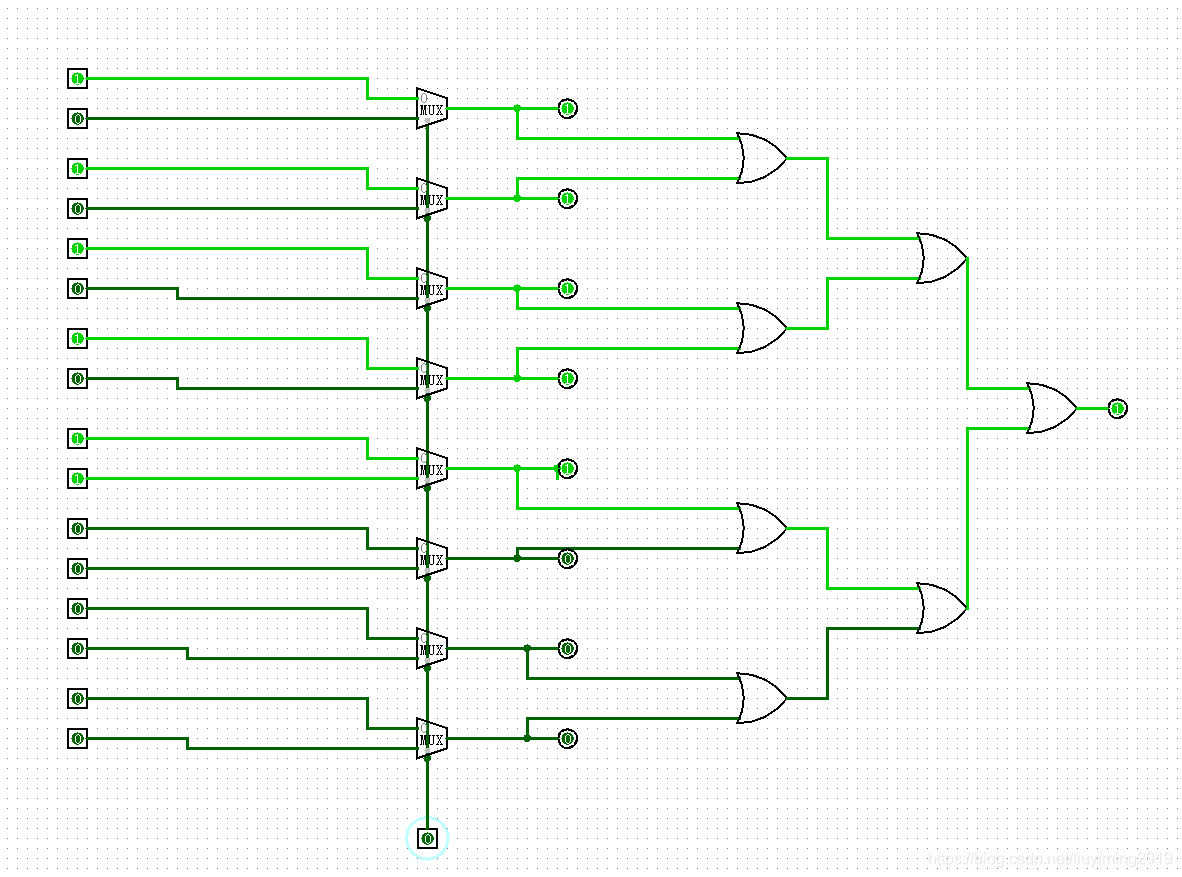

多路复用器

为将地址转换为正确的行或列的内容而用到

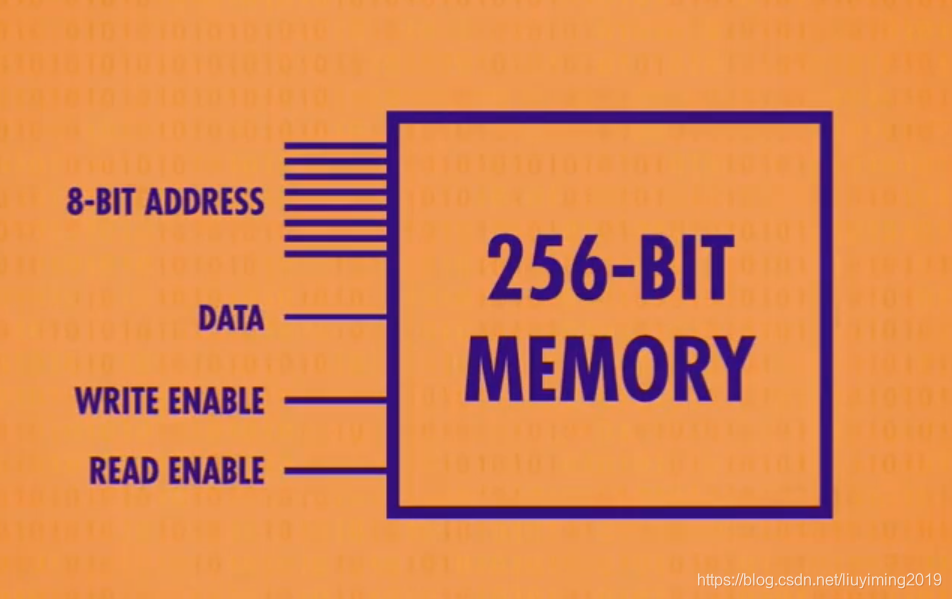

封装

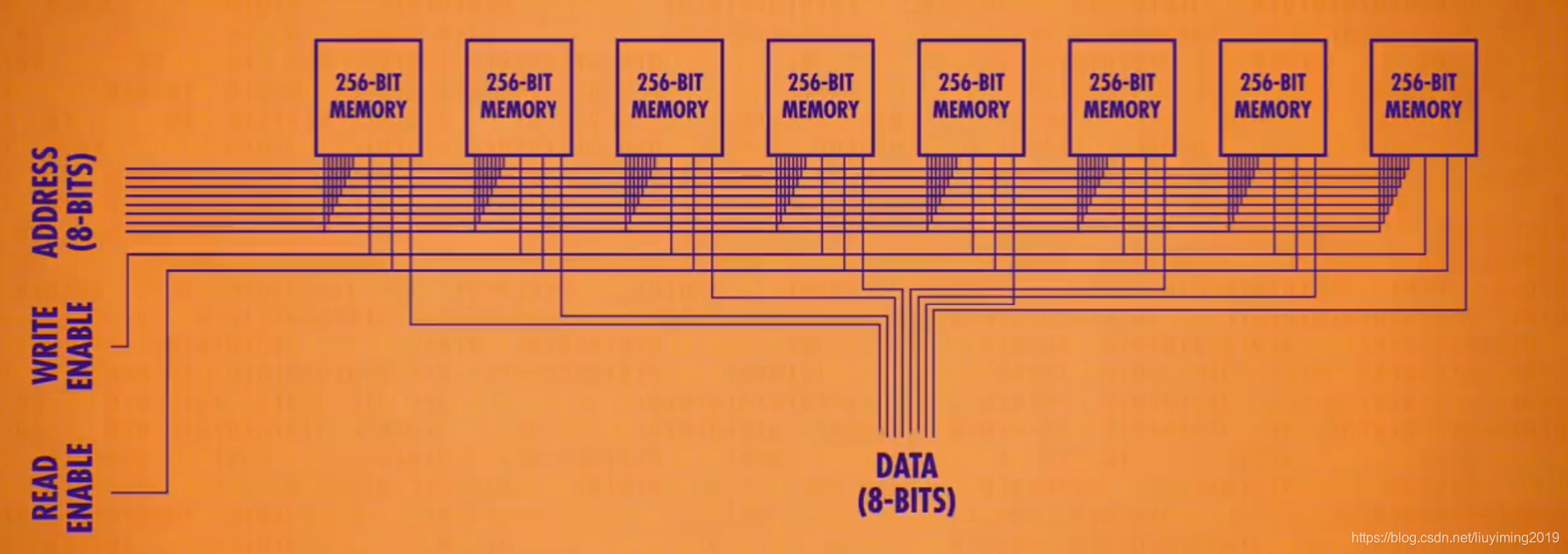

要存储一个数字,要输入八位的地址,一条写入线,一条线控制可写,一条线控制可读。

这样排成一行,则一次可存储一个八位数字,即一个字节。我们同时给8个256位内存同样的地址,每个同样的地址都得到一个数,如把11111111存入8行12列,只需地址输入11001000,允许写入,在对应的数据线上输对应的数字即可。

这样排成一行,则一次可存储一个八位数字,即一个字节。我们同时给8个256位内存同样的地址,每个同样的地址都得到一个数,如把11111111存入8行12列,只需地址输入11001000,允许写入,在对应的数据线上输对应的数字即可。

##

R

A

M

RAM

RAM

##

R

A

M

RAM

RAM

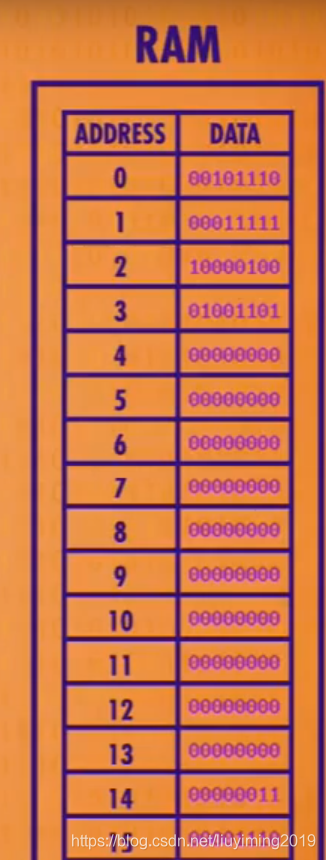

这个内存的重要特性是随时以随机顺序访问内存位置,因此叫随机存取存储器。

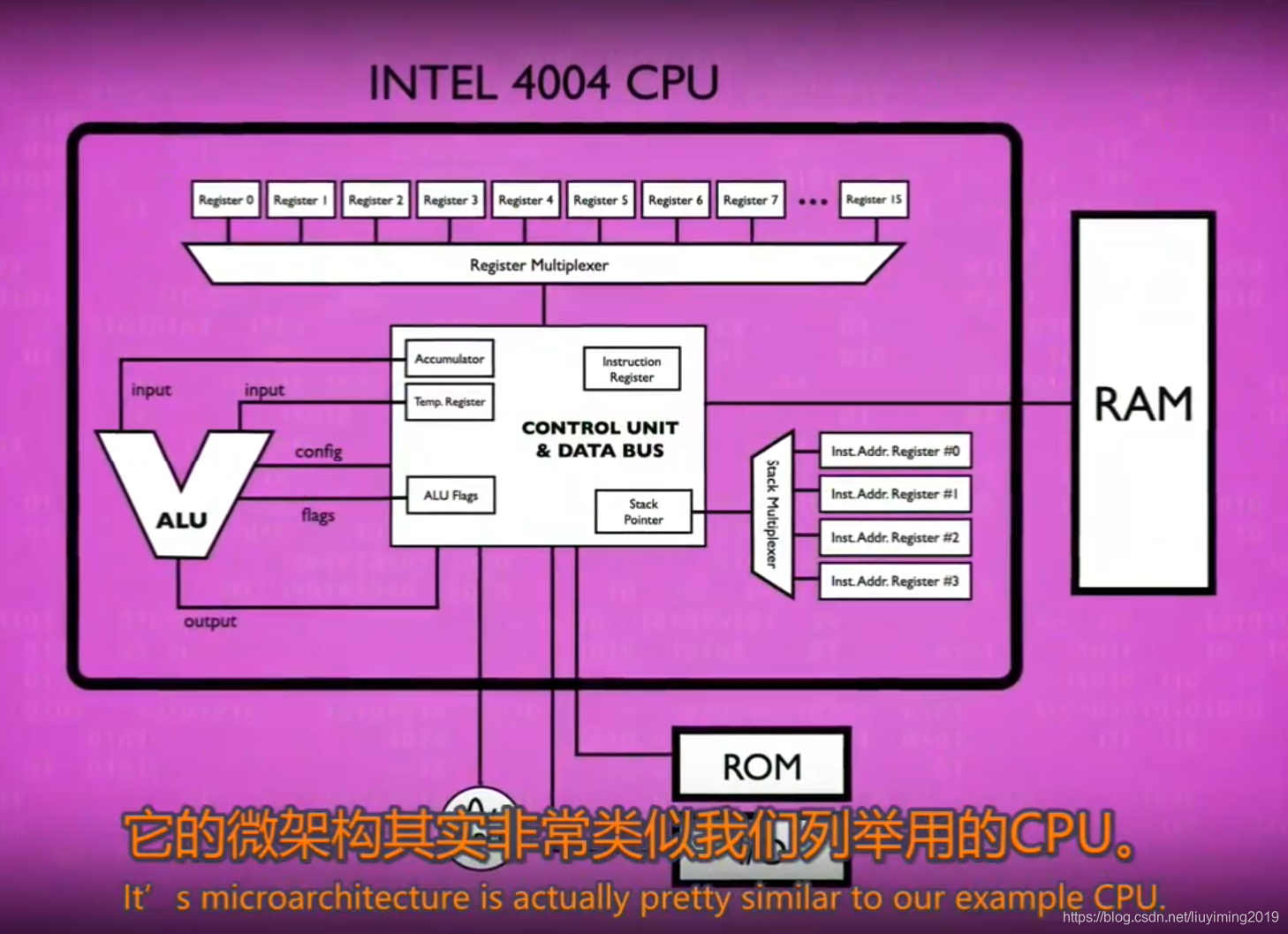

C P U CPU CPU

C P U CPU CPU是执行程序,程序由一系列单独的操作组成,称为指令。他们指示计算机做什么,指令不仅仅是数学指令(发给ALU),还可能是 内 存 指 令 内存指令 内存指令( C P U CPU CPU)和内存通信,然后读/写值,接下来我们将专注于功能部分,而不是线的连接。当我们用一条线连接两个组件时,这是所有必要布线的抽象概念,也称其为微体系架构

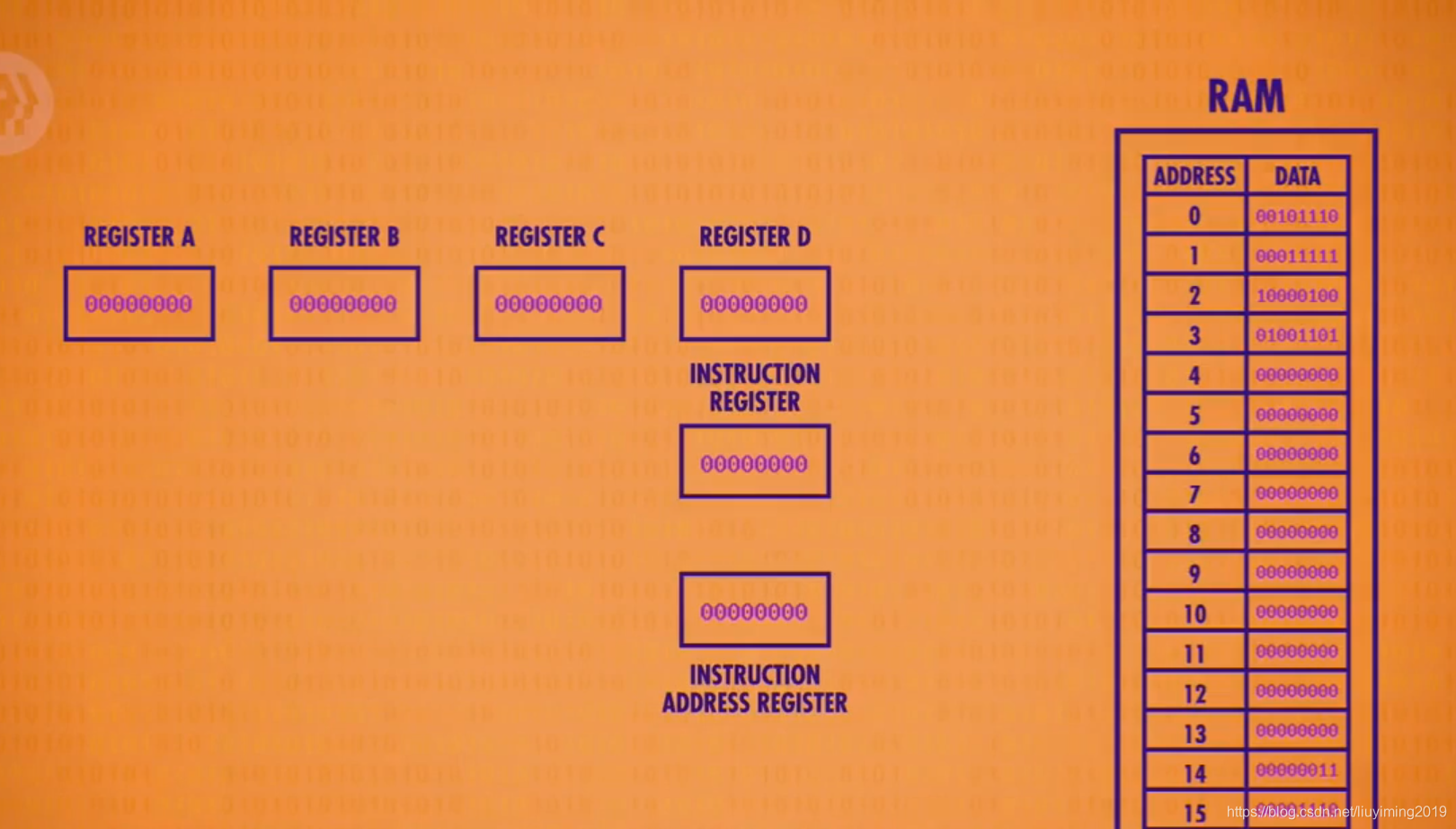

部件的创立

-

R

A

M

RAM

RAM

假设在内存中只有16个位置,每个位置有8位。

- 寄存器

给处理器四个八位寄存器,称之为" A , B , C , D A,B,C,D A,B,C,D",用于临时存储值和更改值

- 程序存储

- 程序存储

我们已经知道数据可以作为二进制存储在内存中,程序也可以存储在内存中

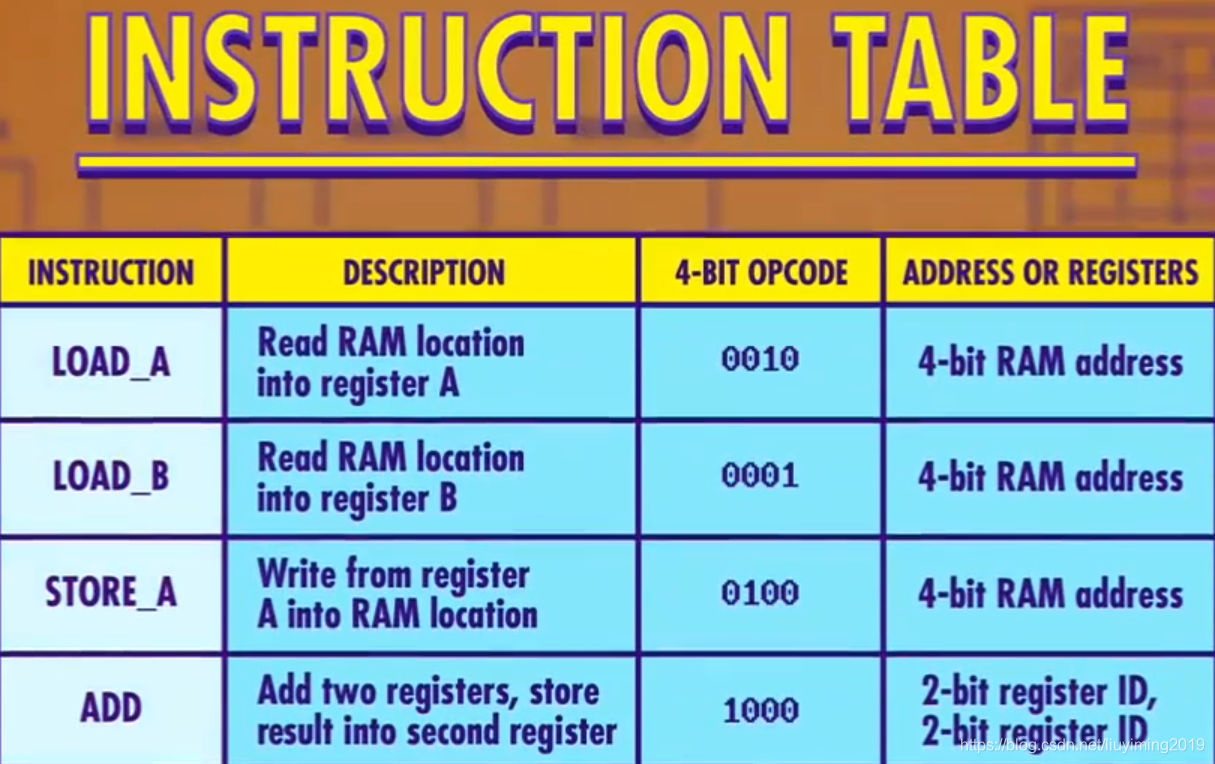

在这个假设示例中,我们用前四位来储存“操作代码”或者简称“操作码”,后四位填写地址码。可以使寄存器或内存中的地址。

| 寄存器名称 | 功能 |

|---|---|

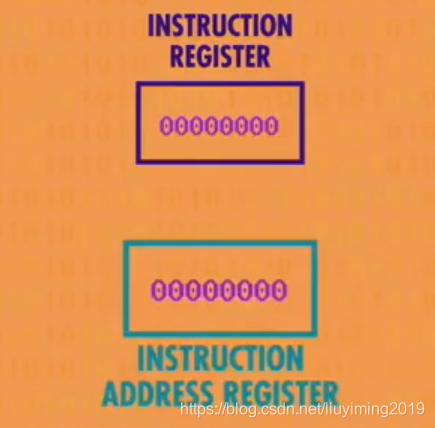

| 指令地址寄存器 | 存储当前指令的内存地址 |

| 指令寄存器 | $12 |

当我们第一次启动,所有的寄存器都从0开始

步骤

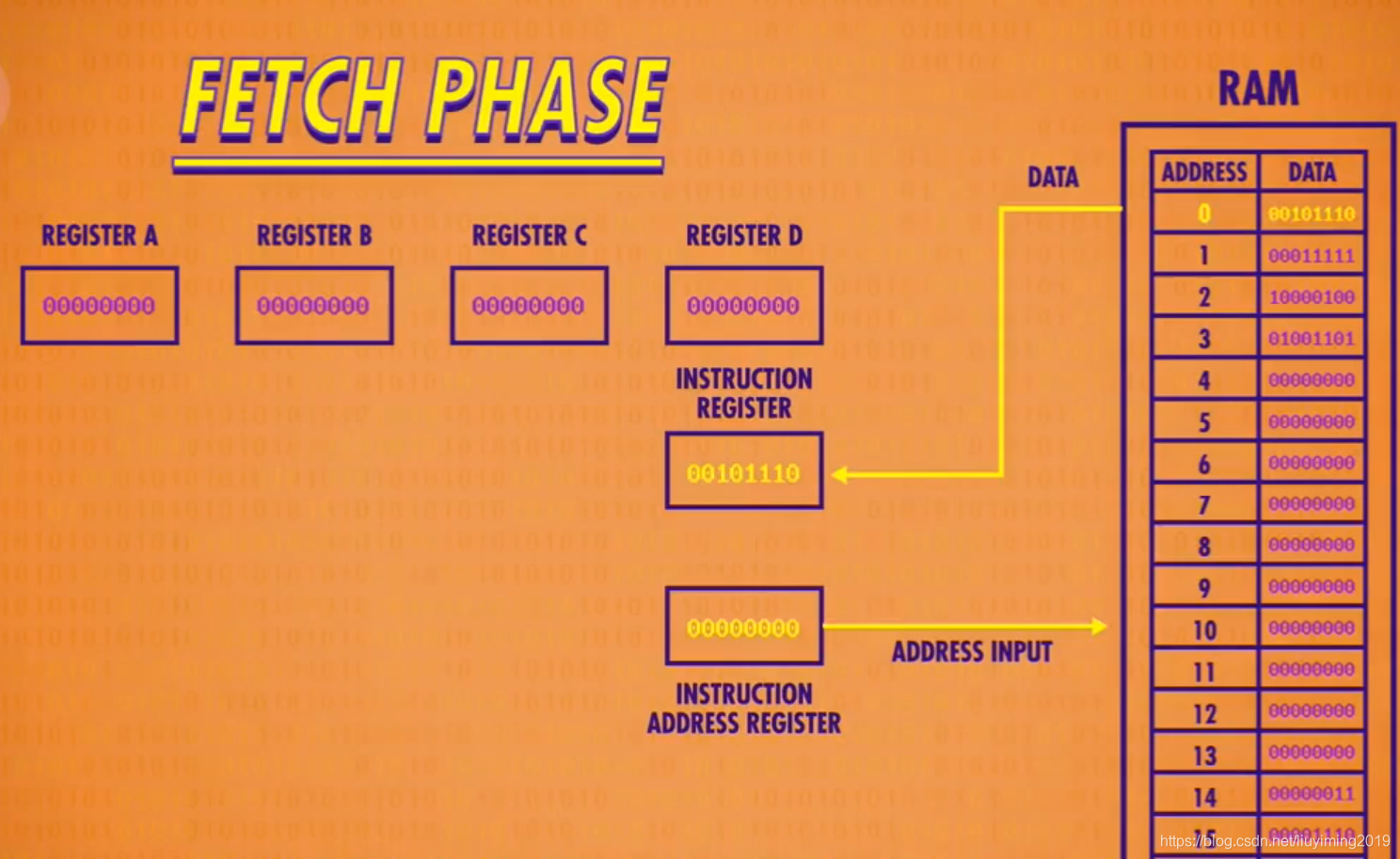

取指令

指令地址寄存器连接 R A M RAM RAM模块

此值复制到指令寄存器中

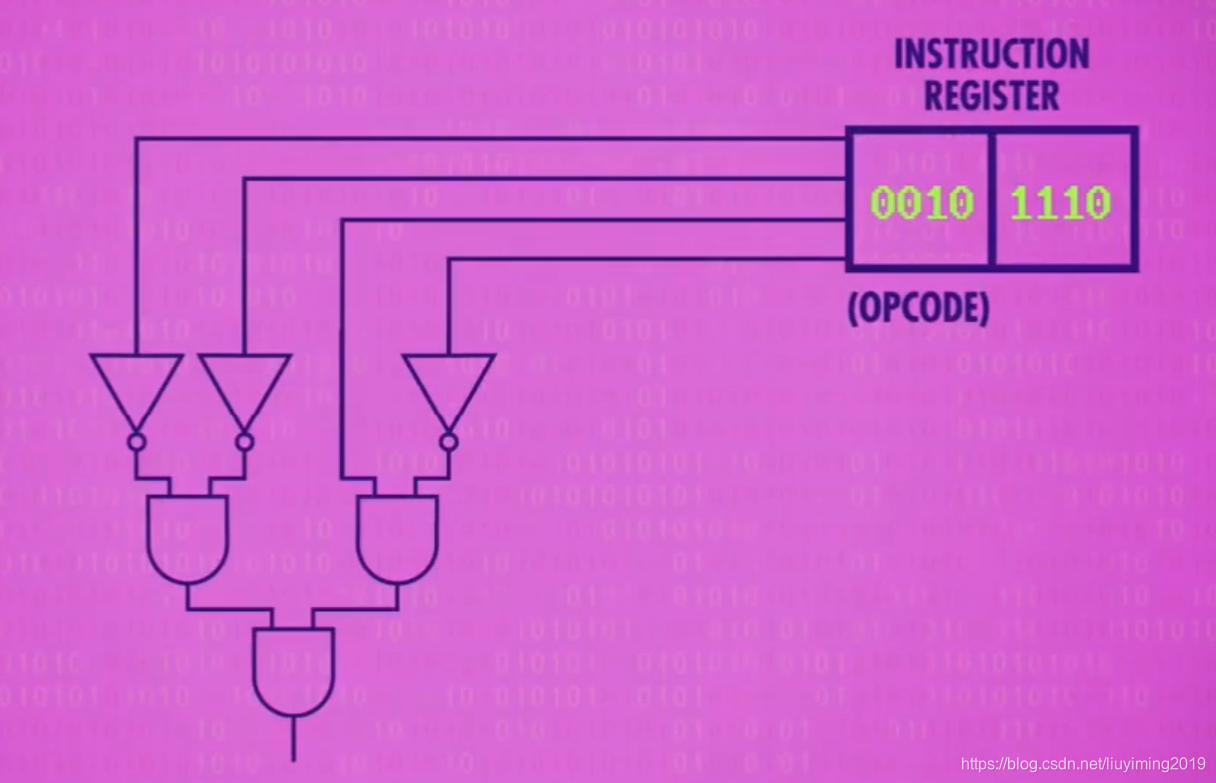

解码

取了指令后,重要的是运行这个指令而不是杀死他。称为解码阶段,接下来,指令由控制单元解码和解释,“控制单元”也是由逻辑门构成,比如为了检验

L

o

a

d

A

Load\, A

LoadA,需要一个电路检验操作码是否与0010匹配,这可以用一些逻辑门完成。

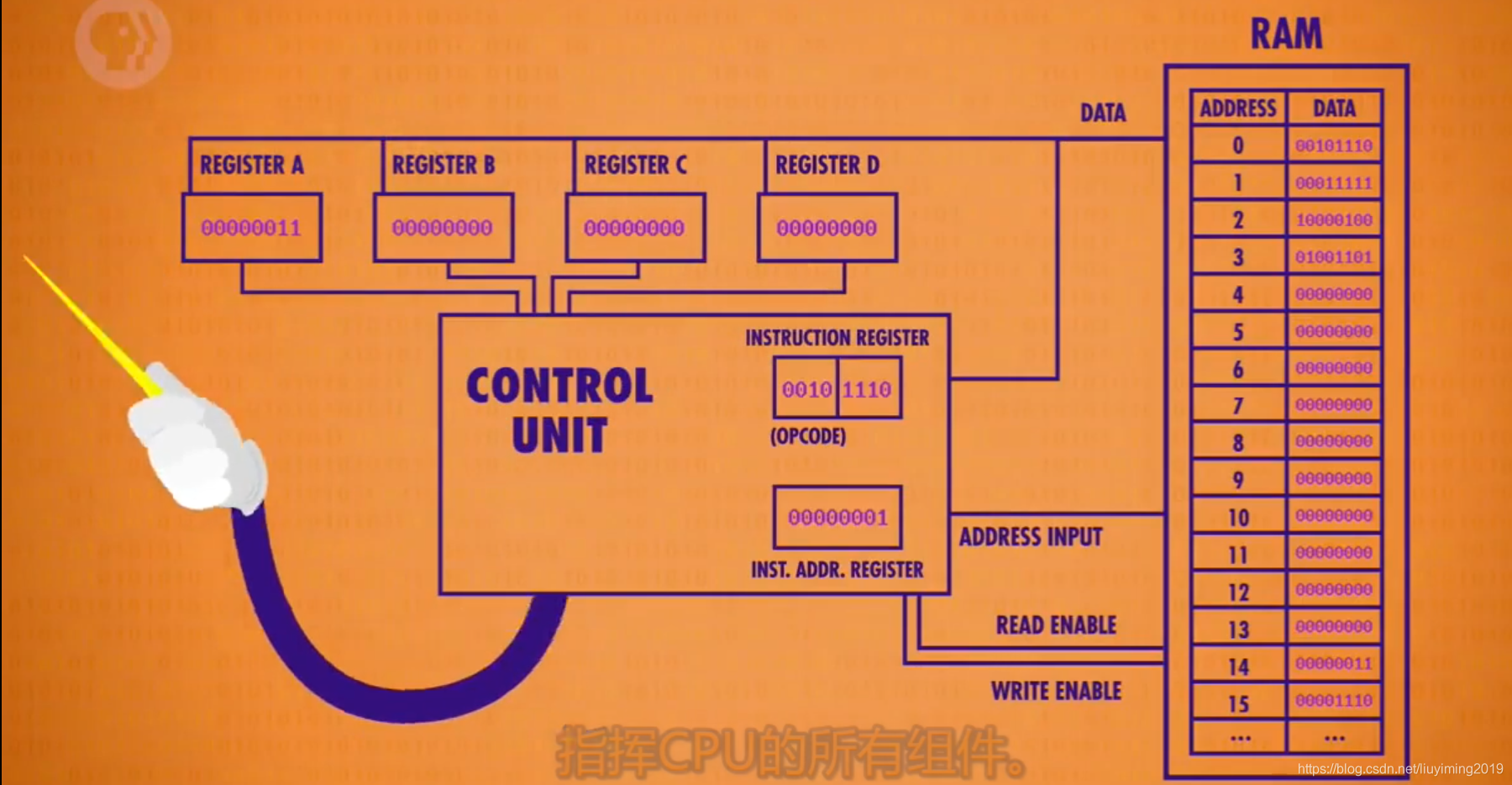

解码电路和之前取指电路封装

具体分析解码电路太过繁琐,我们这里继续进行封装,把控制单元封装

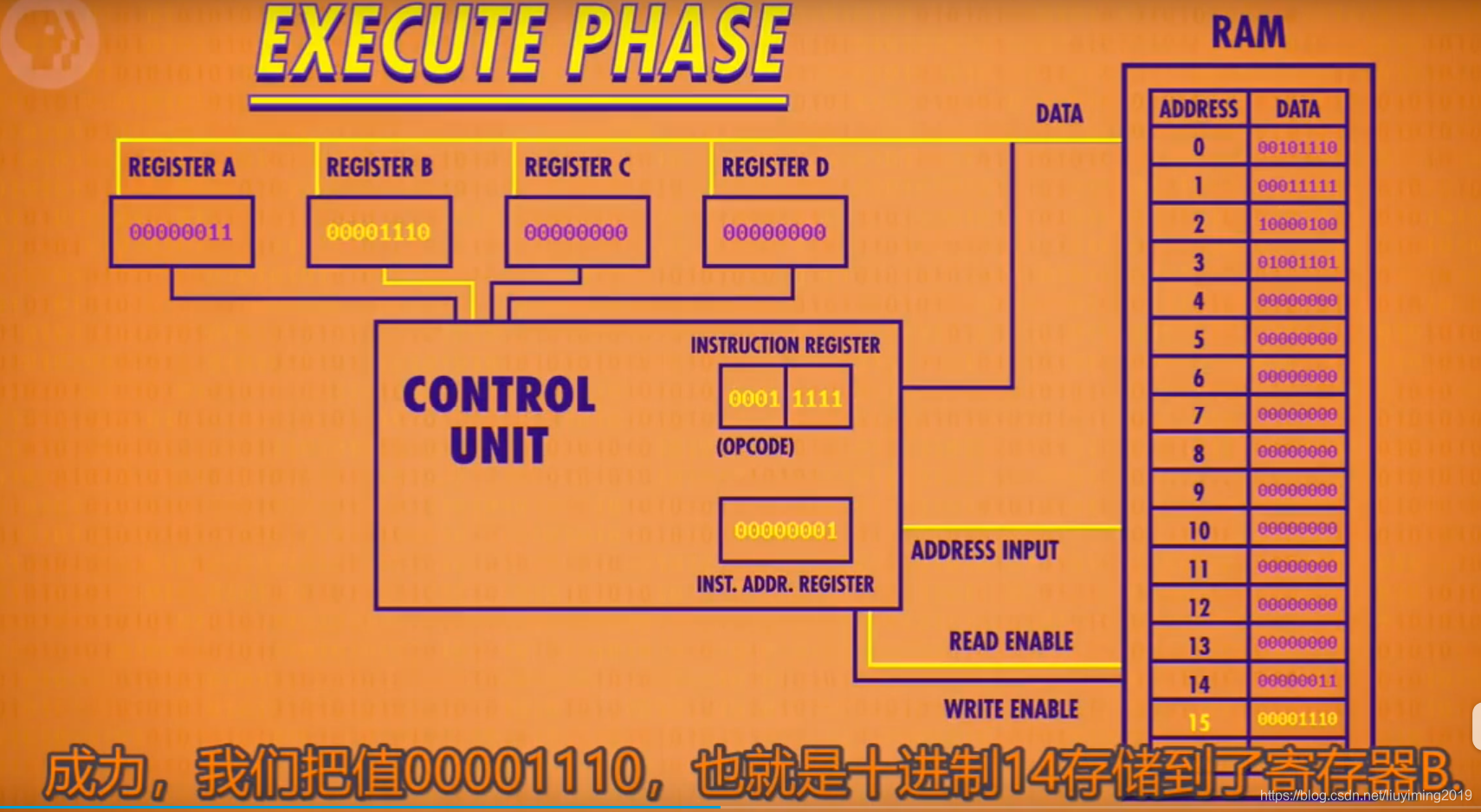

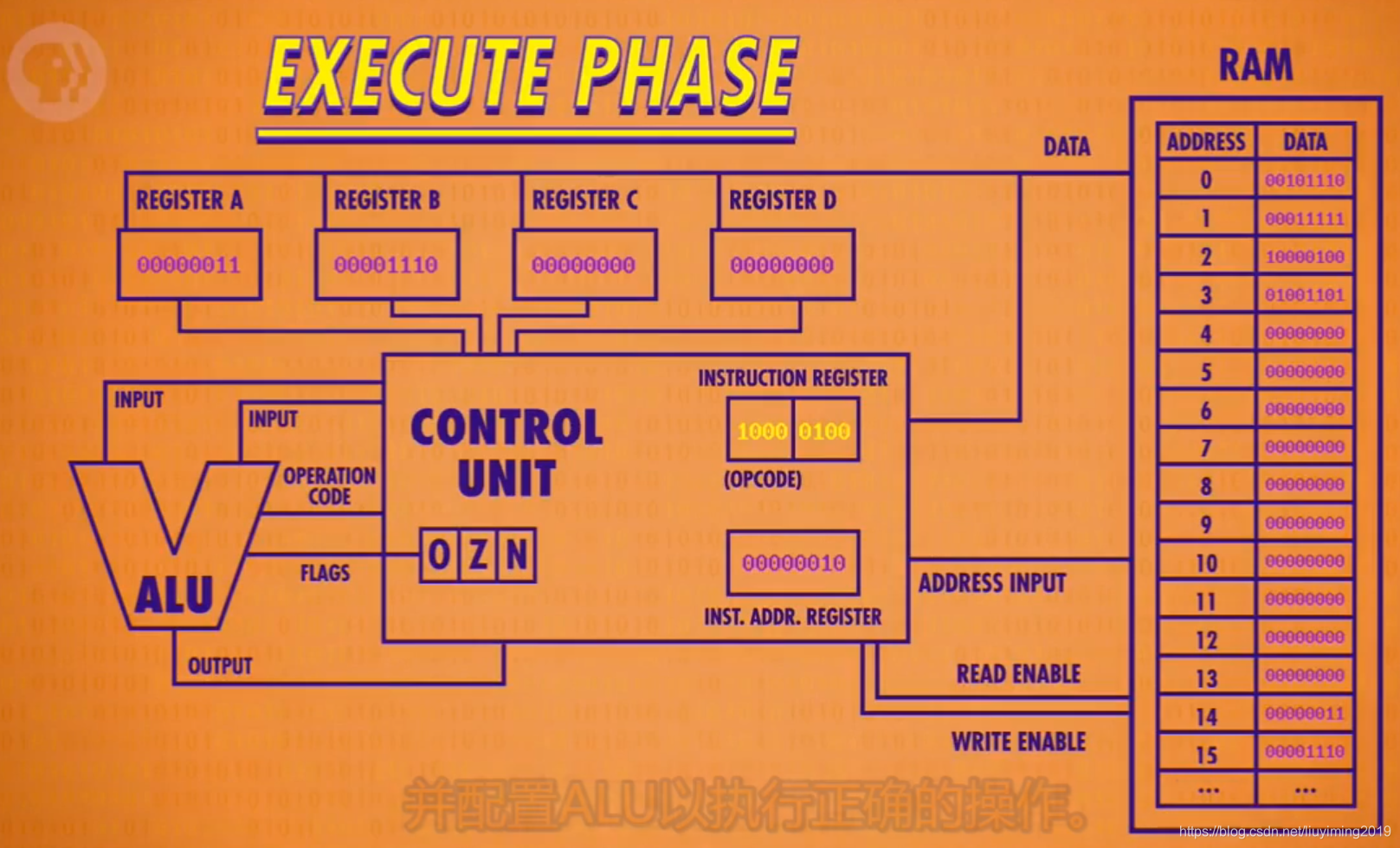

执行代码

-

l

o

a

d

1110

load\, 1110

load1110到

A

A

A

-

l

o

a

d

1111

load\, 1111

load1111到

B

B

B

-

A

D

D

ADD

ADD指令特殊,由于总共有四个寄存器,所以用两位足以,后面是两个寄存器的地址,

00

00

00对应

A

A

A,

01

01

01对应

B

B

B。此时将

A

L

U

ALU

ALU也集成进

C

P

U

CPU

CPU里

- 控制单元将 A , B A,B A,B的值作为输入传入,再传入 A D D ADD ADD操作码来执行 A D D ADD ADD操作,最后输出值保存到寄存器 A A A中,但他不能写入寄存器 A A A,因为新值会进入 A L U ALU ALU反复和自己相加,因此 A L U ALU ALU用内部寄存器暂时保存输出,关闭 A L U ALU ALU,然后在正确的寄存器中写入值。

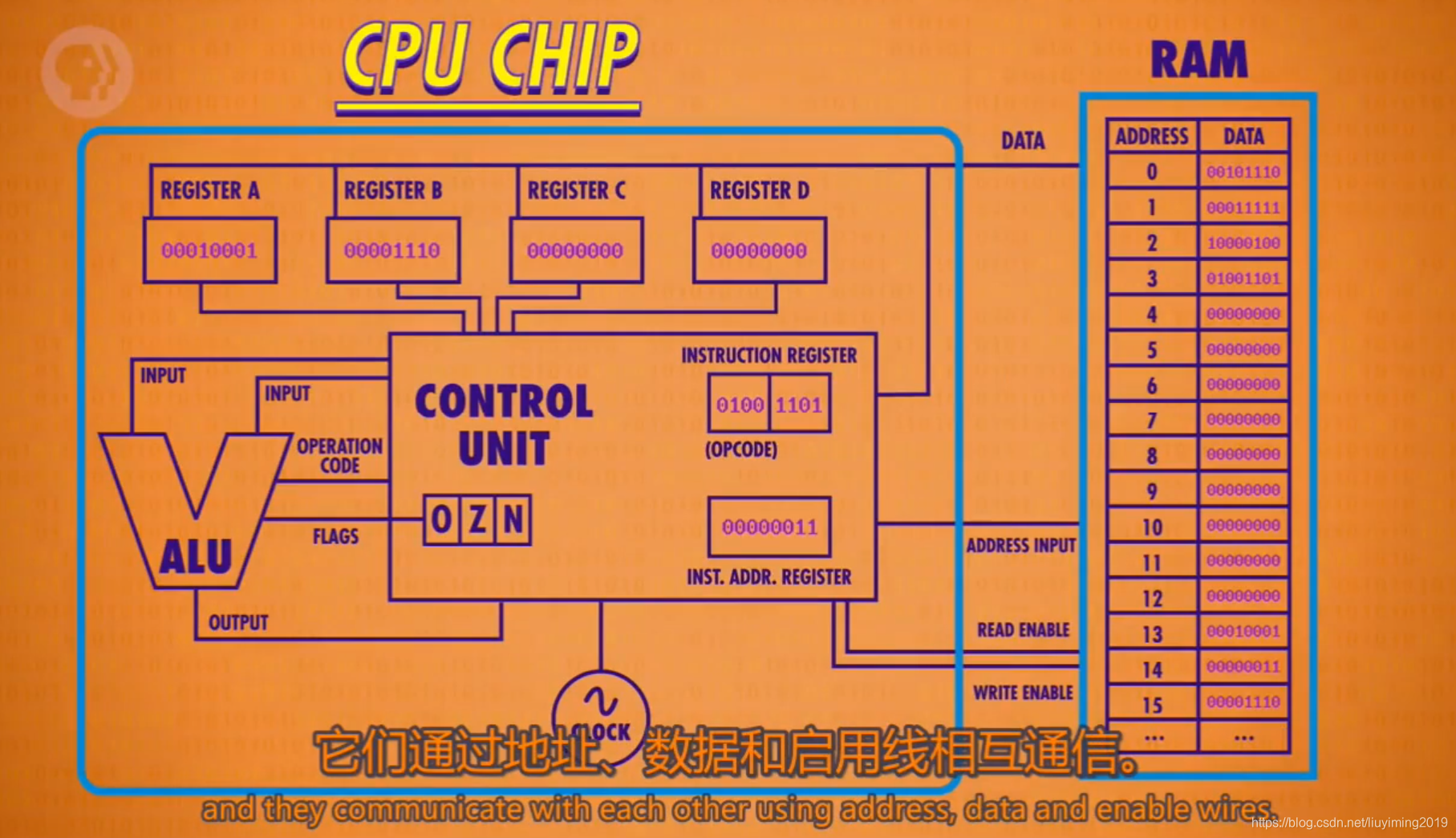

访存取数

根据指令需要,有可能要访问主存,读取操作数,这样就进入访存取数阶段。

写回

- store 像往常一样,我们把地址传给 R A M RAM RAM模块,但不是允许读取而是允许写入,同时打开寄存器 A A A的允许读取,这允许我们使用数据行来传递存储在寄存器 A A A中的数据。

指令地址寄存器自增一

有个时钟利用脉冲控制指令地址寄存器的自增

我们的CPU就做好了!

我们的CPU就做好了!

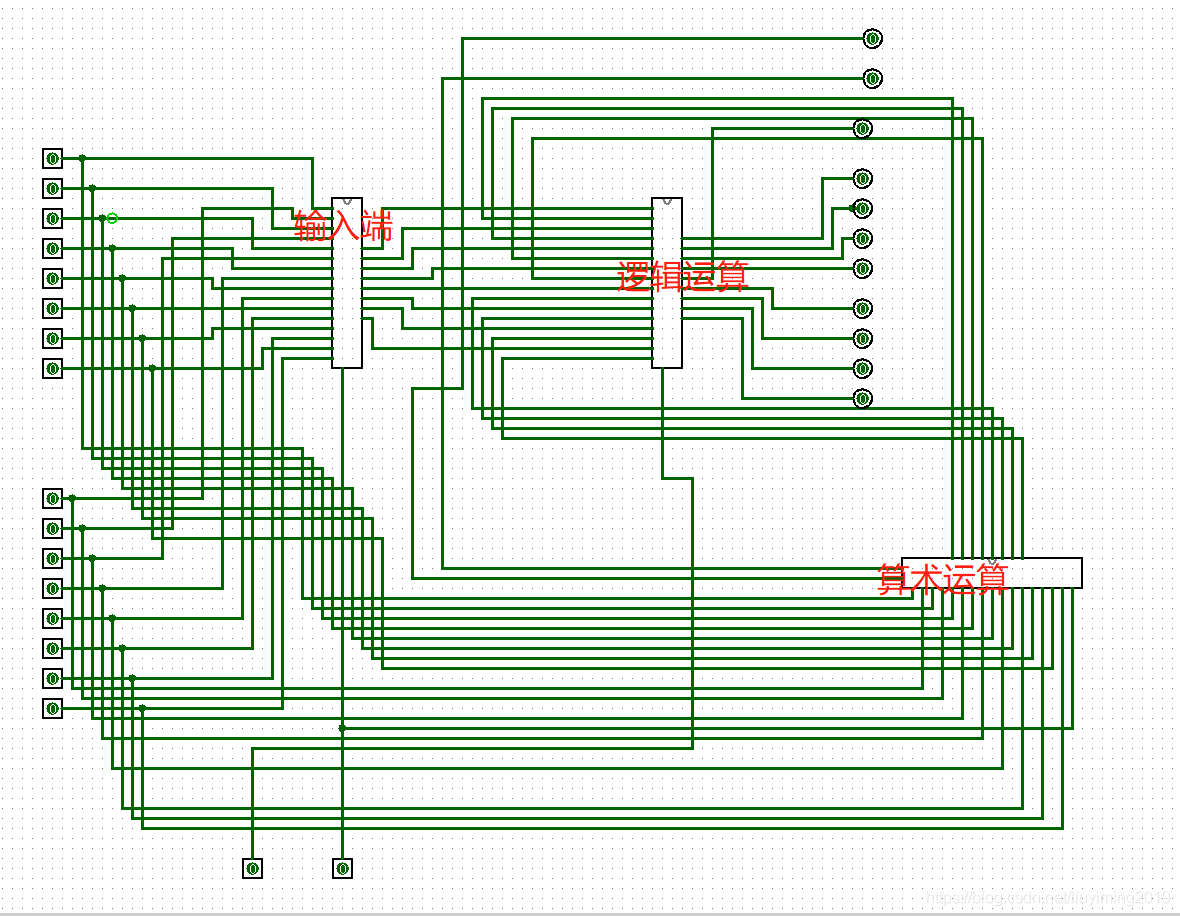

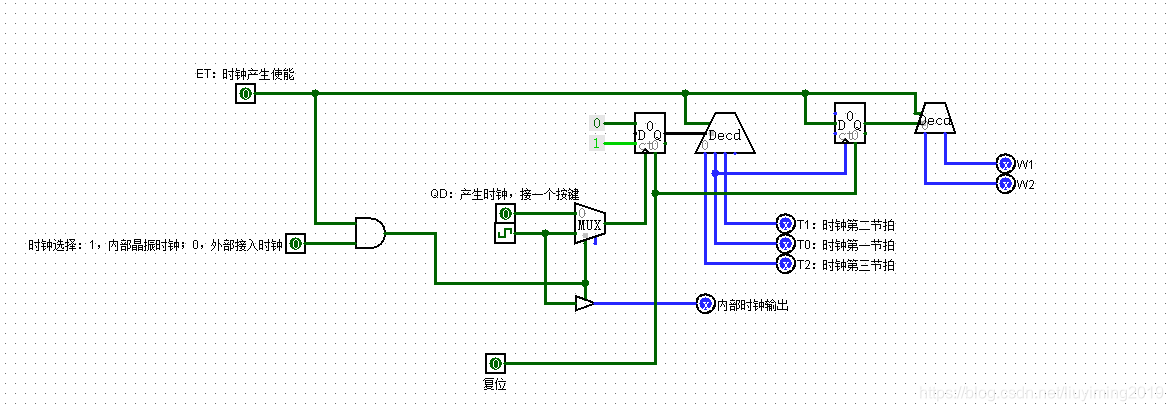

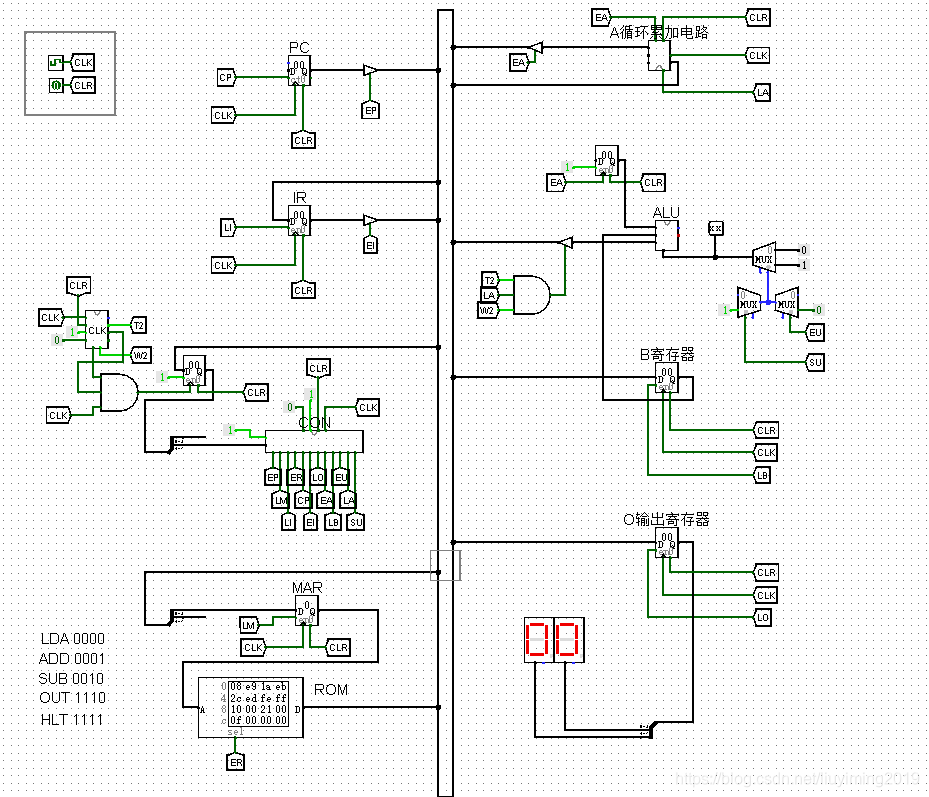

接下来看看logisim的展示:

-

A

L

U

ALU

ALU

-

C

L

K

CLK

CLK

-

C

P

U

CPU

CPU

2499

2499

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?