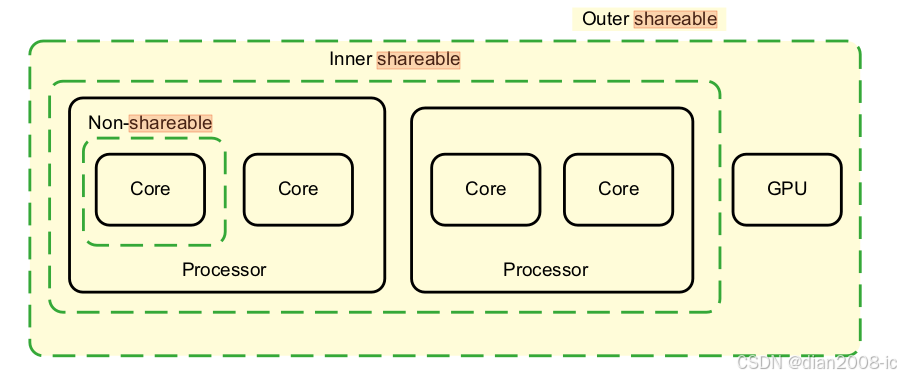

本文基于armv8-a,先看一张图,结合下图来介绍

arm的domain属性说白了就是定义内存区域会在什么范围内共享,有了这个信息才能更好的设计硬件, 硬件的cache coherency是按domain来设计的,同时将同一domain的硬件放到一起减少功耗等一些开销。

Non shareable:内存区域只在本core里使用,比如单核系统,它的所有内存区域都可以设置为这个属性。

Inner shareable:内存区域会在多核之间共享,比如双核A57,这两个核之间需要cache coherency。

Out shareable:内存区域会在多个agents之间共享, 比如arm多核和GPU。

Full system:内存区域会在整个系统共享。

为了提高性能cache coherency机制不能实现原子操作,所以这些共享的domain,在不同的obsever之间会看到不同的内存操作时序,这样就需要有相应的barrier指令来保证不同的observer看到相同的内存操作时序。

这里在多说一些,上面这些domain的设计是针对硬件cache coherency的, 如果没有cached coherency, 也就没有相应的domain,比如一个系统, 两个A55+NPU, 但是这个NPU没有设计硬件cache coherncy功能, 那这个系统就只有两个A55的 inner shareable domain,因为NPU对共享内存的读写我们是通过cache fush和cache ivalide来保证一致性的,这两操作完全可以保持内存访问时序。或者直接不使用带cache的内存。

929

929

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?