f4pga环境搭建教程

- 背景介绍

FOSS Flows For FPGA (F4PGA) project,是一套开源的FPGA工具链,号称the GCC of FPGAs,作用是将写的硬件描述语言(verilog或VHDL)转化为可以在FPGA上运行的可执行文件(bit文件)。可以将它类比为gcc编译器,将c语言编译为计算机上的可执行程序。

将硬件描述语言转换为bit文件,需要三个步骤:

- 综合

将硬件描述语言转化成网表文件,工具是yosys

- 实现

实现布局布线

- 生成

生成bit文件

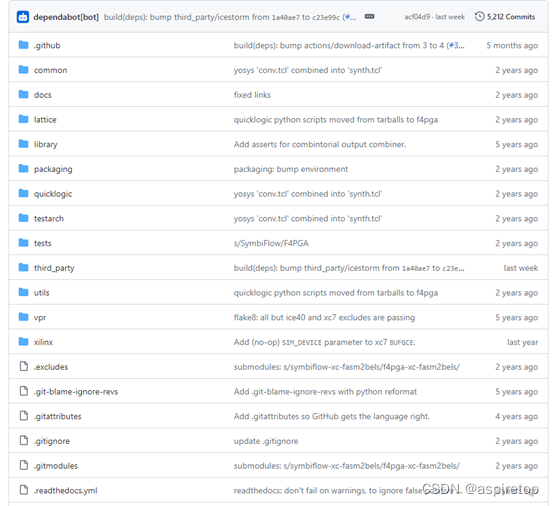

- f4pga项目结构

其中xilinx文件夹下为主要功能区,包含各个tile的原语,以及对应tile的model。

- 具体操作

- make env

耗时很久,有些部分需要科学上网才能下载。运行完成后,会生成一个env文件夹,以及build文件夹,env文件夹包含了conda环境,以及一些其他基础环境。build文件夹是构建后的内容。

- cd build && make

进入build的xilinx文件夹下,会有不同型号的板子,选择自己需要的板子,进入文件夹,执行make命令。以xc7k325t为例,这个过程会生成rr_graph_xc7k325t_test.cache、rr_graph_xc7k325t_test.lookahead.bin、rr_graph_xc7k325t_test.place_delay.bin、rr_graph_xc7k325t_test.rr_graph.real.bin。然后再生成arch.timing.xml文件,至此,针对该板子的建模建库工作完成。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?