如何确定合理的FIFO深度,以保证数据不会丢失。

1、数据

速率表示一段时间内有效数据的快慢。

如一个16位宽FIFO,写时钟100MHz,读时钟801MHz,假设每4个写时钟有一个写使能,每2个读时钟就有一个读使能。

则:

写速率: 100MHz*16bit/4=400Mbit/s

读速率: 80MHz*16bit.2=640Mbit/s

平均速率:指一段时间内平均传输速率,上面例子中,有时10个时钟来一个写使能,有时2个时钟来一个写使能,平均是8个时钟来一个写使能。

则其写平均速率:100MHz*16bit/8=200Mbit/s

突发速率:指可以达到的最快速率,上面例子中,

写突发速率:100MHz*16bit/1=1600Mbit/s

读突发速率:80MHz*16bit/1=1280Mbit/s

2、FIFO深度

FIFO就像一个水池,一个入水口,一个出水口。

1、入水速度比出水速度慢,那么无论水池大小,进来的水应该都能出去

2、入水速度和出水速度相等,那么无论水池大小,进来的水也能出去

3、入水速度比出水速度快,那么无论水池多大,水池都会有溢水可能,水池越大,时间就久。

如上可知,若FIFO写平均速率比读平均速率小或者相等,那么FIFO深度可以设置小一点,如果写平均速率比读平均速率大,那么无论FIFO设置多深,数据都会有溢出,

而稳健的系统不允许丢失数据,必须更改设计架构,确保读平均速率比写平均速率大,这才是稳健的系统。

那么FIFO的深度是不是能随意设置?

要预防一段时间内,写突发速率大于读突发速率的情况,以保证数据不会丢失。

3、深度计算(转载硅农),这个例子理解简单,

一个注意写的时钟和读时钟,二注意有没有空闲周期,类似于占空比,或者是平均速率。

三就是要注意计算突发长度,length==package(例如4Kbit)/位宽(例如8bit)(512)。

四就是要注意背靠背问题:两端周期内,两次突发写数据,连在了一起

Case-1:fA > fB 读写之间没有空闲周期

写速率fA = 80MHz

读速率fB = 50MHz

突发长度Burst Length = 120

读写之间没有空闲周期,是连续读写一个突发长度。

Sol:

写一个数据需要的时间 = 1 / 80MHz = 12.5ns

写一个突发需要的时间 = 120 * 12.5ns = 1500ns

读一个数据需要的时间 = 1 / 50MHz = 20ns

每1500ns,120个数据被写入FIFO,但读一个数据需要20ns的时间

可以计算出,1500ns内读出多少个数据,1500 / 20 = 75

剩下的没有读出,就存在FIFO中,则需要120 - 75 = 45

所以这种情况下,需要的FIFO最小深度为45

拿笔在纸上推导下更清楚。

Case-2:fA > fB 在两个连续读写之间有一个周期的延迟

Sol:

这个题目是制造了一些假象,这其实和Case-1的情况是一样的,因为两个连续的读写之间通常都会有延迟。解决方法,如同Case-1。

Case--3:fA > fB读写都有空闲周期(IDLE Cycles)

写速率fA = 80MHz

读速率fB = 50MHz

突发长度Burst Length = 120

两个连续写入之间的空闲周期为 = 1

两个连续读取之间的空闲周期为 = 3

Sol:

两个连续写入之间的空闲周期为1的意思是,每写入一个数据,要等待一个周期,再写入下一个数据。这也可以理解为每两个周期,写入一个数据。

两个连续读取之间的空闲周期为3的意思是,每读取一个数据,要等待三个周期,再读取下一个数据。这也可以理解为每四个周期,读取一个数据。

写一个数据需要的时间 = 2 * (1 / 80MHz) = 25ns

写一个突发需要的时间 = 120 * 25ns = 3000ns

读一个数据需要的时间 = 4 * (1 / 50MHz) = 80ns

每3000ns,120个数据被写入FIFO,但读一个数据需要80ns的时间

可以计算出,3000ns内读出可以多少个数据,3000 / 80 = 37.5

剩下的没有读出,就存在FIFO中,则需要120 - 37.5 = 82.5 约等于 83

所以这种情况下,需要的FIFO最小深度为83

Case-4:fA > fB并给出了读写使能的百分比

写速率fA = 80MHz

读速率fB = 50MHz

突发长度Burst Length = 120

写使能占得百分比为 = 50% = 1 / 2

读使能占得百分比为 = 25% = 1 / 4

Sol:

用你聪明的大脑想一想,这是不是和Case-3也是一模一样呢,写使能占得百分比为50%,即每两个周期写入一个数据。读使能占得百分比为25%,即每四个周期读取一个数据。

Case-5:fA < fB 读写操作无空闲周期(每两个连续读写之间有一个周期延迟)

Sol:

这类题目,因为读取速率大于写入速率,FIFO永远不会被写满,所以FIFO深度为1就够了。

Case-6:fA < fB 读写操作有空闲周期(读写使能占得百分比问题)

写速率fA = 30MHz

读速率fB = 50MHz

突发长度Burst Length = 120

两个连续写入之间的空闲周期为 = 1

两个连续读取之间的空闲周期为 = 3

Sol:

两个连续写入之间的空闲周期为1的意思是,每写入一个数据,要等待一个周期,再写入下一个数据。这也可以理解为每两个周期,写入一个数据。

两个连续读取之间的空闲周期为3的意思是,每读取一个数据,要等待三个周期,再读取下一个数据。这也可以理解为每四个周期,读取一个数据。

复制上面一遍

写一个数据需要的时间 = 2 * (1 / 30MHz) = 66.667ns

写一个突发需要的时间 = 120 * 66.667ns = 8000ns

读一个数据需要的时间 = 4 * (1 / 50MHz) = 80ns

每8000ns,120个数据被写入FIFO,但读一个数据需要80ns的时间

可以计算出,8000ns内读出可以多少个数据,8000 / 80 = 100

剩下的没有读出,就存在FIFO中,则需要120 - 100 = 20

所以这种情况下,需要的FIFO最小深度为20

Case-7:fA = fB 读写操作无空闲周期(每两个连续读写之间有一个周期延迟)

Sol:

很好理解。

如果读写时钟为同一个时钟,则可以不需要FIFO。

如果读写时钟存在相位差,FIFO深度为1,也是够了。

Case-8:fA = fB 读写操作有空闲周期(读写使能占得百分比问题)

写速率fA = 50MHz

读速率fB = 50MHz

突发长度Burst Length = 120

两个连续写入之间的空闲周期为 = 1

两个连续读取之间的空闲周期为 = 3

Sol:

同样的解题思路。

两个连续写入之间的空闲周期为1的意思是,每写入一个数据,要等待一个周期,再写入下一个数据。这也可以理解为每两个周期,写入一个数据。

两个连续读取之间的空闲周期为3的意思是,每读取一个数据,要等待三个周期,再读取下一个数据。这也可以理解为每四个周期,读取一个数据。

人类的本质是复读机吗?

写一个数据需要的时间 = 2 * (1 / 50MHz) = 40ns

写一个突发需要的时间 = 120 * 40ns = 4800ns

读一个数据需要的时间 = 4 * (1 / 50MHz) = 80ns

每4800ns,120个数据被写入FIFO,但读一个数据需要80ns的时间

可以计算出,8000ns内读出可以多少个数据,4800 / 80 = 60

剩下的没有读出,就存在FIFO中,则需要120 - 60 = 60

所以这种情况下,需要的FIFO最小深度为60

Case-9 如果数据速率如下所示

读写速率相等

每100个时钟写入80个数据

每10个时钟读取8个数据

突发长度为160

Sol:

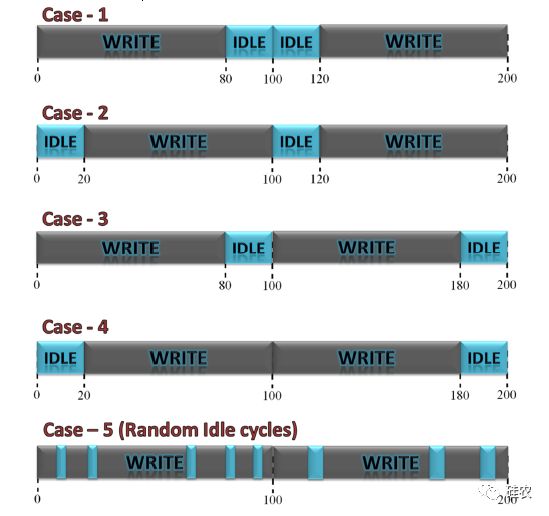

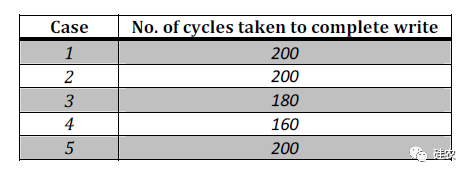

写速率的其他20个周期的位置是随机的。所以就有了下面几种情况。

为了保证数据的传输不丢失,我们考虑到最坏的情况。

考虑的最坏的情况,就是写数据速率和读数据速率之间的差别最大。即写数据速率最大,读数据速率最小。

写操作最坏得情况是Case-4 ,即两次连续的突发写入,又称“背靠背”的情况。

即为在160个周期内写入160个数据。

读数据速率读出每个数据的时间为 = 8 / 10

所以160个周期读出数据的个数为 160 * (8 * 10) = 128

剩下的没有读出,就存在FIFO中,则需要160 - 128 = 32

所以这种情况下,需要的FIFO最小深度为32。

Case-10:举个栗子

写入时钟20MHz

读出时钟40MHz

每1000个时钟周期写入500个数据

每4个时钟周期读出1个数据

读写数据位宽一致。

Sol:

考虑到“背靠背”的情况突发长度则为500 * 2 = 1000

则为每1000个时钟周期写入1000个数据

每4个周期,读取一个数据。

写一个数据需要的时间 = 1 / 20MHz = 50ns

写一个突发需要的时间 = 1000 * 50ns = 50000ns

读一个数据需要的时间 = 4 * (1 / 40MHz) = 100ns

每50000ns,120个数据被写入FIFO,但读一个数据需要80ns的时间

可以计算出,8000ns内读出可以多少个数据,50000 /100 = 500

剩下的没有读出,就存在FIFO中,则需要1000- 500 = 500

所以这种情况下,需要的FIFO最小深度为500

总结

掌握这十种情况,还需要记什么公式?解决所有FIFO深度计算类笔面试题都不再话下。万变不离其宗。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?