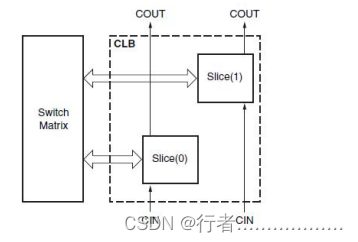

进位逻辑(Carry Logic)Slice 中除了LUT,寄存器,触发器,锁存器外,还提供了专用的快速超前进位逻辑,可以在slice 中执行快速算术加法和减法。CLB 中的专用进位逻辑提高了算术功能(如加法器,计数器和比较器)的性能。包含简单计数器或加法器/减法器的设计会自动推断进位逻辑。如果是更复杂的乘法器可以使用单独的DSP48E1 Slice 实现。7系列FPGA CLB具有两个独立的进位链,如图下所示,1个CLB 中的2个Slice 各有1个CIN.

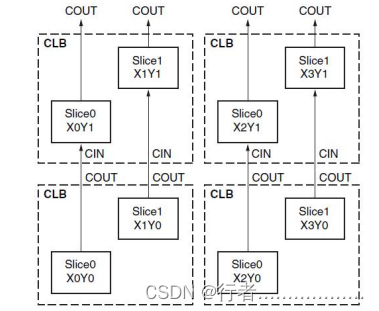

进位链可级联以形成更宽的加/减逻辑,如图下图所示。

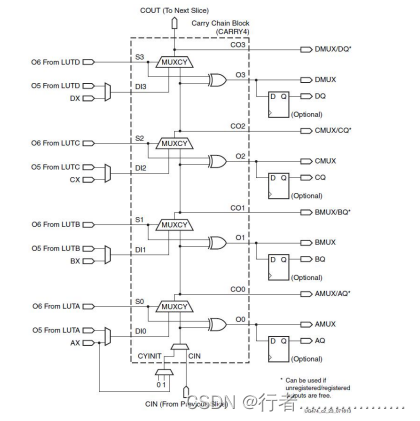

进位链向上延伸,每个slice的高度为4bits。对于每个bit,都有一个进位多路复选器(MUXCY)和专用的XOR门,用于用选定的进位位加/减操作数。专用的进位路径和进位多路复选器(MUXCY)也可以用于级联LUT,以实现广泛的逻辑功能。如下图所示:

CARRY4 CARRY4_inst(

.CO(CO),//4-bit carry out

.O(O),//4-bit carry chain XOR data out

.CI(CI),//1-bit carry cascade input

.CYINIT(CYINIT),//1-bit carry initialization

.DI(DI),1/4-bit carry-MUX data in

.S(S)1/4-bit carry-MUX select input

):

进位链与功能生成器一起使用进位超前逻辑。有10个独立输入和8个独立输出:

输入S输入SO至S3

-进位超前逻辑的“传播”信号

-来自LUT的O6输出

DI输入-DI1至DI4

-进位超前逻辑的“生成”信号

-来自LUT的O5输出

-创建乘数

-或 SLICE 的 BYPASS输入(AX,BX,CX或DX)

.CYINIT

-进位链的第一位的CIN

-0表示加/-1表示减

-动态第一进位位的AX输入

*CIN

-级联Slice以形成更长的进位链

・输出

O输出O0至03

-包含加法/减法之和

.CO输出-CO0到 CO3

-计算每一位的进位

-CO3连接到 Slice 的COUT输出以通过级联多个Slice 形成更长的进位链-创建加法器/累加器

282

282

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?