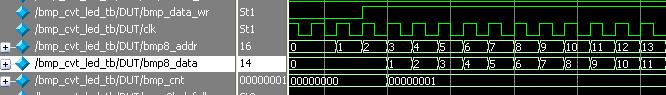

1.mif文件模拟bmp数据源,输出时序如下

其中数据晚于地址2个clk周期建立,建立伊始,便开启写fifo使能。

这里,用testbench测试数据输入fifo,以及数据从fifo读出,来判断逻辑正确性。需要考虑2种情况。

a.fifo未满时,读数据是否正确。

b.fifo满时,此时写入速度大于读取速度时,读数据是否正确。

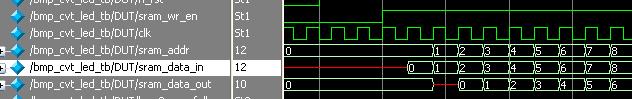

2.用单口ram模拟的sram数据输入时序如下,

sram输入数据要在sram写使能一个clk之后才能有效输入。数据与地址同步建立。

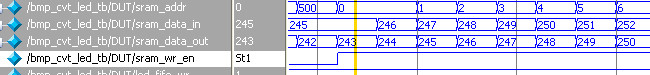

注:还要检查第二次写入数据是否正确。

3.模拟sram数据输出时序

模拟sram数据在地址总线稳定后2个clk,数据总线才稳定。

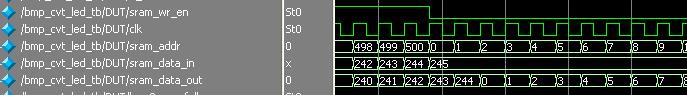

4.sram数据在读出的时候,bmp2sram fifo继续写入,当写满时,fifo写标志位要改变,并保证数据完整

248

248

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?