SD RAM介绍及 PCB Layout处理

SDRAM—Synchronous dynamic random-access memory (SDRAM)。

同步动态随机存取存储器,即数据的读写需要时钟来信号同步。其存储单元不是按线性排列的,是分页的。

DRAM和SDRAM由于实现工艺问题,容量较SRAM大,但是读写速度不如SDRAM(DRAM),且不需要刷新操作。

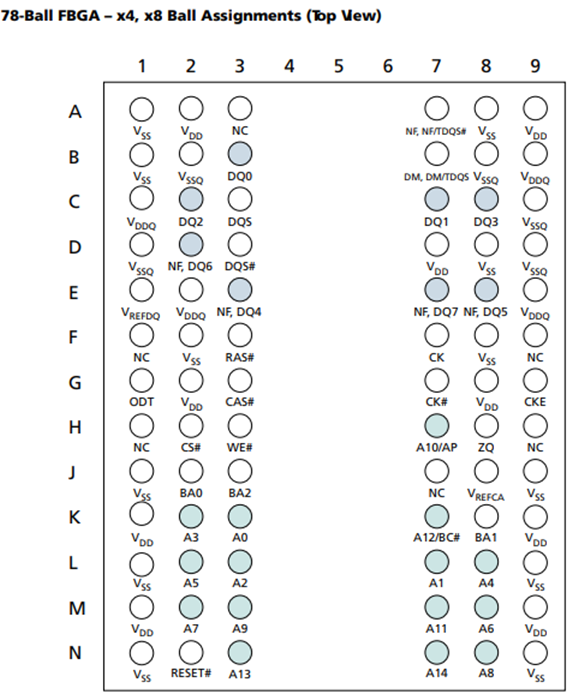

DDR SDRAM X8

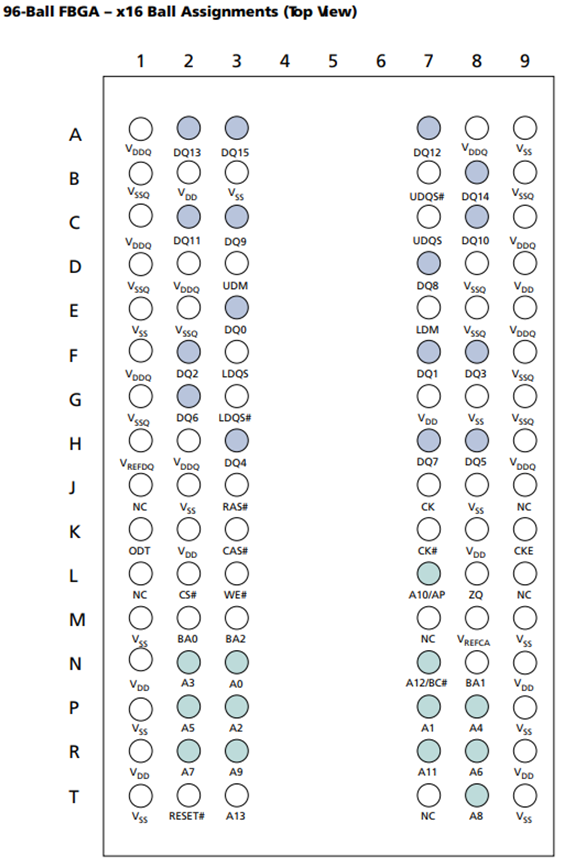

DDR SDRAM X16

DDR信号(我们以16位DDR SDRAM为例说明)

CK差分-时钟

CK和CK#是差分时钟输入。所有地址和控制输入信号均在CK的上升沿和CK的下降沿的交点处采样。

CKE-时钟使能

内部时钟信号以及设备输入缓冲器和输出驱动器激活CKE HIGH,而禁用CKE Low。

将CKE设为低电平可提供预充电掉电和自刷新操作(所有Bank都处于空闲状态),或有效掉电(在任何Bank中均处于活动状态)。对于自刷新退出,CKE是异步的。 在上电和初始化序列期间VREFCA和VREFDQ变得稳定之后,必须在所有操作(包括自刷新)中维护它们。在整个读写访问过程中,必须将CKE保持在较高水平。掉电期间禁用除CK,CK,ODT和CKE以外的输入缓冲器。自刷新期间禁用除CKE以外的输入缓冲区。

CS-片选

CS设置为高电平时,所有命令均被屏蔽。CS为具有多个等级的系统提供外部等级选择。CS被视为命令代码的一部分。

ODT-端接

ODT(注册为HIGH)使能DDR3 SDRAM内部的端接电阻。

启用后,ODT仅适用于x4 / x8配置的每个DQ,DQS-DQS#和DM / TDQS-NU / TDQS(当通过MR1中的模式寄存器A11 = 1启用TDQS时)信号。

对于x16配置,ODT应用于每个DQ,DQSU-DQSU#,DQSL-DQSL#,DMU-DML信号。

如果MR1被编程为禁用ODT,则ODT引脚将被忽略。

命令输入

RAS,CAS和WE(以及CS)定义要输入的命令。

1)RAS:行地址;

2)CAS:列地址;

3)WE:写使能信号。

DM-输入数据屏蔽

DM是用于写数据的输入掩码信号。 在写访问期间,当DM采样到与该输入数据一致的高电平时,将屏蔽输入数据。

DM在DQS的两个边缘上采样。 DM包含UDM和LDM,各自控制8位数据线。

对于x8设备,通过MR1中的模式寄存器A11设置启用DM或TDQS / TDQS#功能。

BA0/BA1-Bank地址输入

BA [2:0]定义正在应用Bank激活,读取,写入,激活,PRECHARGE命令。

BA [2:0]定义在LOAD MODE命令期间加载哪个模式寄存器(MR0,MR1,MR2或MR3)。

BA [2:0]参考到VREFCA。

A0-A15-地址信号输入

为活动命令提供行地址,为读/写命令提供列地址,以从相应存储体的存储器阵列中选择一个位置。 (A10 / AP和A12 / BC具有其他功能,请参见下文)。

在模式寄存器设置命令期间,地址输入还提供操作码。

注:镁光的片子一般DDR地址只有14位。

A10/AP-预充电

在读/写命令期间对A10进行采样,以确定是否应在读/写操作后对所访问的存储体执行自动预充电。(高:自动预充电;低:无自动预充电)。

在预充电命令期间对A10进行采样,以确定预充电是适用于一个Bank(A10低电平)还是适用于所有Bank(A10高电平)。如果仅要预充一个Bank,则按Bank选择该Bank地址。

A12/BC-突发传输

在读取和写入命令期间对A12 / BC进行采样,以确定是否将执行突发斩波。(高,无突发斩波;低:突发斩波)。

RESET-复位

低电平有效异步复位:当RESET为低电平时复位有效,而当RESET为高电平时无效。在正常操作期间,RESET必须为高电平。

RESET是CMOS轨到轨信号,其DC高低为VDD的80%和20%,即DC高时为1.20V,DC低时为0.30V。

DQ[15:0]-数据输入输出

双向数据总线,16位数据线配置。

DQS-数据选通

输出带有读取数据。与读取数据边缘对齐。输入写入数据。LDQS居中对齐以写入数据。

16位DDR的DQS信号有DQSL-DQSL#和DQSU-DQSU#两对差分线;

DDR3 SDRAM仅支持差分数据选通,不支持单端。

TDQS-8位数据选通

TDQS / TDQS仅适用于x8 DRAM。 通过MR1中的模式寄存器A11 = 1启用时,DRAM将在TDQS / TDQS上启用与DQS / DQS相同的终端电阻功能。

当通过MR1中的模式寄存器A11 = 0禁用时,DM / TDQS将提供数据屏蔽功能,并且不使用TDQS。

x4 / x16 DRAM必须通过MR1中的模式寄存器A11 = 0禁用TDQS功能。

ZQ Calebration-ZQ校准

ZQ校准参考引脚

VREFDQ

DQ参考电压

VREFCA

CA参考电压

DDR电源

DQ Power Supply: 1.5 V +/- 0.075 V

DQ电源:1.5 V +/- 0.075 V

DDR电流

DDR电流:Die Rev. D,取决于DDR的Die设计生产时的工艺,像D工艺下DDR的电流大小是425mA,在M工艺下电流为230mA。(D、H、K、M)

DDR的Layout要点

DDR电源设计

DDR3 SDRAM 的 VREF(0.75V)电源都必须和其它电源隔离,可以通过较宽的走线(20mil 及以上)连接,保证每个电源管脚尽可能就近摆放去耦电容,并且最好在 PCB上对 VREF 加包地屏蔽处理。

VREF 参考电压设计

1、参考电压设计时,需要重点关注参考电压的布线。根据 SSTL-15 协议要求,VREF参考电压上的噪声不得超过±1%,为了降低噪声,VREF 走线宽度尽量宽,建议将VREF 在电源平面层通过铜皮布线,且不能作为信号线的参考平面;

2、每个 VREF pin 要加去耦电容且走线尽量宽,与其它信号线间隔 20mil~25mil。

DDR时钟差分线

1、CLK 信号走线长度最长不能超过 4inch;

2、CLK 差分对信号走线严格走差分,差分对内部走线的长度差推荐小于 5mil,即:|LCLKxP-LCLKxN| < 5mil;

3、DDR 走线线宽和线间距不能小于 4mil。

数据选通DQS信号

1、DQS 差分对内部两根信号线严格等长,差分走线长度偏差推荐小于 5mil,即:

|LDQSxP-LDQSxN| < 5mil;

2、DQS 以 CLK 时钟走线长度为参照进行走线,其走线长度相对于 CLK 的走线长度允许的偏差为﹣500~0mil,即:LDQSx = LCLKx- (0~500mil);

DQ信号线

1、DQ[7:0]以 DQS0 的走线长度为参照进行走线,允许偏差范围为±100mil,即:

LDQ[7:0] = LDQS0 +/-100mil;

2、DQ[15:8]以 DQS1 的走线长度为参照进行走线,允许偏差范围为±100mil,即:LDQ[15:8] = LDQS1 +/- 100mil;

3、数据走线推荐以 GND 层为参考平面,在无法满足的情况下,要求同组同层走线。

数据掩码DM信号

1、DM0 以 DQS0 的走线长度为参照进行走线,允许偏差范围为±100mil;

2、DM1 以 DQS1 的走线长度为参照进行走线,允许偏差范围为±100mil。

地址信号线ADDR

ADDR[14:0]以 CLK 时钟走线长度为参照进行走线,允许偏差范围为±200mil,

即:LADDR = LCLK +/- 200mil;

控制线

控制信号线 BA[2:0]、DM、CKE、CSN、WEN、CASN、RASN、ODT 的 PCB 走线长

度要求如下:

1、控制信号线以 CLK 时钟走线长度为参照进行走线,允许偏差范围为±200mil;

2、为减小信号反射,建议所有 DDR3 SDRAM 接口信号走线避免穿越电源地分割区域,保持完整的电源地参考平面。

综述阻抗控制

信号线尽量短,走线路径上尽量少打过孔,保证走线阻抗的连续性。在 2 层板PCB 设计时传输线阻抗控制在 140Ω±10%,在 4 层板 PCB 设计时传输线阻抗控制在 50Ω±10%,差分线阻抗控制在 100Ω±10%。

2020于深圳

454

454

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?