目录

TRST-Resets the JTAG TAP controller and the CPU internal debug logic

SRST- Resets the CPU core and peripherals

下图为Trace32工具为ARM debug设计的 JTAG pin 脚图:

其中,TRST和SRST信号是可选的。

TRST-Resets the JTAG TAP controller and the CPU internal debug logic

Test Reset 信号用于JTAG Test Access Port (TAP)的异步重置。它将reset TAP的状态机,以及绝大部分ARM系列的debug相关寄存器。从调试器的视角,TRST信号从调试器输出至目标板。它是低电平有效。

SRST- Resets the CPU core and peripherals

System Reset,低电平有效,用于reset 目标系统。这个信号同样也可以用于调试器检测目标处理器是否处于reset状态。该信号可以是输入或者输出。

SYStem.Mode Down

禁用调试器,CPU的状态不会改变。

SYStem.Mode Nodebug

同down,禁用调试器,CPU的状态不会改变。

SYStem.Mode Prepare

reset 目标处理器,可以通过重置信号(reset line)或者CPU中特殊的reset寄存器来实现。之后,将提供对CoreSight DAP接口的直接访问。对于reset,reset line必须连接到调试器。

调试器将初始化一些debug 端口(JTAG,SWD,cJTAG)以及CoreSight DAP接口,但是并不连接到CPU。这种Mode可以用于一些不需要debug CPU或者绕过CPU的场景,调试器直接通过内存总线(memory bus),比如AXI,AHB或者APB等,直接通过CoreSight DAP的内存访问端口,比如:

- 调试器绕过CPU,直接访问物理内存。如果改映射存在,内存应该在被访问前,被初始化。

- 调试器访问外设,例如,在调试模式下,停止CPU之前配置寄存器。可能需要先对外设进行计时和供电,然后才能访问它们。

- 第三方软件或一些特殊调试器使用 TRACE32 API通过 TRACE32 调试器硬件访问调试端口和 DAP。

SYStem.Mode Go

通过复位线复位目标,初始化调试端口(JTAG、SWD、cJTAG),并开始进程执行。对于重置,重置线必须连接到调试连接器

SYStem.Mode Attach

不会发生重置,CPU状态(正在运行或停止)不会更改。调试端口(JTAG,SWD,cJTAG)将被初始化。 执行此命令后,例如,可以使用 Break 命令停止用户进程。

SYStem.Mode StandBy

通过复位线使目标保持复位状态,并等待检测到电源。对于重置,重置线必须连接到调试连接器。 一旦检测到电源,调试器就会恢复尽可能多的调试寄存器(例如片上断点、矢量捕获事件、控制),并从复位中释放CPU以启动进程执行。 检测到 CPU 断电时,调试器会自动切换回待机模式。这允许调试电源周期,因为调试寄存器将在上电时恢复。 注意:通常只能在CPU运行时设置片上断点和矢量捕获事件。要设置软件断点,必须停止 CPU。

SYStem.Mode Up

通过复位线复位目标,初始化调试端口(JTAG、SWD、cJTAG),停止CPU,并进入调试模式,相关寄存器被恢复为默认值。 对于重置,重置线必须连接到调试连接器。 所有寄存器的当前状态都是从 CPU 读取的。

SYStem.Mode Up 操作内部实现原理

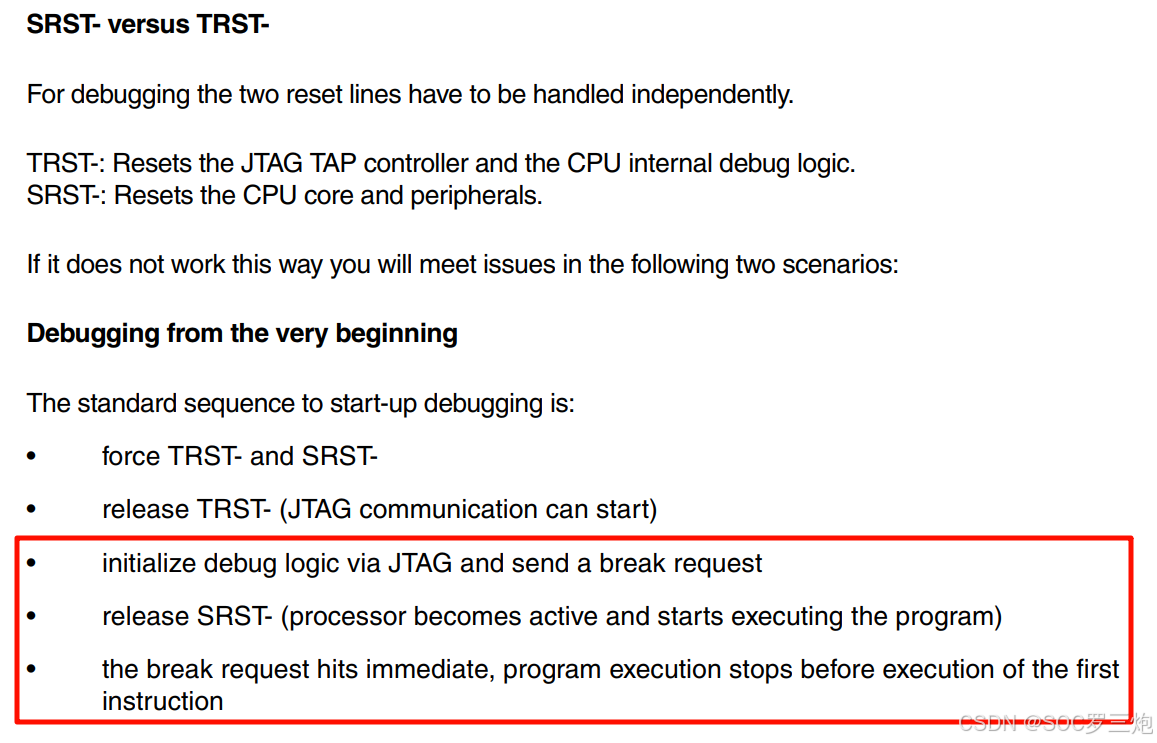

Trace32会使用sys.up命令连接到chip,通过上文,一个sys.up命令包含三个部分:Attach CPU(连接到CPU),触发SRST,将CPU break在第一条指令的地方。他们之间有个先后顺序:

- 拉高(触发) TRST和SRST

- 释放TRST,TRST结束后,JTAG 可以开始通信功能

- Trace32通过JTAG 初始化debug 逻辑模块,并且向CPU发送break请求(此时CPU处于SRST状态,虽然发送了请求,但是CPU此时无法响应,因此该请求尚未生效)

- 释放SRST,SRST一结束,CPU便开始工作,准备开始执行指令

- 预先发送的break请求生效,CPU在执行第一条指令之前,,先响应该break请求,导致CPU停在第一条指令

参考文章:

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?