在描述FIFO(First In First Out)或其他存储结构的同步复位(Synchronous Reset)功能时,srst(或wr_rst/rd_rst,即写入和读取时钟域的同步复位信号)仅适用于块RAM(Block RAM)、分布式RAM(Distributed RAM)、移位RAM(Shift RAM)或内置FIFO的实现。

1 使用Common Clock的块RAM、分布式RAM或移位RAM FIFOs

同步复位(srst)在断言时同步地复位所有计数器、输出寄存器和内存。由于复位引脚与输入时钟同步,并且FIFO中只有一个时钟域,因此不需要额外的同步逻辑。

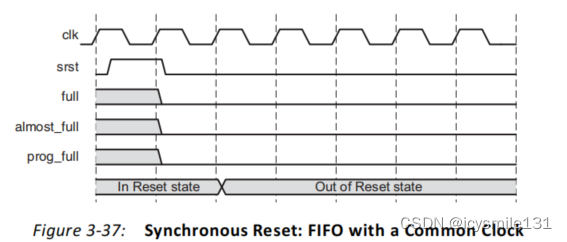

图3-37展示了当srst被释放(即,从活动状态变为非活动状态)后,FIFO中各种标志(flags)或状态位的变化。

在同步复位被释放后,FIFO将恢复到其初始状态,所有计数器将被清零,输出寄存器将被复位,并且内存内容(如果适用)也可能被清除(这取决于具体的FIFO实现和设计需求)。此后,FIFO将准备好再次接受数据。

2 使用Independent Clock 块和分布式RAM FIFOs(在没有选择(Enable Reset Synchronization选项的情况下)

同步复位(wr_rst/rd_rst)在断言时同步地复位各自时钟域的所有计数器和输出寄存器。因为复位引脚是与各自时钟域同步的,所以不需要额外的同步逻辑。

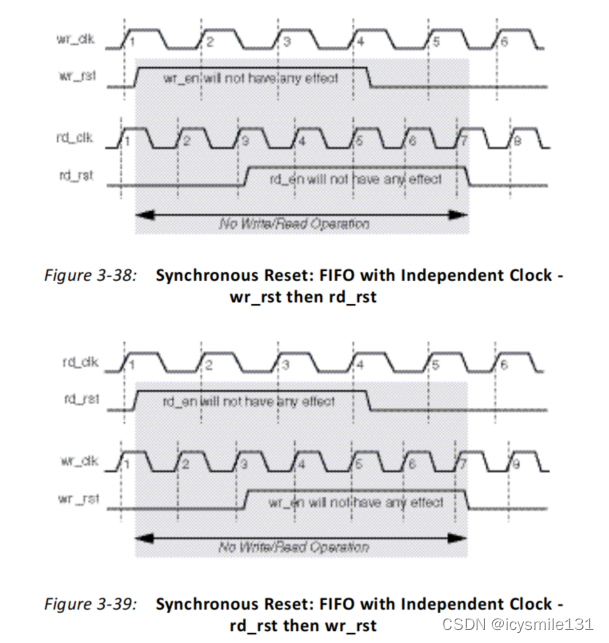

当同时断言写入和读取的同步复位(wr_rst/rd_rst)时,至少要保持一个时钟周期,如图3-38所示。复位的断言/去断言时间可能有所不同,在这个期间,FIFO的输出会变得无效。为了避免意外的行为,不要在第一个复位断言到最后一个复位去断言的期间执行写入或读取操作。

注意:对于使用首字直通(First-Word-Fall-Through)和ECC配置构建的FIFOs,sbiterr和dbiterr(分别表示单个位错误和双位错误的标志)可能在两个复位(wr_rst和rd_rst)都去断言后执行有效读取之前保持高电平状态。

图3-38和图3-39详细说明了复位的过程。

在复位过程中:

- 在两个时钟域(写入和读取)中分别使用

wr_rst和rd_rst进行同步复位。 - 这两个复位信号需要同时断言至少一个时钟周期。

- 在复位断言期间,FIFO的输出不应被使用,因为它们可能是无效的。

- 在复位去断言之后,直到执行了有效的读取操作之前,

sbiterr和dbiterr标志可能保持高电平状态(如果FIFO配置了ECC)。 - 在复位期间,不应执行写入或读取操作以避免FIFO的未定义行为。

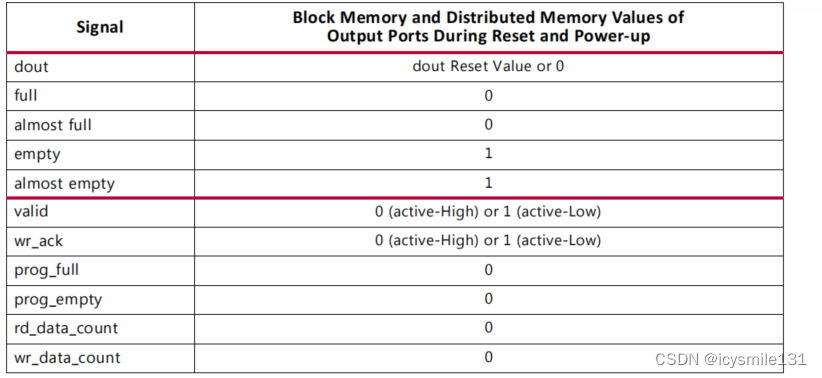

下表中定义了在上电和复位状态下输出端口的值。如果没有指定dout(数据输出)的复位值,它默认会被设置为0。FIFO只需要一个时钟周期的复位脉冲。在复位被释放后的时钟周期,FIFO就可以进行数据传输了。对于同步复位,上电时的值与复位状态相同。

3 使用UltraScale架构内置的FIFO

UltraScale架构内置的FIFO主要支持同步复位(srst),并且这个复位必须始终与写入时钟(clk/wr_clk)同步。这些内置的FIFO需要至少一个写入时钟周期的同步复位脉冲。同时,这些FIFO提供了wr_rst_busy和rd_rst_busy输出信号。

当srst被断言时,wr_rst_busy输出会在wr_clk的上升沿之后立即被断言,并持续保持到复位操作完成。在wr_rst_busy被断言之后,内部复位会与rd_clk域同步。当到达rd_clk域时,rd_rst_busy会被断言,并保持到rd_clk域的所有信号复位完成。此时,rd_rst_busy会被去断言。在公共时钟模式下,由于不需要跨时钟域,这个逻辑会被简化。

在复位状态下,rd_en和wr_en端口必须被去断言(即,不能进行读取或写入操作)。复位的断言会导致full和prog_full标志去断言,而empty和prog_empty标志会被断言。在wr_rst_busy和rd_rst_busy被释放之后,FIFO核心会退出重置状态并准备好进行写入。

underflow(下溢信号)是依赖于rd_en(读取使能)的。如果rd_en被断言(即,激活)并且FIFO为空,那么underflow就会被断言(即,发出下溢信号)。overflow(上溢信号)是依赖于wr_en(写入使能)的。如果wr_en被断言并且FIFO已满,那么overflow就会被断言(即,发出上溢信号)。

需要注意的是,下溢和上溢信号直接与FIFO基本单元连接。如果rd_en被断言并且FIFO为空,那么下溢信号会被断言。如果wr_en被断言并且FIFO已满,那么上溢信号会被断言。

此外,当应用复位时,请确保FIFO Generator IP核的输入时钟是自由运行的。违反这一点可能会导致复位挂起状态,这可能需要硬重启或重新引导来恢复。

1668

1668

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?