采取低电压是为了降低功耗。

为什么CPU会发热

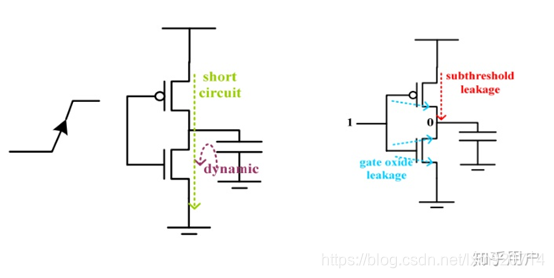

从含有1亿4000万个场效应晶体管FET的奔腾4到高达80多亿的Kabylake,Intel忠实的按照摩尔定律增加着晶体管的数目。这么多个FET随着每一次的翻转都在消耗者能量。一个FET的简单示意图如下:

当输入低电平时,CL被充电,我们假设a焦耳的电能被储存在电容中。而当输入变成高电平后,这些电能则被释放,a焦耳的能量被释放了出来。因为CL很小,这个a也十分的小,几乎可以忽略不计。但如果我们以1GHz频率翻转这个FET,则能量消耗就是a × 10^9,这就不能忽略了,再加上CPU中有几十亿个FET,消耗的能量变得相当可观。

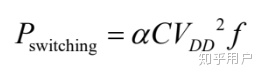

实际上能耗和频率成线性相关。能耗关系公示是:

![]()

P代表能耗。C可以简单看作一个常数,它由制程等因素决定,制程越小,C越小;V代表电压,和P是二次方的关系;而f就是频率了。理想情况,提高一倍频率,则能耗提高一倍。

通俗的讲,CPU可以看作由几十亿到上百亿个小开关组成的。开关切换的速度f决定了计算机的性能。为了高性能,必须提高开关速度f,这才是大家关心的。而V则因为省电的原因越小越好。那为什么不把V定成很低很低不到1V呢?

这里要引入门延迟(Gate Delay)的概念。简单来说,组成CPU的FET充放电需要一定时间,这个时间就是门延迟。只有在充放电完成后采样才能保证信号的完整性。而这个充放电时间和电压负相关,即电压高,则充放电时间就短。也和制程正相关,即制程越小,充放电时间就短。让我们去除制程的干扰因素,当我们不断提高频率f后,过了某个节点,太快的翻转会造成门延迟跟不上,从而影响数字信号的完整性,从而造成错误。这也是为什么超频到某个阶段会不稳定,随机出错的原因。那么怎么办呢?聪明的你也许想到了超频中常用的办法:加压。对了,可以通过提高电压来减小门延迟,让系统重新稳定下来。

也就是说,为了省电,要降低V,但为了达到数G的主频,而不得不提高电压V到一个可以接受的最小值,达到一个平衡。Vcore现在约1V。

不可忽视的其他因素

现实情况比这个更复杂。实际上,上面公式里的P只是动态能耗,主要关注占比90%的Dynamic Power,造成Dynamic Power的原因是寄生负载电容的充放电。CPU的整体功耗还包括短路功耗和漏电功耗:

短路功耗是在FET翻转时,有个极短时间会有电子直接跑掉。它和电压、频率正相关。

漏电功耗是电子穿透MOSFET的泄漏情况,它和制程与温度有关。

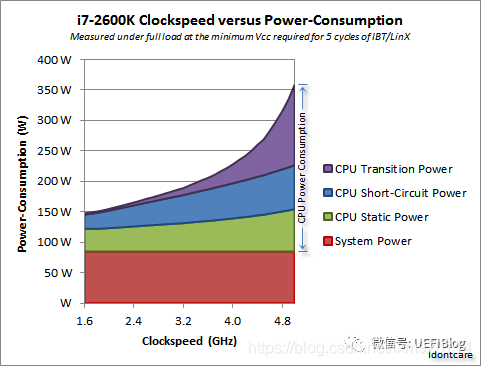

综合这些,我们看一个实际的例子:

这里的Transition Power就是动态能耗,可以看出它随着频率陡峭上升;短路功耗和频率几乎呈现线性关系;而Static power就是指漏电功耗,它也上升是因为频率上升导致温度上升,从而漏电加重。从中我们可以看出短路功耗也和电压有关,而电压越低,短路功耗也越低。

1.降低电压是目前集成电路里面非常常用也是非常有效的节能手段,而且降低电压同时也要配套相应的工艺,越先进的工艺,电压要求也比较低,所以现在的CPU和GPU电压都比较低。

2.CPU或GPU上百安的电流不是一个Vcc脚提供的,而是很多电源pin分摊的,所以几百个引脚平摊下来上百安的电流也不算太夸张。

晶体管密度太大导致pn节间距很小,耐压低,不能高压。电压是由制造工艺决定的,越是制成线宽小的工艺,能承受的电压越低,同时寄生电容也更小,使得同频率下单管功耗更低。如果电压太高,意味着制程必须要高很多,如果想5V供电,需要1微米的制程才可以,太小的话,容易击穿,导致损坏。

CPU工作过程是通过内部很多开关(FET管)在不停开关开关切换来实现逻辑运算和存储,这个实际上是要对内部的电容(FET管的寄生电容)充电放电来实现。

电源只是表示最大能提供的能力,负载才决定用了多少。

计算机芯片大多都是大规模数字集成电路,其供电设计主要考虑以下几个因素:

- 半导体硅管的正向饱和压降约0.7V,锗管约0.3V。考虑到其它因素的影响,发射极-集电极电压一般一两V即可工作,因此不需要太高的电压。

- MOSFET开关速度快,但导通电阻更大,饱和压降更高(1.7-3V),因此需要更高的工作电压才能正常工作。

- 半导体集成电路的硅片中电阻阻值越大面积越大,越不经济,且会造成废片率急剧上升。

- 过高的供电电压需要使用大量大阻值电阻限压限流,以保证降低功耗。

- 大量功耗消耗在电阻上,不利于降低电路耗散功率(即电路自身消耗的功率),使用经济性、系统供电设计、整机散热设计都会提高难度。

- 考虑到供电电路的设计简便以及逻辑电平的兼容性(一致性),需要统一供电电压。

- 供电电压越接近半导体的最低工作电压,意味着在电阻上的功率损耗越低,电路的能耗效率越高,越省电。

- 逻辑电平越低,电平建立时间越短,意味着数字电路的工作频率越高,响应时间越短,性能越强。

- 供电电压太接近工作电压的话也不行,电源波动噪声和外界干扰将对电路造成较大影响,反而会降低电路性能。因此供电电压需要有一定的“冗余”。

- 较高的工作电压除了提高晶体管功耗外,还会对集成电路的耐压特性提高要求,加大制作难度和成本。大电流则问题不大,金属导体的散热性能和导电性能相对容易改善。

因此,一般来说,对于大规模数字电路,供电电压最好是工作电压的1.7~2倍,性能与功耗及造价能够达到最佳平衡点。这个电压值根据不同的半导体材料(决定工作电压),大约是2.5-5V之间。

至于“大电流”,因为管子数量多,动辄集成上千万颗晶体管数量累加所致,并非是有意这样设计,在保证正常工作的前提下,当然是电流越小越好,功耗就越低嘛。即便提高电压,也是需要通过降压电阻来维持晶体管的工作电压,电流还是需要那么多。降低电流只能通过改进集成电路的制程工艺,提高材料纯度,改进材料特性等等来得到。大电流有一个特点,就是,对于电源引脚的增加,同时对于电容的需求增加,频繁的跳转,电源芯片供电波动太大,所以只能是电源模块给储能电容供电,储能电容给芯片电源引脚电容供电,芯片电容再给芯片供电。

首先,半导体特征尺寸,越来越小,目的有两个,同一个die芯片(芯片的核心部分,比看到的芯片小很多,芯片为了走线方便,做了很多引脚引线),上面可以有更多逻辑单元。这是主要目的,因为晶圆(wafer)的成本是固定的。那么,die越小,单个芯片成本越低。

所以,半导体工艺最近四十年的方向,都是将特征尺寸做小,目的是,降低成本。特征尺寸做小以后,还有一个附加效应,就是跨域pn节沟道,所需要能量就不需要那么大了。从这个角度看芯片的core电压,就是越来越低,1.8V/1.2V/1V/0.8V,以前用POLA架构电源,就可以提供低电压大电流。特征尺寸小了以后,还有两个效应,一个是热效应的减少,芯片散热被优化。对于layout,更容易一点点。

除了功耗与供电电压成正比要求降低功耗外,还有一个原因是芯片对速度的要求,越高的速度对应的晶体管氧化层厚度会很小,这个决定了晶体管承受电压的能力.因此应对高频应用cpu中的晶体管的耐压也就1.几V。换个高压不说不说芯片热死了,而是击穿了。

降低器件的电压等级,是有效减低绝缘应力的办法。

功耗分析:总功率可以分为三个部分:dynamic, static, short circuit.

如图,short circuit power 来自于在输入信号的上升/下降时间不是0,所以不能简单看成0和Vdd,会在变换的过程中有介于0-Vdd的值,在这个时候nMOS和pMOS会同时导通导致短路电流。在正常情况下short circuit power一般会比dynamic power少一个数量级,因此可以先忽略。

Dynamic 来自于:输入信号从1-0,从电源看,消耗的能量是

其中一半会被PMOS消耗,一半会存在输出的电容中,因此实际消耗的能量只有一半。

输入信号从0-1,存在电容中的能量被NMOS消耗。

那么信号从1-0-1这一个循环中,消耗的能量是![]() 。

。

当系统的频率是f,每个周期有a的可能性输入信号会变化(1-0-1)那么功率为:

由此可见想要降低功耗有4个方法,降低a(例如对bus信号做特殊的编码),降低C(少见),降低Vdd(本题的答案),降低频率(比如笔记本电脑平时会处在低功耗模式,玩游戏把频率升起来,反应是风扇开始噪音)。

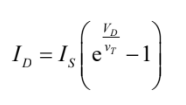

static来源于:

1.pn结可以看成一个二极管,二极管反向会有导电电流,例如inverter中输入信号是0,NMOS的d是vdd,那么n 会和p substrate 有反向电流:

2. 在Vgs小于Vth的时候,会有泄露电流(这在现代工艺中占有主导地位)

可以看出更小的vds会减少static电流。也就是说,降低vdd可以同时减少dynamic和static的功耗(short curcuit忽略),从而降低总功耗,减少发热和电量损失。

受到摆率的限制,为了提高运行速度,必须要降低电压。开关元件的功耗主要发生在切换过程中,完全断开和完全导通的时候功耗很小。为了降低功耗,必须减小开关时间占比,也必须降低电压。

8MHz左右的处理器,一般电压5V。72MHz左右的处理器,一般3.3V。150MHz频率附近的低端处理器,如DSP,内核的电压大约是1.8V或1.9V。1GHz的元件内核电压大约是1.1V或1.2V,甚至有极端的0.9V。

有时候,内核电压和IO电压不等。内核电压低而速度快,IO电压高而速度慢。有的电路或者芯片自带变压模块。不能用供电电压猜测工作电压。

11万+

11万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?