一、芯片供电

每路电源都要求在一定范围内。每路电源都有允许的输入电压范围。可能需求多路电源;可能分模块供给。

不同模块对电源质量的要求可能不同。有些模块可能较为敏感,抗扰度低。有些模块可能容易干扰其他模块。

电源分配网络存在一定电感,器件高速开关会引起一定的电压波动。需要做好去耦、隔离、保证参考平面完整。

二、电源去耦

当器件高速开关时,高速器件需要从电源分配网络汲取瞬态电流。

因为电源分配网络中存在一定的电感,没有去耦的电源分配网络会有较大的瞬时电压尖峰。即不利于电压稳定,也可能产生较大的 EMI。

去耦电容的主要作用就是提供局部的、低阻抗的电源。

提供给高速开关电流一个较小的环路面积,减小 EMI。

2.1、去耦电容

电容的主要作用是滤波和储能,而去耦电容还有消除电路中耦合现象(即电路中由于瞬间负载增幅过大而导致的高电源电流)的作用。

去耦电容在选择时需要考虑去耦电容的自谐振频率以及考虑电容耐压值。(贴片陶瓷 0.1uF/16MHz, 0.01uF/50MHz, 1000pF/160MHz, 100pF/500MHz)初始设计,普通模块的电源一般取 0.1uF,时钟模块相关电源、高速接口电源宜采用多个电容并联或不同容值电容并联的方式。总之,足够低的阻抗是目标。通常可以通过实测芯片电源噪声,进行调整,也可以通过电脑软件建模、仿真分析。

2.1.1 去耦电容的分布

理想:每个引脚至少能放置一个。

实际:有时难以满足,存在两三个电源引脚共用一个去耦电容的情况。

关键的电源引脚(时钟模块相关电源、高速接口电源)重点照顾。

2.1.2 去耦电容的布局布线

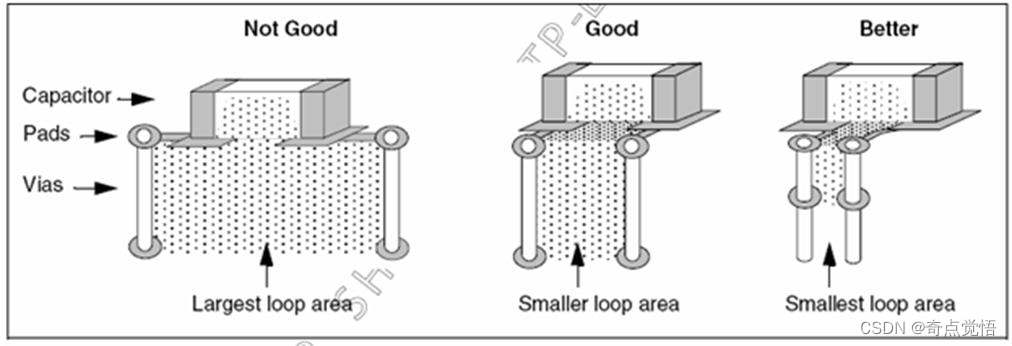

最重要的原则:最小化电感、最小化高频环路。

除以上例子中的处理方式之外,缩短、加宽去耦电容引脚的走线,多打几个过孔,优化参考平面的完整性等都是优化的方式。

另外尽量不分享 Vcc 和“ GND”过孔,尤其是时钟、高速接口模块的电源的去耦电容及其他对电源噪声敏感的模块的去耦电容之间。

三、电源隔离

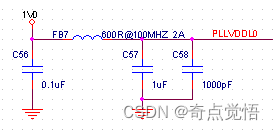

在芯片供电中,我们常用磁珠对某些路电源进行隔离。

3.1 磁珠的特性

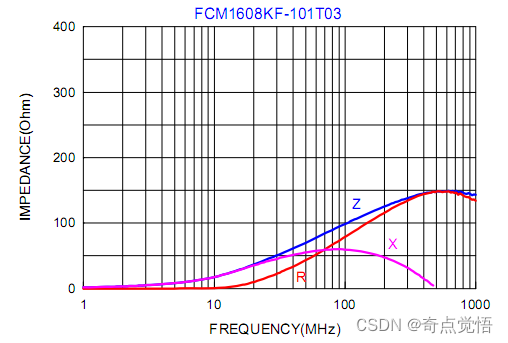

等效一个变化的电阻和一个变化的小电感串联。对某一频段的高频电流呈现高阻抗,阻碍高频电流流过。并有额定电流、直流电阻。

3.2 磁珠的选择

一般需要磁珠对芯片的高频开关电流呈现高阻抗。具有较小的直流电阻,从而压降小。并且拥有足够大的额定电流。

在特定的设计中,磁珠可能无法起到很好的隔离作用,也可考虑用电感来隔离。

四、电源的 PCB 走线

线宽:根据铜箔厚度、走线电流、温度来确定走线宽度,一般来说越宽越好。同时需要注意的是电源岛上被过孔打碎的地方也需要注意有效线宽。

电源部分远离 RF 电路。高频容易干扰低频。

电源走线在相同层应尽量避免与其他信号线平行, 若无法避免,则中间需加包地,且包地宽度保证 3~5W 宽度;电源走线与相邻层的其他信号线避免重叠或者平行,但可以是正交的。

DC-DC 电路的输出部分需要先经过滤波电容,然后才能通过过孔传递至各层,且此处的过孔至少要 2~3 个。同时 DC-DC 的反馈走线要尽量短。

各芯片电源输入脚的滤波电容尽可能的靠近芯片,且要尽量保证电容到芯片引脚不再有过孔。

电源输入脚若有多个滤波电容,要按照从大到小的顺序排列,小电容尽量靠近电源输入脚。

同一个电源给多个电路供电的时候, 电源要用星型连接,在星型节点位置放置大电容滤波,尽量使各个供电保持独立。

电源的回路面积要小,回路面积大了容易引起辐射。

电源部分的电解电容需要远离发热大的器件。电解电容随着温度升高其容值会大幅度下降。

186

186

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?