实验目的

帮助学生掌握一位全加器的实现逻辑,掌握多位可控加减法电路的实现逻辑,熟悉 Logisim 平台基本功能,能在 logisim 中实现多位可控加减法电路。

实验内容

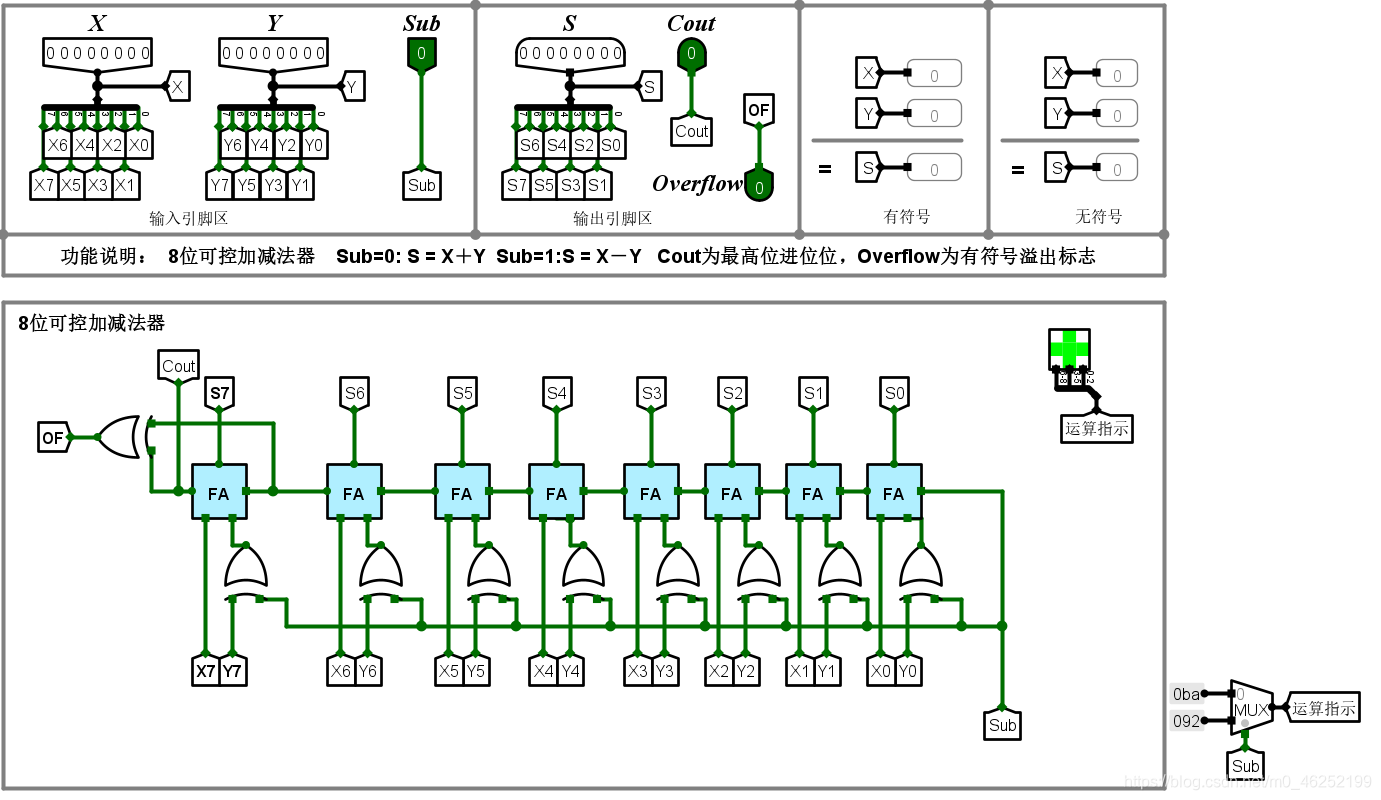

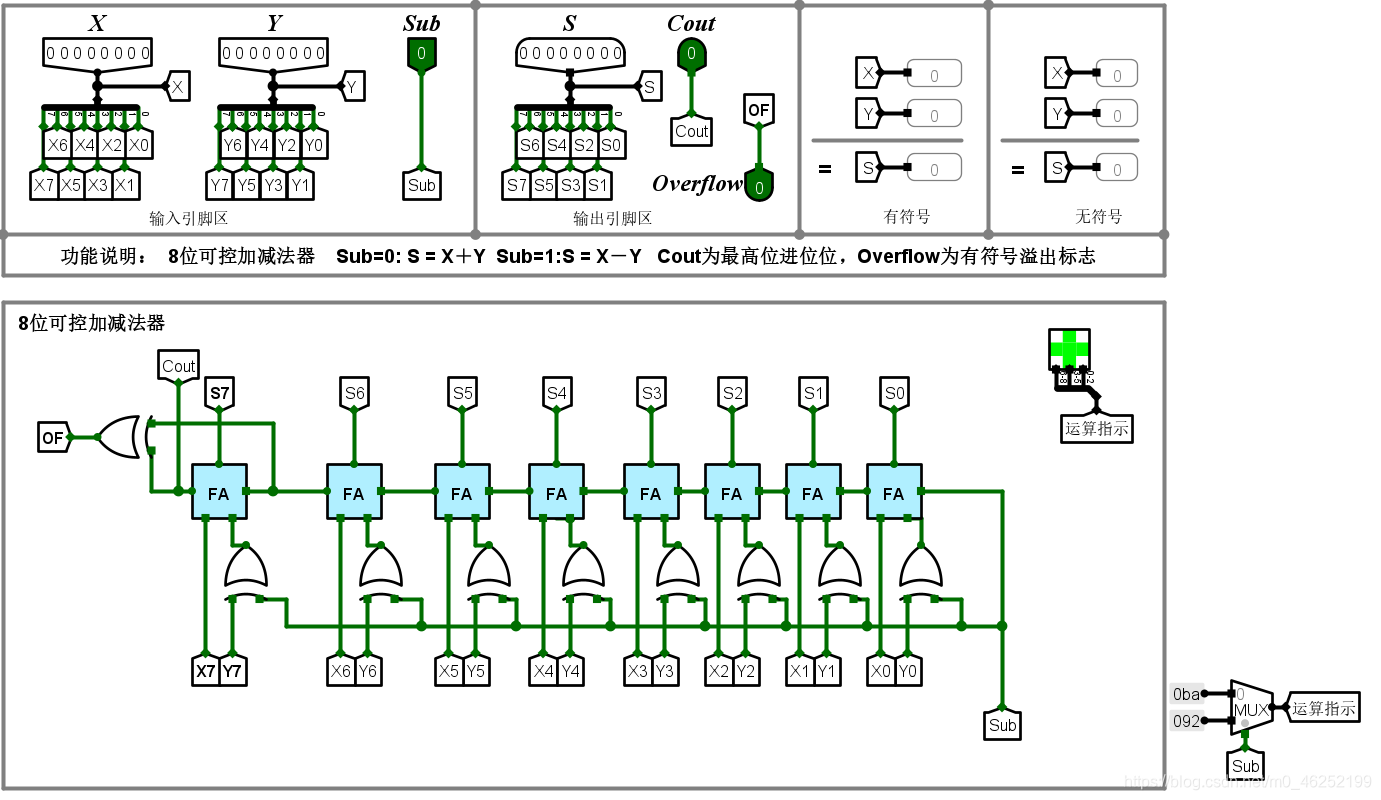

在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,其电路引脚定义如图所示,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。

解答:

实验目的

帮助学生掌握一位全加器的实现逻辑,掌握多位可控加减法电路的实现逻辑,熟悉 Logisim 平台基本功能,能在 logisim 中实现多位可控加减法电路。

实验内容

在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,其电路引脚定义如图所示,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。

解答:

1251

1251

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?