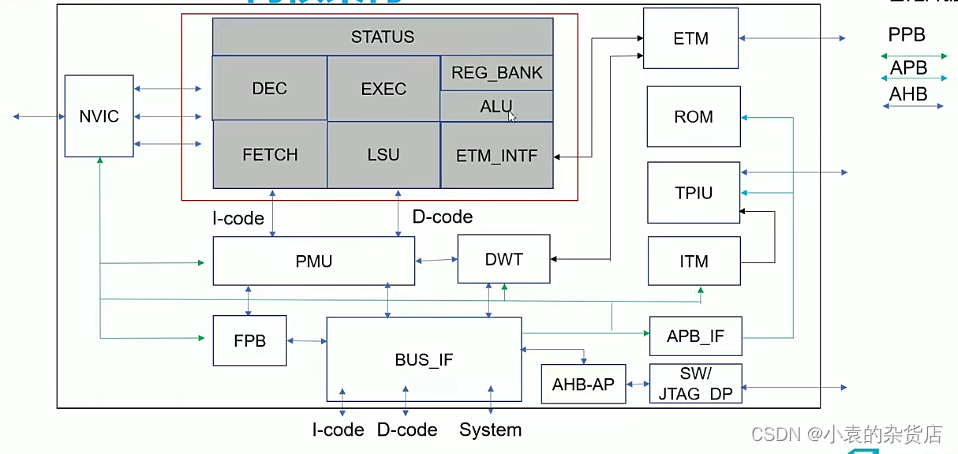

内核整体架构

core内部总体的一些特点。

1. m3支持thumb16和thumb2,thumb32是32位,thumb2是16位的。

2. 哈佛结构。指令和数据分开。

3. 3级流水。

4. 两套堆栈,一套用户使用,一套previledged。

5. 支持大小端。

6. 支持非对齐操作。在bus_if中做的处理。

MPU单元

1. 可以将mpu分成,8个内存区域,针对不同的优先级的用户访问。

2. 8个区域还可以细分内存区域,用于不同的优先级的用户访问。

3. bufferable(只到达寄存器后认为指令完成了,mpu之后在通过硬件搬运到bus_if,相当于可以加速指令的完成速度)和read only region

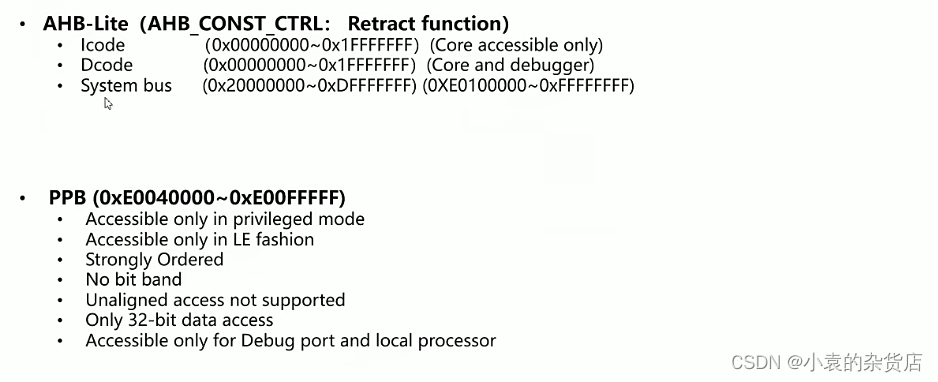

总线接口:

1. 和外部通信主要使用icode,dcode,systembus

2. ppb bus主要用于内部的调试单元的连接,ppb总线只能在特权模式下访问。只有小端模式。

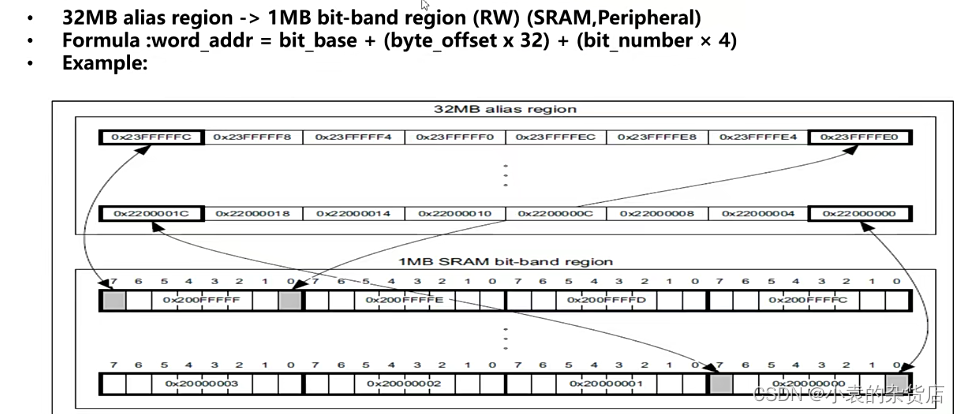

3. bit band 操作

4. 硬件自动地址对其。

5. bufferable

6. icode和dcode是对应的是rom的地址(0.5g)。system bus包括了sram地址,外设地址,外部存储器地址等。

icode只能core访问。dcode只能core访问和debugger 单元访问。

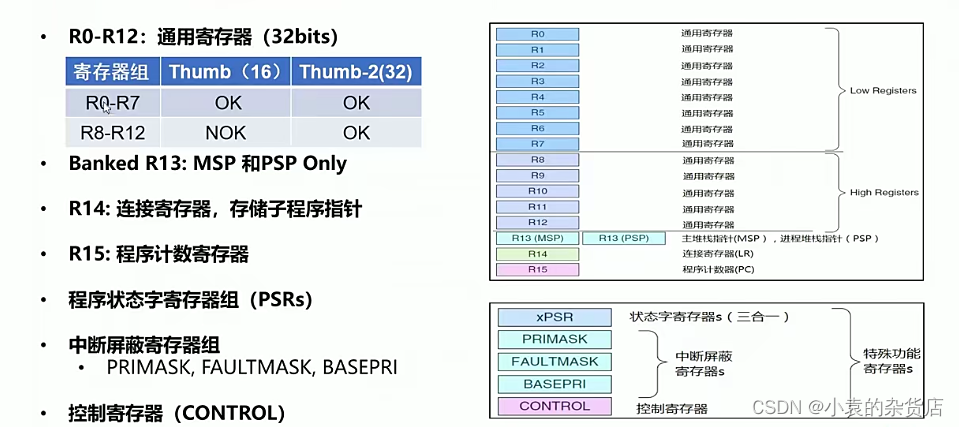

内核寄存器

一共13个32bit通用寄存器,如果指令是thumb16的话,只有0~7寄存器可以用。如果是thumb2的话都可以使用。r13主要用于堆栈指针。两个堆栈主要用于特权模式和用户模式的时候是用不同的堆栈。

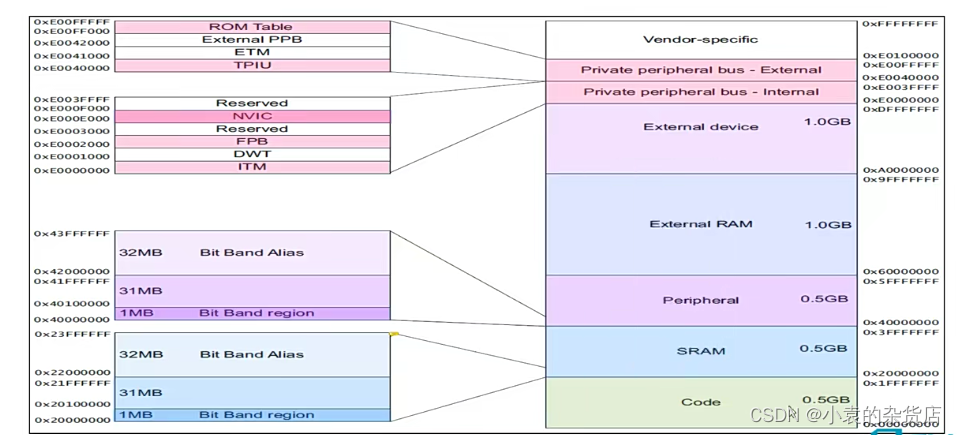

memory map

1. 0.5g给指令rom,0.5g给sram存数据。

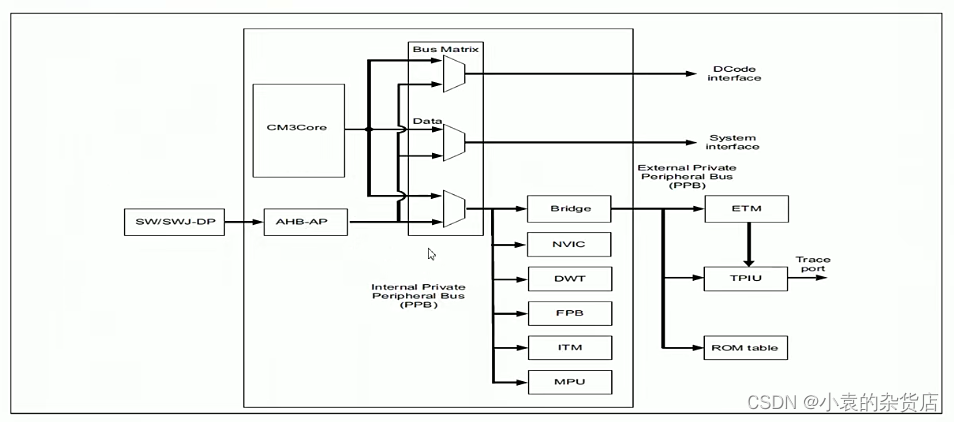

2. ppb总线内部连接了寄存器(内部调试组件)nvic,fpb,dwt,itm;外部连接(外部调试组件)etm,tpiu,external ppb等。可见ppb主要连接调试单元。

3. bit band:其实就是在bit band region里面每一个bit,对应了32M里面的一个word。之前如果想要把地址2000_0000的bit0置位1,之前的办法就是将2000_0000 l中的数据oad 到通用寄存器如r7,在进行运算操作or或者and指令将bit0变成1在store到2000_0000这个地址,使用了软件很麻烦。现在通过bit band只需要将alias region中的2200_0000这个地址的bit0写1就行,写不写其他位都无所谓。

时钟

下面3个时钟为同步

FCLK:free running clk,不被门控,主要用于中断接收和debug。低功耗不停时钟。

HCLK:主时钟

DAPCLK:ahb-ap组件的clk,调试时钟。

下面的时钟都为异步时钟,外部送入。

traceclkin: tpiu组件的输入时钟和fclk异步,所以tpiu组件内部有异步fifo

dbgclk:sw-dp debug clk

tck:jtag时钟

stclk:systick的参考输入

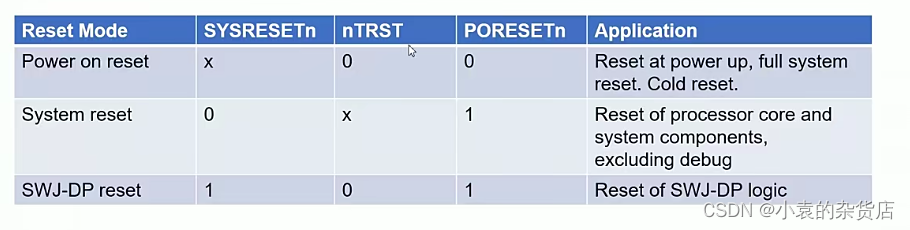

复位

poresetn: 全局复位,除了jtag。

sysresetn: 只复位处理器,nvic,fpb,dwt,itm,ahb-ap不复位

ntrst:jtag复位

上面的图表示:

1. ntrst和poresetn都复位了,那么m3所有的部件全部复位。冷复位。

2. core的复位看sysresetn,但是要保证poresetn不能复位。

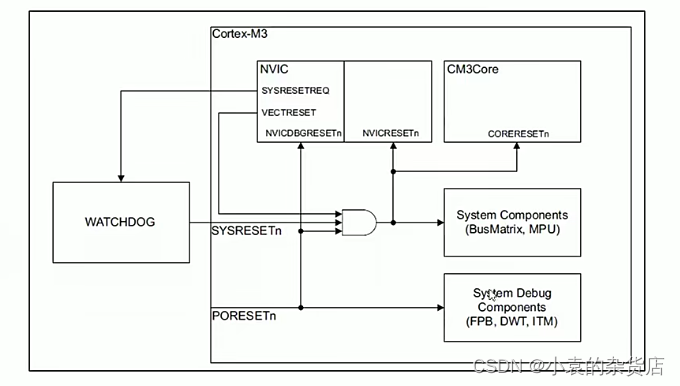

下面是复位系统图。

wdt复位只是复位system,不会复位debug等模块。wdt饿死了可以只是送出中断,或者直接复位。

调试单元结构图

1. ahb_ap可以访问所有的空间,包括调试空间和系统空间。

2. nvic,dwt,fpb,itm,mpu为内部组件;etm,tpiu为外部组件。

3. core和ahb_ap(外部jtag)都可以通过arbitor访问调试组件,说明可以在程序运行的时候进行一些online的debug。

fpb单元

提供Flash 补丁和断点(FPB)单元具有两个功能:

1. 提供硬件断点特性。提供处理器内核的断点事件,触发暂停模式或调试监控异常等调

试模式。断点功能理解起来相对简单:在调试期间,可以在程序地址或数据地址处设置一个或多个断点。若执行了断点地址处的程序代码,则会触发断点调试事件并暂停程序执行(暂停模式调试)或触发调试监控异常(若使用调试监控)。之后就能检查寄存器的内容、存储器和外设,并可以利用单步进行调试等。

2. 通过将CODE区域内的存储器访问映射到SRAM区域(存储器空间的下一个0.5GB),实现对指令或数据的补丁。Flash补丁功能利用系统中的一小块可编程存储器为无法修改的程序存储器打上补丁。对于大量生产的产品,使用掩膜ROM 或可单次编程的 ROM 会降低产品的成本。不过,若在

设备编程后发现了软件问题,要重置这些设备可能需要很高的成本。若增加一小块可编程的存储器(如Flash或可电擦除可编程只读存储器 EEPROM),则可以修改设备中编程的软件。

FPB可用于断点的生成,也可用于 Flash 补丁,不过无法同时使用。若某设备的 FPB 被

配置为Flash补丁,则在运行时连接调试器后Flash补丁的配置会被调试器覆盖。

DWT 数据监视点和跟踪单元

DWT中存在最多4个可产生数据监视点,DWT 具有多个不同功能。

1. 产生调试事件

数据检测点产生可以暂停处理器或触发调试事件,调试事件送到ETM,ETM用调试事件产生 ETM 触发(引起 ETM 在指令跟踪流中发送触发包),包中可能会包含数据值、数据地址或当前PC值。

2. 异常跟踪

DWT可以在进入和退出异常时产生一个跟踪包,这个跟踪包确定产生的是哪个异常,这对调试非常有用。结合ITM中的时间戳包,甚至可以计算出处理器在每个异常所花费的时间。

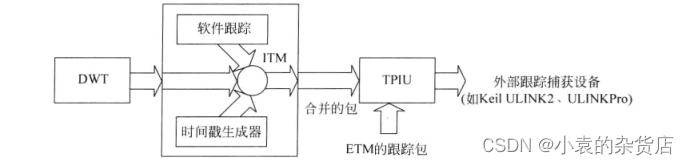

ITM

ITM具有多种功能:

1. 软件跟踪。软件可以直接往ITM激励端口寄存器写入消息,ITM会将数据放在跟踪包并通过跟踪接口输出。

2. ITM还具有跟踪包合并的功能,会将DWT、激励端口和时间戳生成器产生的跟踪

包合并。ITM中还有一个小的 FIFO,它可以降低跟踪包溢出的概率。

ahb_ap

对于调试主机和 Cortex-M3/M4 系统间的基本数据传输,因为接口不同而不能直接进行,所以需要进行接口转化,AHB-AP为调试接口模块(sw/swj_dp)(JTAG调试端口)和Cortex-M3/M4存储器系统间的桥接。它是小端传输的。调试主机通过jtag协议写寄存器ahb_ap中的寄存器然后命令通过ahb的形式发出到Cortex-M3/M4 系统。

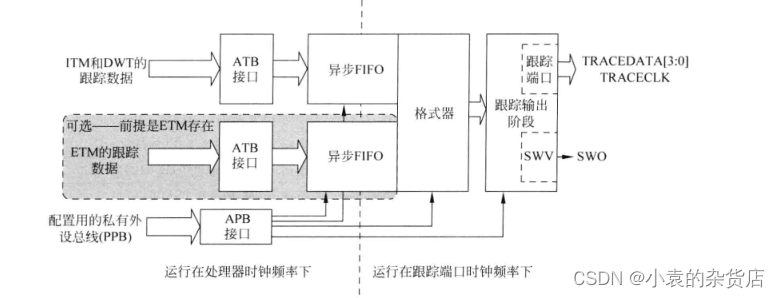

tpiu

TPIU用于将ITM、DWT 和 ETM 的跟踪包合并后进行格式整合输出到外部捕获设备(如 Keil ULINK2/ULINKPro)。apb接口进行配置用于对应外部同步的调试仪器,比如不同的调试仪器会使用打包后的不同长度的包之类的。异步fifo用于两边不同时钟域的跨时钟传递。

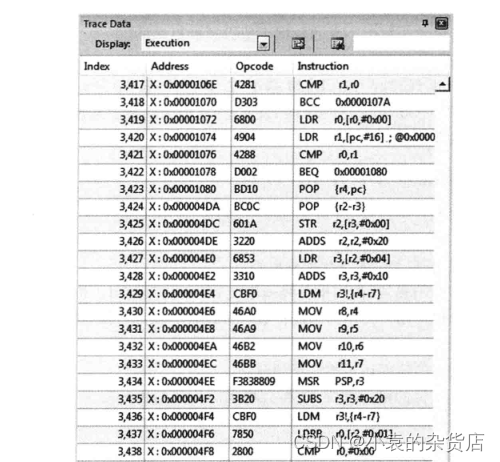

etm

ETM用于提供指令跟踪,它是可选的。在其使能后,它会生成指令跟踪包。FIFO位于ETM中,TPIU可以对跟踪数据包进行串行化处理。下图为 Keil uVision调试器的指令跟踪显示的信息,从图中看,etm对使用的指令进行了跟踪和打包最后送到了TPIU。

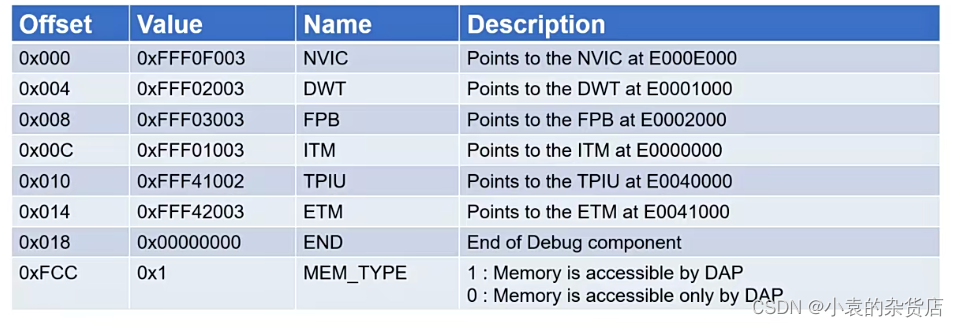

ROM表

m3是一个可能有多个调试部件的复杂片上系统设计。为了帮助调试工具确定调试系统中的调试部件,ROM表被加入进来,它提供了调试组件的地址。调试之前,如果某一个调试组件被使用,这个时候设计者就可以将它的地址写入数据,调试者通过查询寄存器就知道本核使用了哪些组件。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?