低功耗设计方法学(3)

本节学习一些UPF的描述,这些描述是实际项目最最使用的。

Level shifter

- 从高电压到低电压不需要LS,反之需要。

- 时钟需要专门的LS。

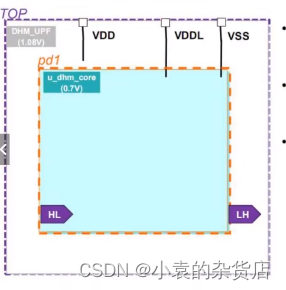

- 图1中蓝色部分就是LS。

图 1

举例描述:图1左下角LS

set_level_shifter pd1_Lsin -domain pd1

-applies_to inputs

-rule high_to_low

-location self

举例描述:图1右下角LS

set_level_shifter pd1_Lsout -domain pd1

-applies_to outputs

-rule low_to_high

-location parent

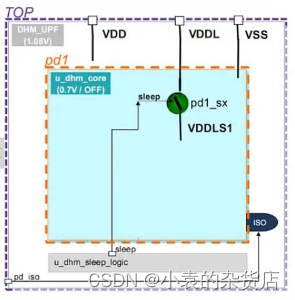

Isolation

- 如果在工艺库中没有对应的ISO,会插入GTECH。

- 时钟net和don’t touch net不能插入iso。

- set isolation 和set isolation control需要成对使用。

图 2

UPF描述:

set_isolation pd1_iso

-domain pd1

-isolation_power_net VDD

-isolation_ground_net VSS

-clamp value 1 //掉电保持1

-applies_to outputs

set_isolation_control pd1_iso

-domain pd1

-isolation_signal pd_iso

-isolation_sense high //高开启iso有效

-location parent

-source 和-sink

假如pd1和pd2都有信号进入pd0,但是pd0和pd1同开同关不需要加iso,但是p0和pd2之间需要加iso,这个时候需加-source (一个属于pd2的supply set )进行区分。

假如pd0有信号进入pd1和pd2,但是pd0和pd1同开同关不需要加iso,但是p0和pd2之间需要加iso,这个时候需加-sink (一个属于pd2的supply set )进行区分。

这样就可以直接避免加多余的iso,面积变大。

UPF描述:

set_isolation iso_mult -domain MULT

-source TOP_p_sset

set_isolation iso_genpp -domain GENPP

-sink Top_p_sset

set_isolation iso_mult -domain MULT

-source TOP_p_sset -sink MULT_p_sset

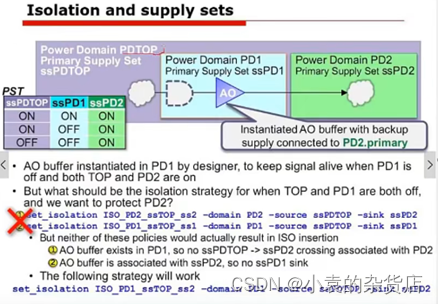

举例说明:分析图3的错误写法和给出正确的写法

图3中,有3个pd,他们的上下电关系在pst里面有描述,可以看到当top on的时候,pd2 on,但是pd1 off,这会导致信号无法从pd1穿过,所以需要在pd1中假如aon_buffer,它的供电来自pd2,又因为当top off 的时候,pd1 off,需要加入iso才不至于x态传播到pd2。

第一种写法错误在于不存在pdtop到pd2的直接通路,中间有buffer,所以无法插入。

第二种写法错误在于aon_buffer由pd2供电,通路应该是到pd2,但是最后却是-sink sspd1

所以:set_isolation iso_pd1_sstop_ss2 –domain pd1 –source sspdtop –sink sspd2 才是正确写法,iso和aon_buffer的供电是-sink后的pd2来供电。

图 3

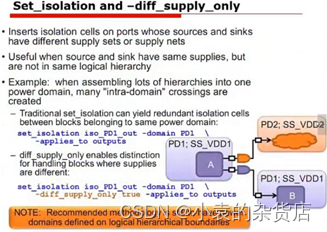

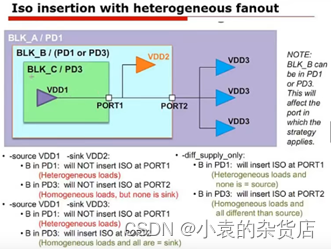

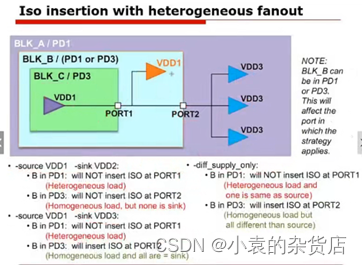

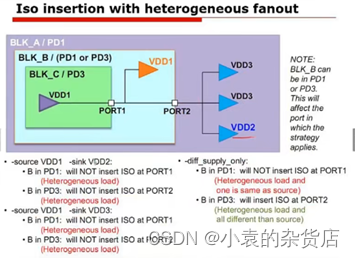

-diff_supply_only

如果有multi load的情况,当load和drvier不同的时候才需要加iso,相同的pd之间,不需要加iso。下图中两个pd1之间不需要添加iso。使用了-diff_supply_only之后,就只会在pd1到pd2加iso。

图5中可使用-diff_supply_only在port1和port2都加iso

图6中可使用-diff_supply_only在port2加iso,port1相同所以无法加iso

图7中可使用-diff_supply_only在port2加iso,因为port2左边接的VDD1,右边接的是VDD2和VDD3。

图 4

图 5

图 6

图 7

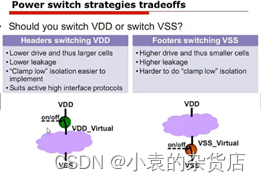

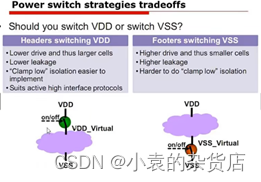

Power switch

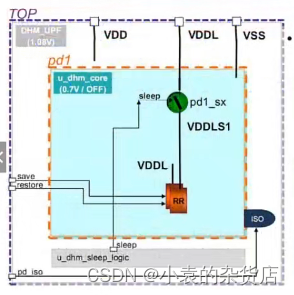

Ps分为header ps和footer ps,一般使用header ps,主要是header ps可以“0”打开比较方便实现。Ps有两个晶体管,一个叫mother,一个叫dauater,两个&起来是打开ps,两个或起来是关闭ps,mother比dauter先置位。图9为例题。

图 8

图 9

create power switch pd1_sx

-domain pd1

-input_supply_port {in VDDL} //in 需要从lib里面去找

-output_supply_port {out VDDLS1}//out 需要从lib里面去找

-control_port {sleep u_dhm_sleep_logic/sleep } //sleep 需要从lib里面去找

-on state {on in {!sleep}} // {state name input_supply_port {布尔表达式}},这里只有一个控制,但是实际项目会有两个控制,Mother和dauter两个。

State retention

主要是retention register,他可以在掉电的时候保持住一个数值,用于对后面电路的控制。图10为例子对rr进行upf描述。

图 10

set_retention pd1_ret

-domain pd1

-retention_power_net VDDL

-retention_ground_net VSS

set_retention_control pd1_ret

-domain pd1

-save_signal {save high} //save 高有效

-restore_signal {restore high} // restore 高有效

map_retention_cell pd1_ret // map对应你的lib

-domain pd1

-lib_cell_type RDFFSRX1

6056

6056

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?