低功耗设计方法学(4)

pst

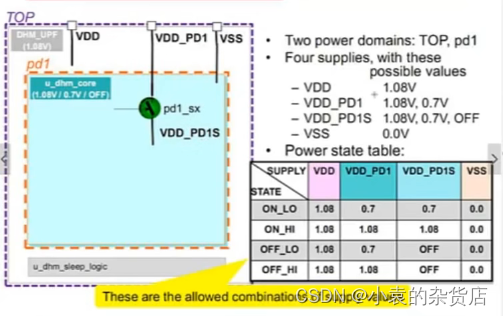

在upf中,使用pst来定义每个pd之间的电压关系,工具也使用pst来检查isolation rules,leve shifter rules是否完全或者冗余。pst不在simulation中使用。

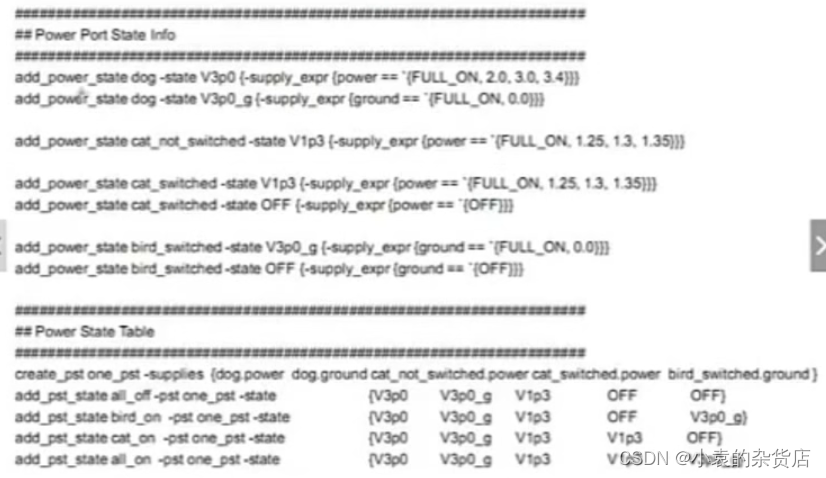

使用supply nets 定义pst(upf1.0)

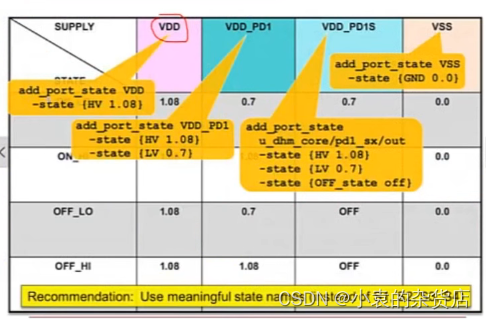

根据要求我们可以得到上图的表格,但是我们需要使用upf的语言将它表现出来。

1. add_port_state <port name>

{ -state { name <nom> | <min nom max>| <off> }} //可以多次使用-state

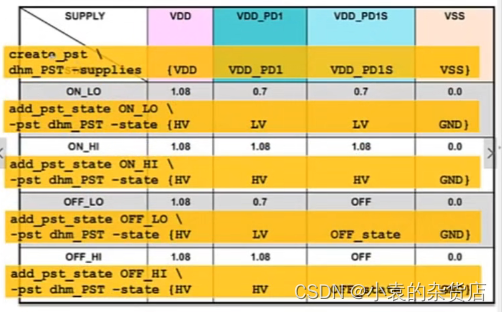

2. create_pst <table_name> -supplies {list}

3. add_pst_state <state_name> -pst <table_name> -state <supply_states>

2和3的命令一起使用。可以得到下面的pst 。*通配符表示无论什么情况都可以。

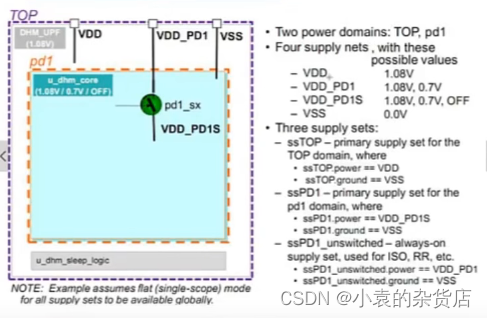

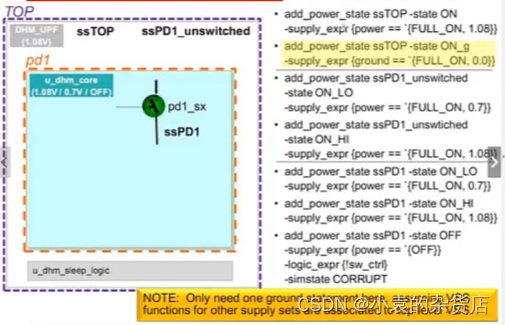

使用supply set 定义pst(upf2.0)

和上面的一样,首先需要有定义的3个supply set。

add_power_state <object_name> -state state_name

[-supply_expr {boolean_function}] //关键字FULL_ON和OFF

[-logic_expr {boolean_function}]

[-simstate simstate]

下面是一个实际的pst例子使用upf2.0编写。

注意下面第三排文字对V3p0_g的定义,他虽然是ground,但是需要定义FULLON,但为0

简单examples

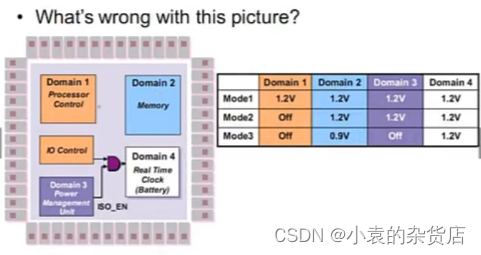

1. 下面的这个图有什么问题?

答案:iso_en来自的pd不能断电。但是pd3会断电。

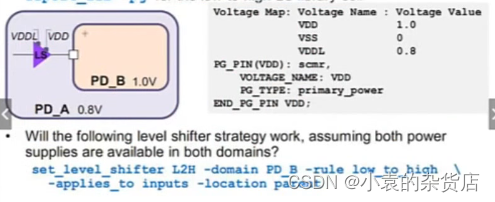

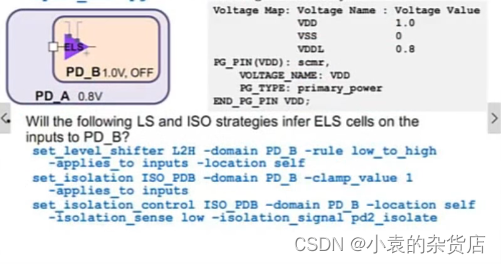

2. 下面的upf描述有什么问题?

答案:-location应该接self,而不是parent,因为-damian的PD_B

3. 下面的upf描述有什么问题?

答案:一般的iso从off到on的pd,但是pd_b中会有off的时候,当off的时候,这个iso中的数据就从on到off,这是不合规的。而且,上图中的els的电源一边实在会掉电的pd_b,这也是不合规的。

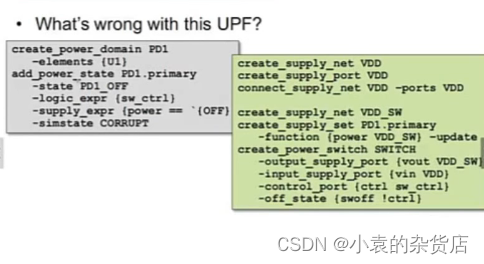

4. 下面的upf有什么错误

答案:-logic_expr {sw_ctrl} 和-off_state {swoff !ctrl} 不一样。所以这是错的。

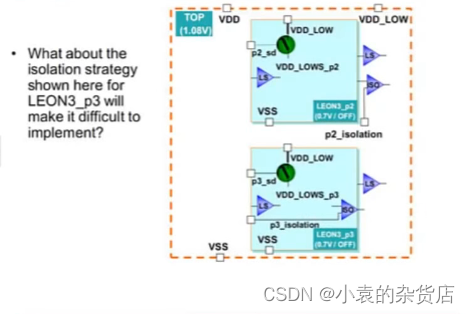

5. 下面两个图中对iso的控制错误的是?

答案:第二个图对iso的控制出错,应该把iso的控制放在TOP而不是在p3内部。

综合练习

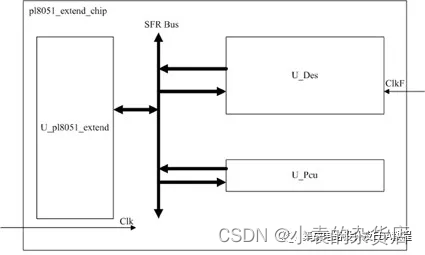

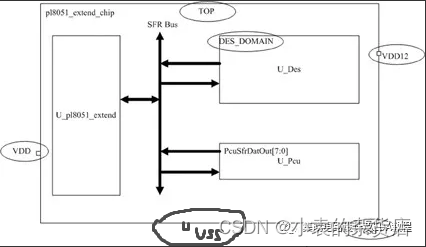

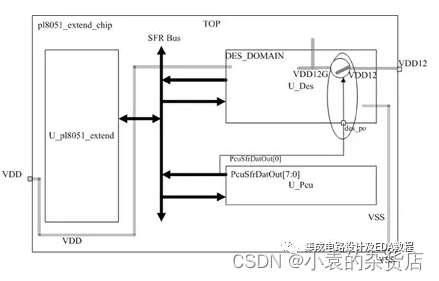

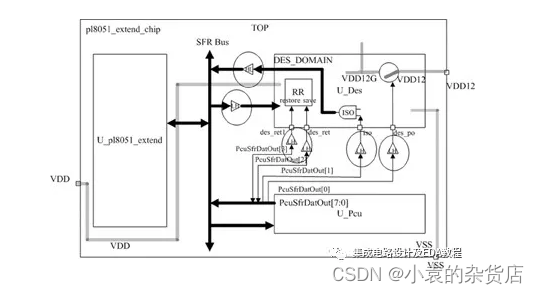

上图中整个设计主要是由一个 8051 控制器,通过 SFR 总线对其他模块进行控制,U_Des 是一个算法模块,U_Pcu 是功耗控制单元。

由于 U_Des 需要在较快的频率下工作,因此需要对 U_Des 进行一些特殊的设计,也就是对整个设计进行低功耗设计,如下所示:

上图主要描述以下信息:

1. 2 个电压域,TOP 以及 DES_DOMAIN。

2. 电源设计外部提供,分 1.2V 的 VDD12 和 1.0V 的 VDD10

3. 设计中除 DES 电路几乎所有电路工作在 1.0V 的 VDD 电压域。

4. U_Des 由于工作速度要求较高,工作在 1.2V 的 VDD12 电压域

DES_DOMAIN,但由于不使用的时候需要关断,以降低静态功耗,因此,通过一组 PowerSwitch 进行控制,控制信号来源为 U_Pcu 的 PcuSfrDatOut[0]输出。该电压域与 TOP 电压域共用 VSS 地信号。

5. 由于 U_Des 电路处于 VDD12 电压域,而 U_Pcu 处于 VDD 电压域,因此需要添加 Level Shifter 进行电平转换。

6. U_Des 电路输出信号,需要通过一个 Isolation Cell,在关断电源时提供稳定电平,而该电平为 1.2V,因此还需要利用 Level Shifter 转换成 1.0V 电压域信号,Isolation Cell 的 Enable 信号来自于 U_Pcu 模块的 PcuSfrDatOut[1]信号。

7. U_Des 电路中的寄存器需要使用 Retention Register,save 和 restore 控制信号分别来自于 U_Pcu 输出 PcuSfrDatOut[2]和 PcuSfrDatOut[3]经过 Level Shifter 产生的信号。

接下来,我们利用 UPF 描述该 DEMO 的功耗设计思路。

4.1 申明电压域以及虚拟电压接口

首先申明电压域,并申明 VDD、VDD12 以及 VSS 等电压端口:

create_power_domain TOP

create_power_domain DES_DOMAIN –elements U_Des

create_supply_port VDD

create_supply_port VDD12

create_supply_port VSS

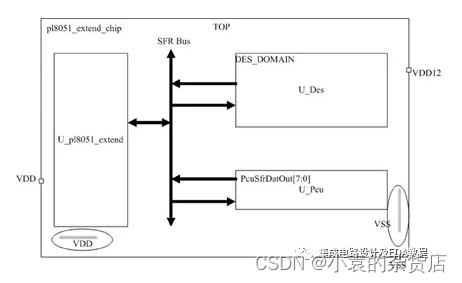

根据上述指令,工具会识别出如下图所示中画圈的信息,电压域及虚拟电压端口开始出现:

需要注意的是电压端口只不过是虚拟存在的,并不是一定在顶层连接。

4.2 申明电源网络

接着申明每个电压域中的电源网络,建议从顶层往底层进行申明,如首先申明 TOP 的 VSS、VDD:

create_supply_net VDD

create_supply_net VSS

以上语句添加下图中画圈部分:

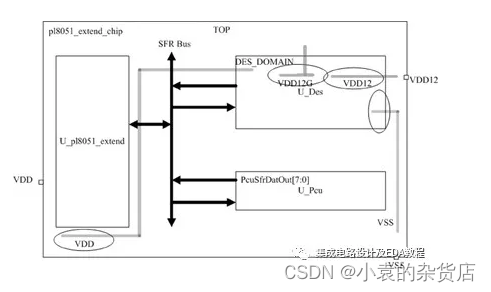

接着申明 DES_DOMAIN 的电源网络,但需要注意的是,如果需要插入 Level Shifter,最好是在与其有连接关系的电源域(TOP)同时申请电源线,并连接起来:

create_supply_net VDD12 //在top中定义VDD12这个线

create_supply_net VDD12 –domain DES_DOMAIN –reuse //DES_DOMAIN 的 VDD12 这根线与 TOP 的 VDD 那根线共用一个网络,因此需要 -reuse

create_supply_net VDD12G //在top中定义VDD12G这个线

create_supply_net VDD12G –domain DES_DOMAIN -reuse

create_supply_net VSS –domain DES_DOMAIN –reuse //之前定义了,所以直接reuse

create_supply_net VDD –domain DES_DOMAIN –reuse //之前定义了,所以直接reuse

以上语句添加下图中画圈部分:

然后将电源网络和电源端口连接起来:

connect_supply_net VDD12 –port {VDD12}

connect_supply_net VDD –port {VDD}

connect_supply_net VSS–port {VSS}

以上语句添加下图中画圈部分。

最后为每个电源域申明主电源网络来源,主电源就是该电压域普通逻辑工作使用的电源:

set_domain_supply_net TOP –primary_power_net VDD –primary_ground_net VSS

set_domain_supply_net DES_DOMAIN –primary_power_net VDD12G –primary_ground_net VSS

做完这一步,电源网络申明基本完成。

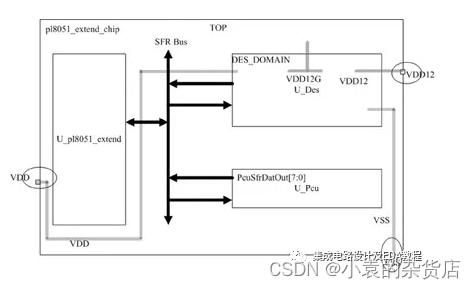

4.3 添加 Power Switch

create_power_switch des_sw

-domain DES_DOMAIN

-input_supply_port {in VDD12}

-output_supply_port {out VDD12G}

-control_port {des_po U_Pcu/PcuSfrDatOut[0]} // des_po为信号名,U_Pcu/PcuSfrDatOut[0]为hirachy

-on_state {state_on in {!des_po}} // {state_on是这里的state in是这里的name {布尔表达式}},这里只有一个控制,但是实际项目会有两个控制,Mother和dauter两个。这里表示!des_po为ps的开启信号。

-off_state {OFF {des_po}}

map_power_switch des_sw

-domain DES_DOMAIN

-lib_cell HDRSIHVTD0

create_power_switch 和 map_power_switch 在综合时只会检查语法,不会有实际效果,但在综合时将该 UPF 指令读入系统,可以由 DC 输出相应的 UPF 给 Synopsys 的 PR 工具,PR 工具可以自动识别这些指令,到时才会真正添加 Power Switch。2 句命令的结果示意在下图画圈中:

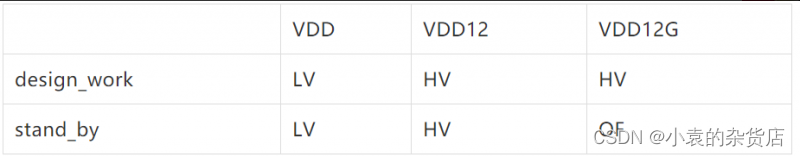

4.4 建立电源状态表格(Power State Table, PST)

在 Power Switch 插入以后,需要对电压域的有效电压,以及不同电压域之间的关系进行设置,同时建立电压分布及关断的情景(scenarios),可以用于静态电压分析、仿真等。

建立电源状态表格,可以参看以下upf描述:

第一步,定义state

add_port_state VDD –state {LV 1.0} #VDD 是 1.0V,属于低电压域(LV)状态

add_port_state VDD12 –state {HV 1.2} #VDD12 是 1.2V,属于高电压域(HV)状态

add_port_state des_sw/out –state {HV 1.2} #Power Switch 输出是 1.2V,属于高电压域(HV)状态,注意des_sw是刚刚定义的ps的名字,out是刚刚定义的ps的电压输出点。

-state {OFF off} #关闭状态(OFF),无电压(off) 再使用一次-state表示另外一种ps的状态为关闭

add_port_state VSS –state {ON 0.0} #VSS 处于常开状态(ON),电压 0V

第二步创建pst

create_pst design_pst –supplies {VDD VDD12 VDD12G} #建立一个 PST,由 3 个电源状态不同组成

第三步增加状态

add_pst_state design_work –pst design_pst –state {LV HV HV} #design_work 状态下,三组电源都开

add_pst_state stand_by –pst top_pst –state {LV HV OFF} #stand_by 状态下,des_sw/out 输出电源为关闭状态

需要注意 add_pst_state 的 -state 括号里的描述顺序,必须与 create_pst 的 -supplies 里一致,选择的状态必须与 add_port_state 的 -state 里描述的一致才可以。

这样就建立了下表所示的 PST,design_pst:

由此建立了 PST,分析工具或仿真工具就知道需要对哪些状态进行分析了。

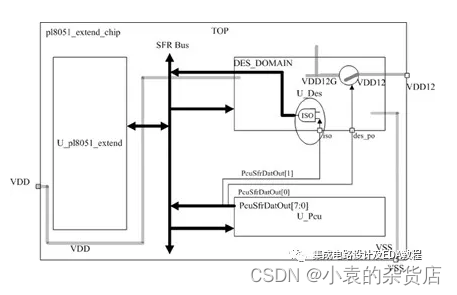

4.5 插入 Isolation Cell

下面需要为 DES_DOMAIN 输出给 TOP 的输出信号添加 Isolation Cell。脚本如下所示:

# Isolation Cell

set_isolation des_iso_out

-domain DES_DOMAIN

-isolation_power_net VDD12 -isolation_ground_net VSS #隔离后只有 VDD12 供电

-clamp_value 1 #关电后输出逻辑 1

-applies_to outputs #对于所有输出添加

set_isolation_control des_iso_out

-domain DES_DOMAIN

-isolation_signal U_Pcu/PcuSfrDatOut[1] //只列出hirachy就可以了

-isolation_sense high #控制信号为高时 ISO 有效

-location self # Isolation Cell 添加在 DES_DOMAIN 里面

这样就可以产生如下图所示画圈部分电路:

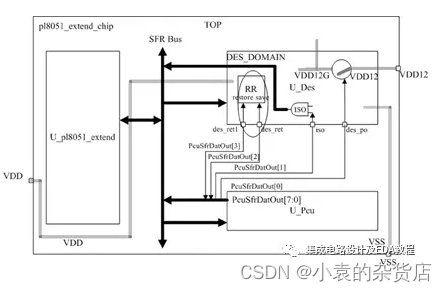

4.6 替换 Retention Register Cell

接着需要使用 Retention Register Cell 将 DES_DOMAIN 中在关断电源后需要保留数据的寄存器替换为 Retention Register Cell,可以使用如下脚本:

# Retention Register

set_retention des_ret -domain DES_DOMAIN

-retention_power_net VDD12G -retention_ground_net VSS #retention_power_net 是关电的 Power,表示需要保持 VDD12G 电源域的数据

set_retention_control des_ret -domain DES_DOMAIN

-save_signal {U_Pcu/PcuSfrDatOut[2] high}

-restore_signal {U_Pcu/PcuSfrDatOut[3] low}

map_retention_cell des_ret

-domain DES_DOMAIN

-lib_cell_type RSDFCSD1

#RSDFCSD1 是带有异步置位的 Retention Register Type,可以从 lib 文件中 retention_cell 属性中看到。

根据以上描述,会按照下图画圈示意图描述电路:

4.7 插入 Level Shifters

插入 Level Shifters 是根据 PST 的定义进行,根据 PST 定义看来,DES_DOMAIN 和 TOP 之间需要插入 Level Shifters,其中 DES_DOMAIN 输出的 pin(Isolation Cell 的输出)需要插入 H->L 的 Level Shifter,而其输入则需要插入 L->H 的 Level Shifter。

插入 Level Shifter 在 Compile 过程中自动进行,也可以利用 UPF 命令 set_level_shifter 定义插入的规则。

# Level Shifter

set_level_shifter des_ls_lh

-domain DES_DOMAIN

-applies_to inputs

-rule low_to_high

-location parent

set_level_shifter des_ls_hl

-domain DES_DOMAIN

-applies_to outputs

-rule high_to_low

-location parent

插入 Level Shifter 后产生的电路变化示意图如下图画圈处所示:

本文详细介绍了低功耗设计方法学,包括UPF(统一电源格式)1.0和2.0中定义电源状态(PST)的方法,如使用`add_port_state`、`create_pst`和`add_pst_state`等命令。通过示例展示了如何使用UPF创建电源开关、电源状态表格、IsolationCell、RetentionRegisterCell以及LevelShifter,并强调了在设计中应注意的问题,如电源网络的申明、电源状态的合规性和控制信号的正确配置。

本文详细介绍了低功耗设计方法学,包括UPF(统一电源格式)1.0和2.0中定义电源状态(PST)的方法,如使用`add_port_state`、`create_pst`和`add_pst_state`等命令。通过示例展示了如何使用UPF创建电源开关、电源状态表格、IsolationCell、RetentionRegisterCell以及LevelShifter,并强调了在设计中应注意的问题,如电源网络的申明、电源状态的合规性和控制信号的正确配置。

2826

2826

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?