Hi,大家好

Axi总是面试的热点问题,axi也是低端和高端芯片的分水岭,本专题从axi协议开始讲解,最后会使用axi做接口实现一个axi接口的双端口ram并验证,实现代码为verilog。本专题会一直更新,直到我找到下一份工作,可能会很久,不过要随时保持战斗力的方法就是随时学习和随时熟悉。首先我们开始了解axi的常用的接口信息,首先说明不常用的信号不实现,也不会实现,不过大家需要熟悉的知道不常用信号的含义才能在工作中才能游刃有余。

AXI4与AXI3之间的不同之处

从读写两个通道来看看相比AXI3,AXI4中都做了哪些修改。(对于下面的接口信息,我会在本专题的第二节进行阐述,大家也可以查阅资料提前了解)

一.写通道

1. axi4的AWLEN位宽更大。axi3的AWLEN是4bit,axi4的AWLEN是8bit。因此AXI4可以产生比AXI3更长的写burst。

2.axi4的AWLOCK缩减到1bit了。这样可以兼容exclusive传输,但是不支持locked传输。

3.axi4增加了AWQOS信号。这个信号支持quality of service。

4.axi4增加了AWREGION信号。这支持通过一个物理slave接口访问不同的slave。

5.axi4删除了WID信号。这样axi4不支持out of order 和 interleave。

6.axi4增加了用户自定义信号。

二.读通道

1.axi4的ARLEN位宽更大。axi3的ARLEN是4bit,axi4的ARLEN是8bit。因此axi4可以产生比axi3更长的读burst。

2.axi4的ARLOCK缩减到1bit了。这样可以兼容exclusive传输,但是不支持locked传输。

3.像写通道一样,读通道也新增了ARQOS和ARREGION信号。

axi五大概念,了解之后你就无敌了。

1.burst传输

一次burst传输可以看做一次transaction,包含了length个的transfer,每一次transfer的地址相差size的大小。burst传输只需要master发出首地址,设定length和size就可以自动进行地址增加。burst 传输可以减少地址通道的交互,提升单笔传输的效率。

2.transaction 和 transfer 与ID

在协议中常常提到transaction和transfer。

协议中规定一个完整的burst成为一笔transaction,假设transaction的burst length=5。那么数据通道对于一个transaction来说会有5个transfer。主机发布读写指令时,会同时发布一个ID,这使得每笔transaction都有一个固定ID。从机在向主机返还信息的时候也要与对应的指令ID相同。(这里指B通道R通道,R通道上一笔transaction中的所有transfer共享一个ID)

3.outstanding

outstanding传输是指不需要等待前一笔传输完成就可以发送下一笔操作,这样可以有效提升通路利用率,提升系统性能,outstanding 可以减少多笔传输之间的等待,提升多笔传输的效率。

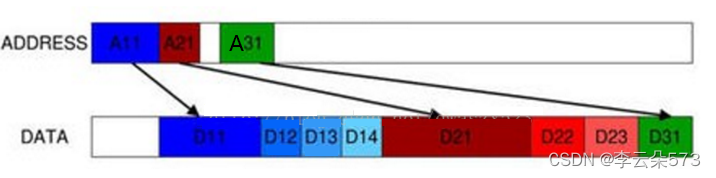

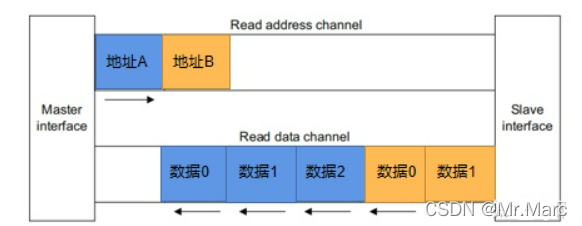

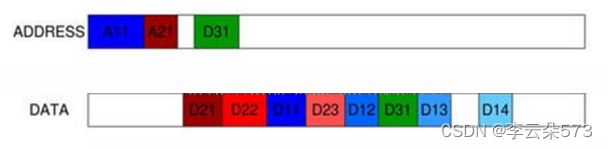

如上图,主机先发送出第一个指令A11。A11指令需要传输4个transfer(D11-D14)。但在这4个transfer为传输完成之前,主机又发布一个新的指令A21。这样的行为成为主机发起一个outstanding。进一步说明,读Outstanding操作是不需要等待前一笔传输完成就可以发送下一笔操作。AXI因为是通道分离的所以master不需要等待前一笔操作A响应完成就可以发送下一笔操作请求B,这样可以有效提升通路利用率,提升系统性能。

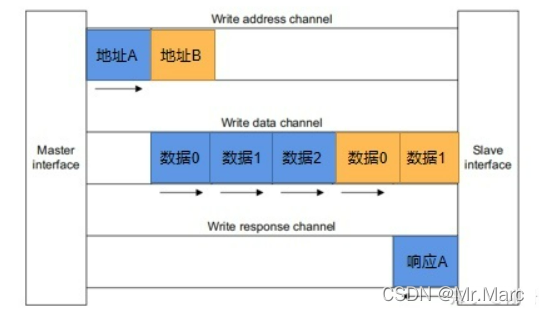

写outstanding也是一样,不需要等待前一笔的写完成就可以发送下一笔传输。系统设计上需要注意outstanding对应的缓存的需求,否则无法接受master发送的数据出现系统的反压。

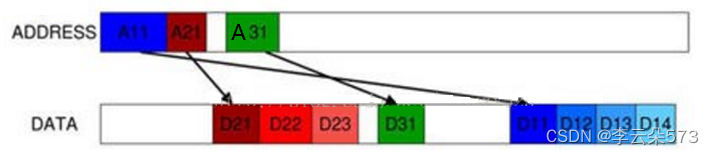

4.out of order 乱序

AXI4取消了W通道的ID,所以这里以R通道举例。主机以A1121A31的顺序发出三笔读传输请求。但是数据的返还顺序并没有按照指令的发布顺序返回(这里按照了D2D3D1的顺序),这样的行为称为out of order乱序传输。

需要注意的是,如果三次指令的ID都相同,那么最终返还给主机的数据也必须keep order(需要interconnect做出支持),因为ID相同如果out of order接收一方无法分辨哪个transaction属于哪个指令。(interleaving也一样)

在这里增加一个概念:

ID扩展:如果在很多master的情况下,有一个master发出一个带原始ID的transaction,在外部对其进行ID扩展。然后到达slave。Slave处理transaction并返还response。这个response带有的ID信息也是那个经过扩展的。这个response会经过各种switch最终到达正确的master。(扩展ID就是为了在多master的复杂拓扑结构中让从机返还的信息找到正确的master)

5.interleaving 间插

AXI4取消了W通道的ID,所以这里以R通道举例。主机以A1121A31的顺序发出三笔读传输请求。但是从机数据的返还并不是以整个transaction为单位。属于不同transaction的transfer会相互插入。

axi 握手机制

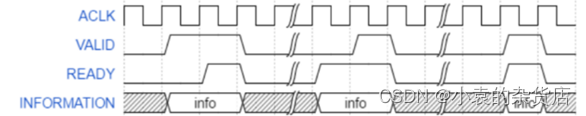

5个传输通道均使用VALID/READY双向握手机制,传输仅仅发生在VALID、READY同时有效的时候。

VALID信号表示地址/数据/应答信号总线上的信号是有效的,由传输发起方控制。READY信号表示传输接收方已经准备好接收,由传输接收方控制。

下图是几种握手机制:

VALID和READY的先后关系具有三种情况:

VALID先有效,等待READY有效后完成传输(VALID一旦有效后在传输完成前不可取消);READY先有效,等待VALID有效后完成传输(READY可以在VALID有效前撤销);VALID和READY同时有效,立刻完成传输。需要注意的是允许READY信号等待VALID信号再有效(图中第一种情况),即使从机准备好,也可以不提供READY信号,等到主机发送VALID信号再提供READY信号。注意:不允许VALID等待READY信号拉高后再拉高,否则容易产生死锁现象。

命令通道握手(AR,AW,B)

- 仅当地址等信息有效时,才拉高VALID,该VALID必须保持直到传输完成(READY置位),READY默认状态=0,仅当准备好接收时拉高READY。

数据通道握手(W和R)

- 突发读写模式下,仅数据信息有效时才拉高VALID,该VALID必须保持直到传输完成。当突发传输最后一个数据发送时拉高LAST信号一个周期,READY默认状态=0,仅当准备好接收时拉高READY

通道顺序

传输中,B通道传输必须在A通道完成以后进行,R通道传输必须在RA通道传输后进行且通道之间必须遵循一系列的状态依赖关系来防止死锁具体如下。

- VALID信号不能等READY信号。

- AXI接口可以等到检测到VALID才拉高对应的READY,也可以检测到VALID之前就拉高READY。

读传输握手依耐关系

ARREADY可以等待ARVALID信号,RVALID必须等ARVALID和ARREADY同时有效后(一次地址传输发生)才能能有效;

写传输握手依耐关系

在AXI3中,写操作中唯一的强依赖关系是写响应通道BVALID,仅当WVALID和WREADY信号同时有效(数据传输完成)且WLAST信号有效(突发传输的最后一个数据传输完成)后才会被置位;

在AXI4中,定义了额外的依赖关系,即BVALID必须依赖AWVALID、AWREADY、WVALID和WREADY信号且WLAST信号有效才能被置位;

读写时序

写地址通道:当主机驱动有效的地址和控制信号时,主机可以拉高(置位的意思)AWVALID,一旦拉高,需要保持AWVALID的拉高状态,直到时钟上升沿采样到从机的AWREADY。AWREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来拉高AWVALID,一个用来拉高AWREADY);当AWREADY为高时,从机必须能够接受提供给它的有效地址。

写数据通道:在写突发传输过程中,主机只能在它提供有效的写数据时拉高WVALID,一旦拉高,需要保持拉高状态,直到时钟上升沿采样到从机的WREADY(??时序图上并没有因为wready的拉高而拉低wvalid)。WREADY默认值可以为高,这要求从机总能够在单个周期内接受写数据。主机在驱动最后一次写突发传输是需要拉高WLAST信号。

写响应通道:从机只能它在驱动有效的写响应时拉高BVALID,一旦拉高需要保持,直到时钟上升沿采样到主机的BREADY信号。当主机总能在一个周期内接受写响应信号时,可以将BREADY的默认值设为高。

读地址通道:当主机驱动有效的地址和控制信号时,主机可以拉高ARVALID,一旦拉高,需要保持ARVALID的拉高状态,直到时钟上升沿采样到从机的ARREADY。ARREADY默认值可高可低,推荐为高(如果为低,一次传输至少需要两个周期,一个用来拉高ARVALID,一个用来拉高ARREADY);当ARREADY为高时,从机必须能够接受提供给它的有效地址。

读数据通道:只有当从机驱动有效的读数据时从机才可以拉高RVALID,一旦拉高需要保持直到时钟上升沿采样到主机的BREADY(还是rready)。BREADY((还是rready)??)默认值可以为高,此时需要主机任何时候一旦开始读传输就能立马接受读数据。当最后一次突发读传输时,从机需要拉高RLAST。

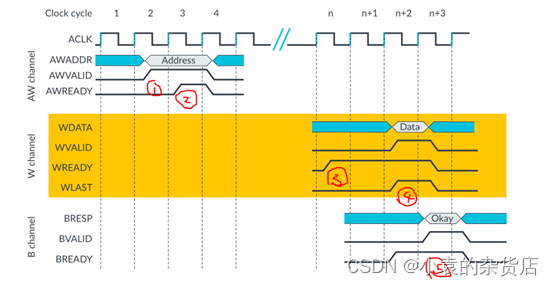

1.单笔数据写

-

- Manager拉高AWVALID同时放地址在AWADDR上

- Subordinate拉高AWREADY握手

- s拉高WREADY

- 过了两个周期之后,MANAGER放数据在WDATA,拉高WVALID,拉高WLAST,拉高BVALID。

- Subordinate拉高BVALID,且发送BRESP给到Manager。

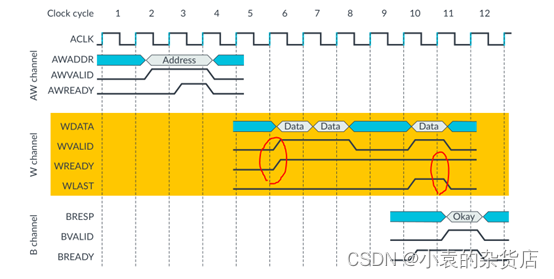

2.BURST写

时序基本和上面一样,需要注意的是,这里的wready和wvalid同时拉高,但是single传输是wready先拉高两个周期,这里不知道有没有影响。而且,m发送了wlast之后wready并没有拉低。

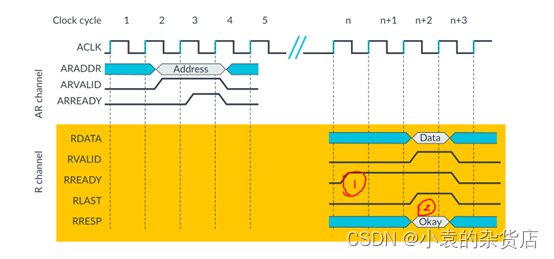

3.单笔数据读

AR channel 和写数据一样的时序。1: M拉高RREADY。2: 过了两个周期,S放数据在RDATA且拉高RVALID和RLAST且发送RRESP。

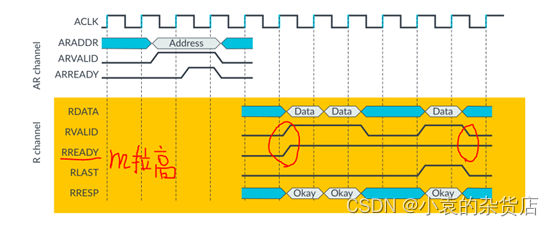

4.Busrt 读

AR channel 和写数据一样的时序。1: M拉高RREADY 且s拉高rvalid且发送数据。2: rlast拉高,rready并没有拉低。注意:这里每读一个数据,s都会发送resp给到m。有个问题,怎么保证rvalid和rready同时拉高??

371

371

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?