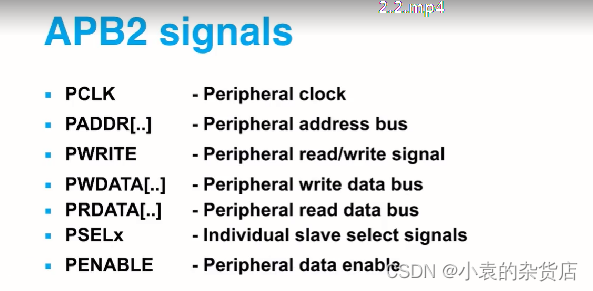

APB2的接口和两个问题:

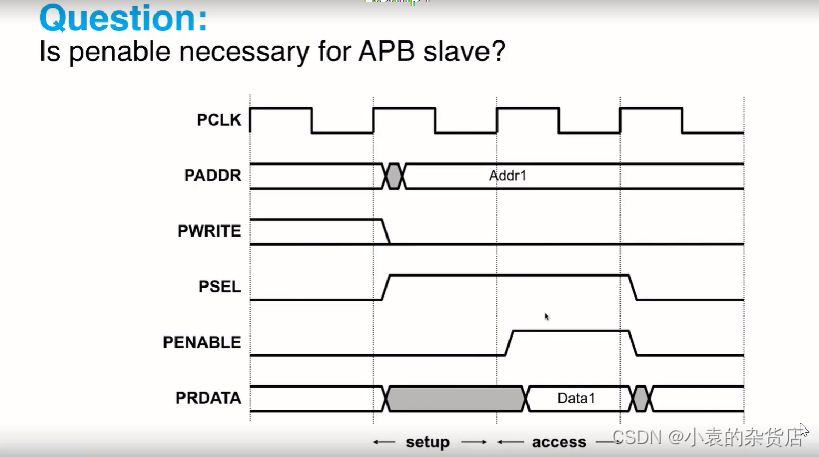

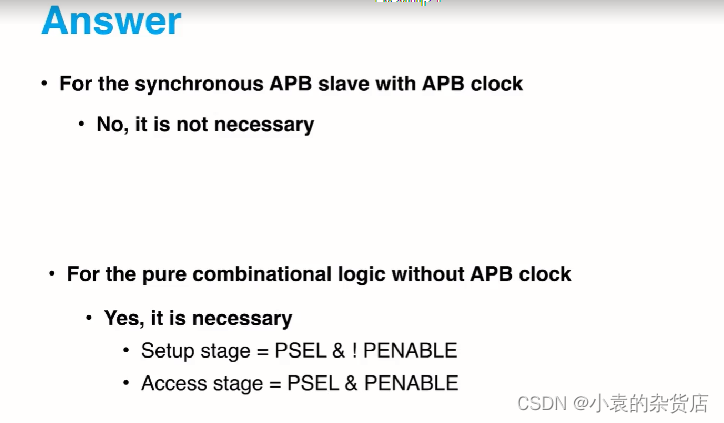

问题1

有pclk时钟的话那么penable就不是必须的;

如果使用全组合逻辑的话,penable就是必须的,可以节省一点功耗。

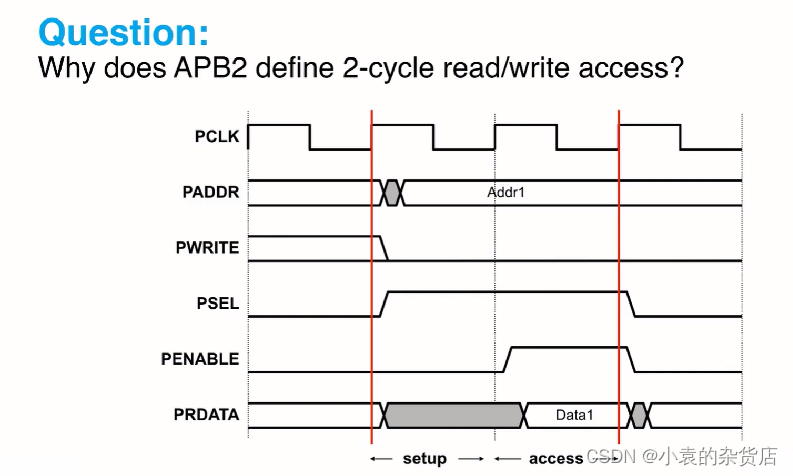

问题2

Apb2中没有握手pready信号,只有通过软件的轮询去查询外设是不是ready,在状态寄存器里查询,如果ready了再写寄存器,所以对于写寄存器两个周期足够了。

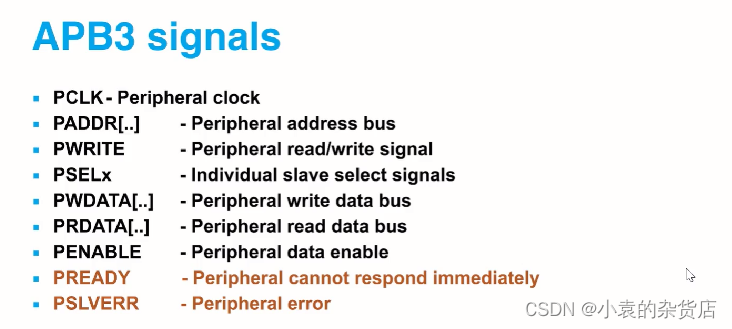

APB3的接口

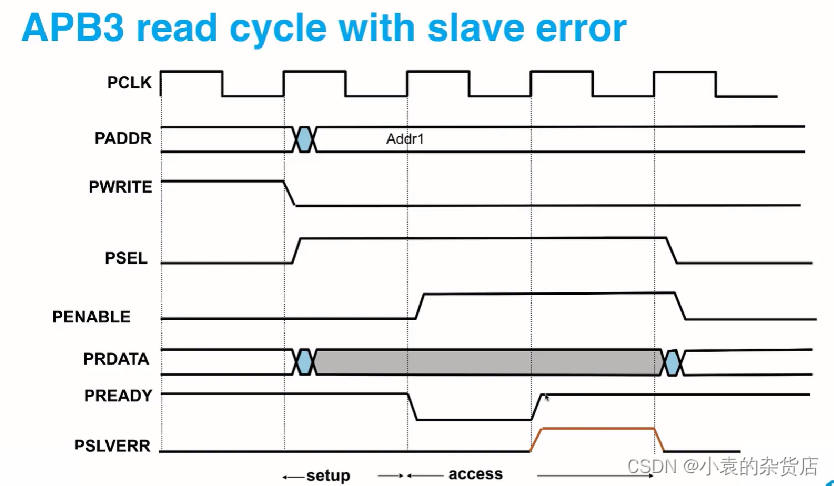

注意PSLVERR的拉高时间是当PSEL,PENABLE以及PREADY 都为高时,PSLVERR才在最后一个周期进行判断。如下图。

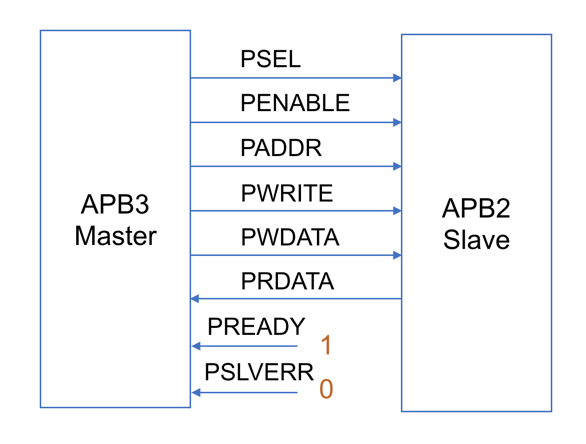

如果是APB3的Master,APB2的slave,只需要将PREADY绑定为1,PSLVERR绑定为0即可,如下图所示:

如果是APB2的master和APB3的slave相连接,会比较麻烦一点,因为APB2的master要求和它相连的slave会在access阶段的时候就要把读数据给它,但是APB3的slave因为有pready的情况下,可能没办法马上给出读数据,所以就比较麻烦了,因此我们不建议这么互联!对于这种情况,最好的方式是把master也改成APB3的master!

APB4的接口

PSTRB[n]对应PWDATA[(8n+7) : (8n)]

PSTRB[3:0]每bit 对应 写数据8bit;高有效;

注意:在读操作的时候,PSTRB必须全部为0

为了实现复杂设计,经常需要对系统中的互联接口和互联设备进行保护保护,以防止非法传输。Cpu可以工作在user模式或者privilege模式,对于支持trustzone的cpu可以工作在normal word或者secure word,可以在有对于APB接口来说,保护功能通过PPROT[2:0]来实现。假如Cpu可以工作在user模式发出PPROT[1]=1(非安全访问)要对外设中PPROT[1]=0(安全访问)的寄存器访问,就会返回pslverr信号。

PPROT[0]:0:正常访问;1:优先级访问;

PPROT[1]:0:安全访问;1:非安全访问;【最主要功能】

PPROT[2]:0:数据访问;1:指令访问;

当同时又数据和指令一起传输时,一般当做数据传输,除非特别指定为指令传输。PPROT最主要的是为了标识安全传输和非安全传输;PPROT[0]和PPROT[2]的含义可以用户重新定义。

Apb4可以参考下面网址:APB4总线介绍_脱密180天的博客-CSDN博客_apb4协议

Apb4的slv连接apb3的mst的话,将apb4 slv的PSTRB全部置1,PPROT根据本slv的安全等级进行置位。Apb3的slv连接apb4的mst的话,要么改Apb3的slv要么做一个转换桥。

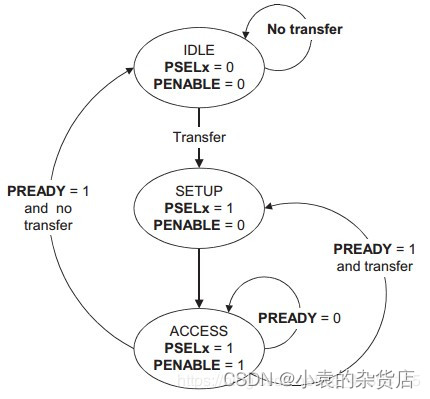

APB(Advanced Peripheral Bus),外围总线。APB属于AMBA 3 协议系列,它提供了一个低功耗的接口, 并降低了接口的复杂性。 APB接口用在低带宽和不需要高性能总线的外围设备上。 APB是非流水线结构,所有的信号仅与时钟上升沿相关,这样就可以简化APB外围设备的设计流程,每个传输至少耗用两个周期。APB可以与AMBA高级高性能总线(AHB-Lite) 和AMBA 高级可扩展接口 (AXI)连接。APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。APB上的传输可以用状态图来说明。

a) 系统初始化为IDLE状态,此时没有传输操作,也没有选中任何从模块。

b) 当传输被请求时,总线进入SETUP状态,选择信号 PSELx被置位。总线仅在SETUP 状态停留一个时钟周期,并在下一个时钟周期进入ACCESS状态。

c) 系统进入ACCESS状态时, 使能信号PENABLE置位。在传输从SETUP状态到ACCESS状态转变的过程中address, write, select和write data信号必须保持不变。从ACCESS状态退出,由从器件的PREADY 信号控制:a) 如果PREADY 为低,保持ACCESS状态。b)如果PREADY 为高,则退出ACCESS状态,如果此时没有其它传输请求,总线返回IDLE状态,否则进入SETUP状态。

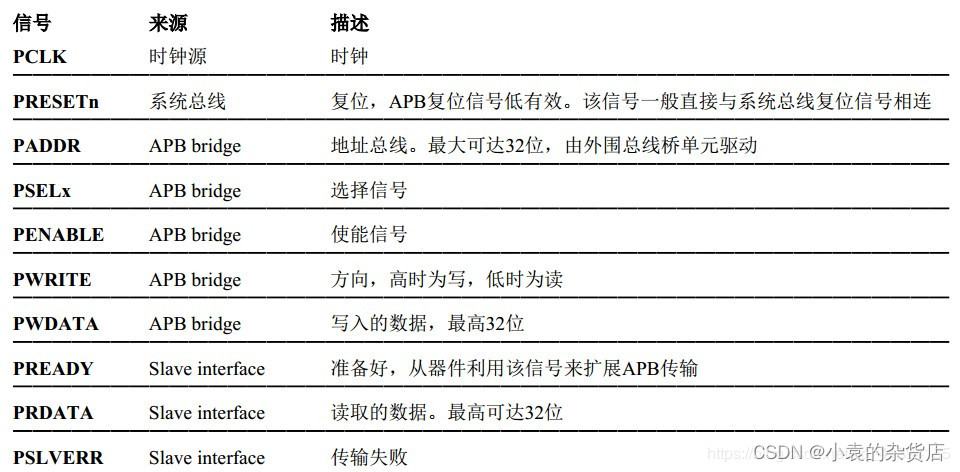

信号描述:

下表给出了APB的信号。APB的支持最大32-bit的数据位宽。APB协议有两个独立的数据通道,读通道和写通道,由于APB的两个通道没有自己的握手信号(vaild/ready),因此两个通道不会同时使用。

除了上表的信号外,APB还有两个信号接口:

PPROT: 保护类型,分为 normal, privileged, secure, data/instruction 访问。

写传输:

写传输包括两种类型:无等待状态和有等待状态。

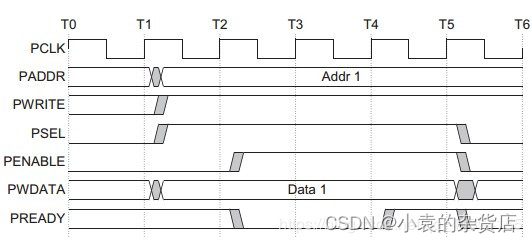

无等待状态:

地址信号、写入数据信号、写入信号和选择信号都在时钟上升沿后改变。T1周期叫做Setup phase。 T2周期使能信号PENABLE被置位,表示Access phase就位。地址、数据和控制信号在Access phase期间有效。传输在该周期后结束。使能信号PENABLE, 在传输结束后清空。 选择信号PSELx同样被置低,除非紧接着下一传输开始。

有等待状态:

下图展示了 PREADY 信号是如何扩展了从器件的传输。

在Access phase期间,当PENABLE为高,传输可以通过拉低PREADY来扩展传输。下述信号仍旧不变:地址(PADDR),写信号(PWRITE),选择信号(PSEL)使能信号(PENABLE)写入的数据(PWDATA)。

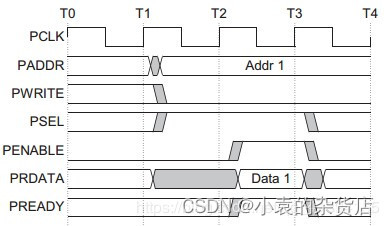

读传输:

无等待状态:

下图显示了一个读传输的无等待状态的时序图。从器件必须在读传输结束前提供数据。

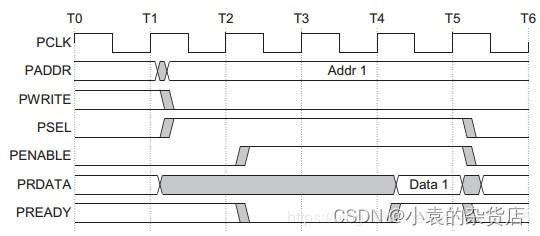

有等待状态:

下图显示了信号是如何扩展传输的。如果在Access phase期间PREADY信号拉低,则传输被扩展。但下述信号不变:地址(PADDR),写信号(PWRITE),选择信号(PSEL)使能信号(PENABLE)。图中显示了如何使用PREADY信号来添加两个周期,你也可以添加数个周期。

错误响应:

使用PSLVERR来指示APB传输错误。当PSEL,PENABLE以及PREADY 都为高时,PSLVERR才在最后一个周期进行判断。当任何一个PSEL, PENABLE或者PREADY为低时,你可以将PSLVERR拉低,这是推荐,并不是强制要求。APB外围设备不要求必须支持PSLVERR引脚,当不使用该引脚时,应被置低。

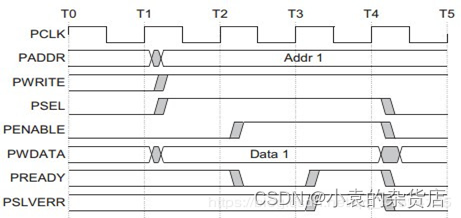

下面是写传输失败的例子。

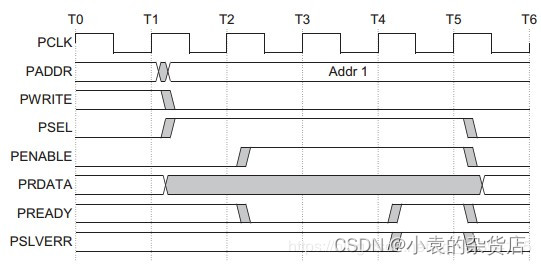

读传输同样可以使用错误响应,下图便是一个错误响应的例子:

对于读操作:READ如果是由~PENABLE形成,那么时序逻辑生成PRDATA,READ如果是由PENABLE形成,那么组合逻辑生成PRDATA。

总结:paddr(地址),pwrite(读写),psel(选择),pwdata或prdata(读写数据),同时有效表示数据加载成功,即将在下个周期拉高 penable,这个时候看 pready是否为高,如果为高,那么传输成功;如果为低,传输延迟。.

参考阅读:

https://blog.csdn.net/vivid117/article/details/107511746

1582

1582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?