基于ZYNQ FPGA实现8路ADC数据采集存储(AD7606)

1 ZYNQ FPGA简介

赛灵思公司在ZYNQ系列上成功将ARM的Cortex-A9处理器片上系统与A7系列的可编程逻辑集成在一起。相比于传统的CPU,ZYNQ系列处理器具有更强的并行处理能力,通过使用AMBA互联技术不仅可以轻松添加外设,还能够解决多种不同信号处理应用中的大量数据处理问题。在实际应用中,相比于传统的CPU+FPGA的双芯片架构,ZYNQ系列的产品更容易实现小型化、高性能和低功耗,并且能够为外设扩展提供足够的灵活。开发和调试工具为vivado套件。

2 系统设计

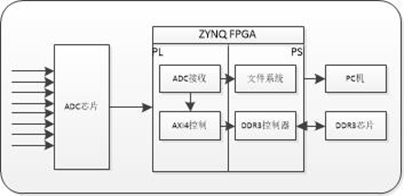

基于ZYNQ FPGA实现8路ADC数据采集系统框图如图1所示。ZYNQ FPGA型号为XC7Z020,外挂芯片有2片DDR3、1片QSPI FLASH、1片EMMC、ADC芯片AD7606(ADC支持8通道同步采样,最高采样率为200Ksps, ADC采样可以达到16位采集精度,充分满足项目采集的精度要求)。基于硬件板卡分别对PL部分和PS部分进行功能设计,PL部分负责接收AD采集板的转换结果数据和控制PL与PS之间的AXI总线,主要功能模块包括ADC接收模块、AXI4控制模块和FIFO数据交互模块。PS部分负责控制DDR3与EMMC的数据读写。

图1 系统设计

1)ADC模块:接收ADC芯片送来的8路数据,进行数据缓存、位宽转换、跨时钟域处理。

2)AXI控制模块:选择zynq处理器HP接口(高性能接口),通过AXI4总线将读写的数据和地址发送到PS内部的存储控制器,存储控制器根据地址和数据对DDR3进行读写操作

基于ZYNQ FPGA实现8路ADC数据采集存储(AD7606)

最新推荐文章于 2024-05-19 20:07:23 发布

订阅专栏 解锁全文

订阅专栏 解锁全文

465

465

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?