提示:只提供参考

提示:只提供参考

前言

一、比较器是什么?

在数字电路中,经常需要对两个位数相同的二进制数进行比较,以判断它们的相对大小或者是否相等,用来实现这一功能的逻辑电路就称为数值比较器,简称比较器。

二、logisim表示

原理:

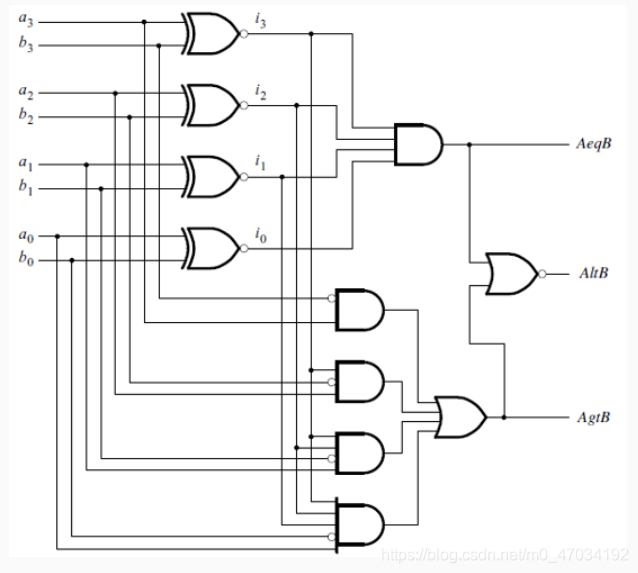

4位比较器原理

4位比较 a3a2a1a0 : b3b2b1b0,比较顺序从高位到低位,当高位大、小关系确定时则无需看低位,当高位相等时再看相邻低位的关系。

大于Great:

L1 = L31+L33∙L21+L33∙L23∙L11+L33∙L23∙L13∙L01

等于Equal:

L3 = L33∙L23∙L13∙L03

小于Less:

L2 = ~ (L1 + L3)

Lij第1个下标表示位数,第2个下标表示大小关系1大、2小、3相等,只有一个下标时表示大小关系。

注意:对于三个比较结果,已知其中任意两个,可以用或非门求得第三个。

原理图:

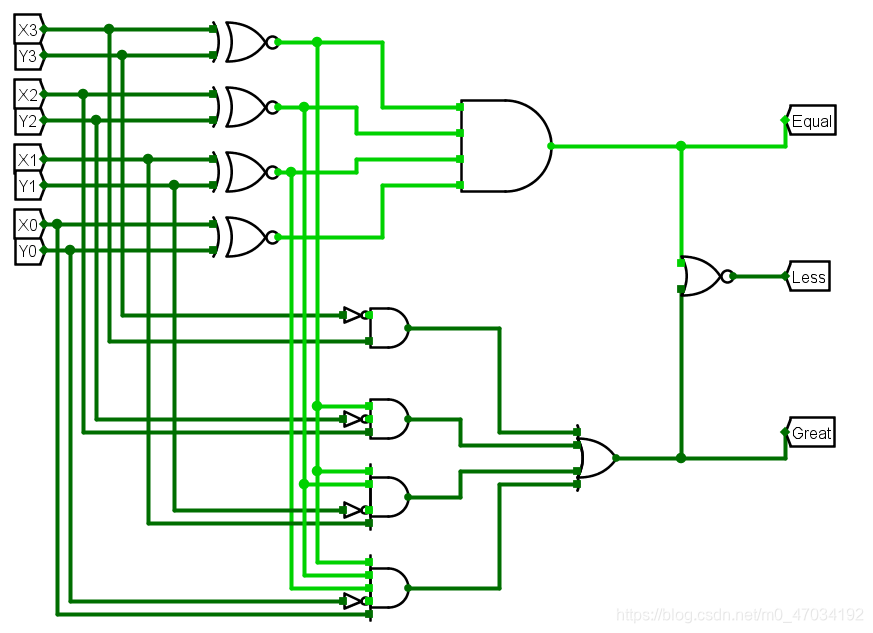

Logisim:

提示:仅提供参考,请勿抄袭

本文详细介绍了数字电路中的比较器概念,特别是4位比较器的工作原理,包括判断逻辑和Logisim软件中的实现步骤。通过逐位比较和逻辑运算,了解了大于、等于和小于的逻辑表达式,并展示了Logisim工具如何构建和展示这个过程。

本文详细介绍了数字电路中的比较器概念,特别是4位比较器的工作原理,包括判断逻辑和Logisim软件中的实现步骤。通过逐位比较和逻辑运算,了解了大于、等于和小于的逻辑表达式,并展示了Logisim工具如何构建和展示这个过程。

5175

5175

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?