本文从PCIe常见的系统应用和BaseSpec的角度,简要介绍PCIe拓扑结构和各个组件的功能及基本概念。

PCIe 系统拓扑结构

此图是BaseSpec中关于PCIe fabric及拓扑结构的示意图,一个常见的PCIe系统内,一般的会包含一个或多个RootPort及SoC其他组件共同组成的RootComplex。一个或多个PCIe Switch,以及多个PCIe Endpoint(或Legacy Endpoint)组件。

上图以AMD Ryzen CPU为例,Ryzen CPU SoC可以认为是Root Complex,其下挂了若干个Endpoint设备,如Storage,Graphics等。AMD X570可以认为是Switch的部分,因为往往chipset下面还会连接更多的PCIe Endpoint设备,比如更多的PCIe/NVME/SSD/USB等存储设备,以太网控制器,声卡等等。

PCIe系统组件

Root Complex

PCIe BaseSpec中描述的RootComplex不只是描述一个SoC中的IP,而是一系列功能。一般的PCIe接口协议相关的叫Root Port,是pcie系统结构中的一个port。BaseSpec定义的RootComplex是:

- RC 表示IO Hierarchy的Root,并且和CPU/Memory子系统相连。

- RC可以包含一个或多个PCIe port (Root Port). 每一个interface分别定义了PCIe域及其层级结构。 每一个PCIe域和层级结构可以包含一个或多个PCIe Switch和Endpoints。

- RC需要支持产生configuration request。

- RC可选的支持产生I/O request。

- 当RC作为Completer时,不允许支持Lock操作。相反的,RC可以支持发送Locked requester as Requester。

上面是一段从BaseSpec翻译过来的,阅读起来非常绕口。稍微总结几句:

1. RC是整个PCIe树形数据结构中唯一的主控者,一个PCIe tree结构下只允许有一个PCIe RC,可以有多个Switch和Endpoint。

2. RC是整个属性结构的发起者和建立者,换言之,因为PCIe是使用Configuration request来枚举和建立PCIe层级结构的,所以只有RC允许发起configuration request。所有其他的PCIe 设备均不允许发送configuration request。

3. RC也是传统PCIe设备中唯一的Host (可以理解为CPU),而传统设备中,只有Host CPU可以发送IO指令,所以BaseSpec描述,RC支持IO Request。因为现代CPU大多使用IOMMU,而非传统IO操作,所以IO request基本已经很少使用了,所以这个IO request对RC来说是Optional。

4. 不支持作为Lock completer, 这个用的比较少,应该是因为RC作为唯一的主控设备,如果他的内存或者某compoment被PCIe hierarchy下面的某个Endpoint给Lock住了,要防止互锁的发生,所以RC是不允许被Lock的。

PCIe Switch

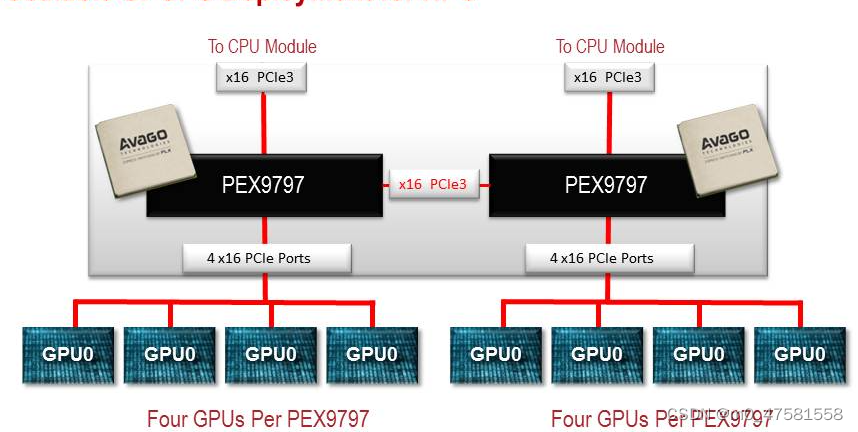

上图PEX9797就是AVAGO推出的PCIe Gen3多端口PCIe switch及典型应用场景。

- 向上连接一个PCIe 的Root Complex (CPU)

- 下面挂在若干个高速设备(此处是4个GPU)

- 另外此PCIe switch支持一个端口对接到另一个PEX9797 switch,用于扩展PCIe endpoint设备数量,或者作为transparent bridge (Optional)对接另一个PCIe tree。

下图是一个PCIe Switch的内部结构概念图。一个Switch由一个Upstream Port,负责和上一级Switch或者Root Port对接。和若干个downstream port,以及一个内部的“交换器/桥接器/路由器”,名称可能很多,工程差不多,主要实现TLP或者Message的路由。

PCIe Endpoint

再PC和Server领域,我们大量的能看到PCIe Endpoint(终端)设备,比如个人PC上用的显卡(金手指那个接口就是PCIe),NVMe硬盘,网卡(特别是万兆网卡),插在PCIe插槽上的声卡等。服务器上的GPGPU,AI算力卡等等,基本上全部使用PCIe接口。Endpoint常见支持的Feature有:

- 支持Memory read/write requestor和completor。

- 支持发送MSI/MSI-X/INT-x等中断消息。

- 支持最大实现6个BAR(Base Address Registers)

- Endpoint只能作为Configuration和IO requester的重点。不能转发和自己发送configuration/IO request.

- Endpoint可以支持多个function,physical function 和virtual function。

全文完

4042

4042

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?