基于Cortex的MCU设计

今日更新的存货文档,发现日更文章还是很花时间的。保证一周更新三篇文章就行啦,本篇文章的内容起始主要取自于《Cortex-M3 权威指南》和知网下载的论文。写的不详细,想进一步了解的就去看这篇文档或网上找别的资料,有错误的地方评论区留言或者私信我,我再更改。书本网盘链接如下,永久有效链接。

链接:https://pan.baidu.com/s/1Zp0L1rAnCJi8brKHjc766Q

提取码:5v92

文章目录

一、概述

如下表所示,MCU大致可以分为5个发展阶段,MCU的位数表示微处理器核每次处理数据的位数或者总线系统的位宽。目前电子市场的主流芯片是16位和32位处理器。

MCU按照指令集可以分为复杂指令集计算机(Complex Instruction Set Computer,CISC)和精简指令集计算机(Reduced Instruction Set Computer,RISC)。现在市面上常用的MCU采用的ARM架构是RISC指令集,该指令集的计算机处理速度更快、功耗更低。

根据MCU中才采用的存储结构不同可以分为冯诺依曼结构和哈佛结构,前者程序指令和数据指令共用同一个存储空间,后者程序指令和数据指令放在不同的空间。目前常用的MCU基本都是采用哈佛结构,比如ARM公司推出的ARM架构大多也是采用的哈佛结构,部分对内核要求很高的SOC系列芯片,采用的是冯诺依曼结构。本文主要讲解以下基于Cortex-M3内核的MCU设计时需要具备什么硬件功能。主要是从处理器内核、系统片上总线和片上外设三部分去讲解。

二、什么是Cortex-M3内核?

基于ARM的MCU控制器的制作流程如下图所示,各大芯片厂商得到了ARM微处理器授权后,根据自身需求再处理器的基础上添加存储器、系统总线和外设等部件。

ARM公司设计了多系列的微处理器内核,其部分Cortex-M系列的产品如下所示,Cortex-M3系列的处理器是ARM公司为高性能、低成本的平台开发而设计。

Cortex-M3具备一个完整的微控制器架构,如下图所示,下文将会根据该内核的简化视图依次从指令集、寄存器、异常和中断、存储器映射和总线接口五大点讲解内核的核心知识点。

2.1 指令集

ARM处理器目前可支持两种相互独立的指令集,分别是32位的ARM指令集和16位的Thumb指令集,两而cortex-M3可支持这两个指令集,三者之间的关系如下所示。

2.2 寄存器

Cortex-M3包括16个32bit的寄存器和多个特殊寄存器。特殊寄存器包括程序号状态寄存器、中断屏蔽寄存器和控制寄存器,其分类如下所示。

2.3 异常和中断

Cortex-M3支持11种类型的系统异常以及240个外部中断,通过内核中搭载的嵌套向量中断控制器(Nested Vectored Interrupt Controller,NVIC)实现对中断和异常的响应,其系统中断如下所示。

2.4 存储器映射

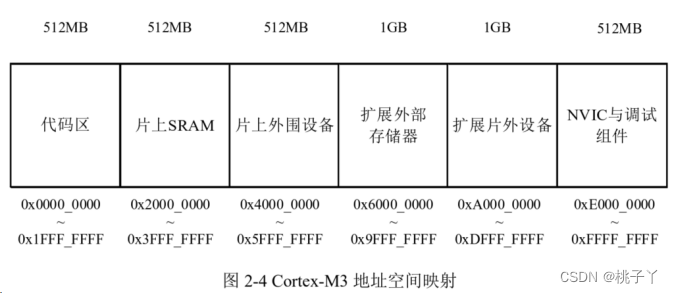

Cortex-M3的地址空间映射如下所示。

2.5 总线接口

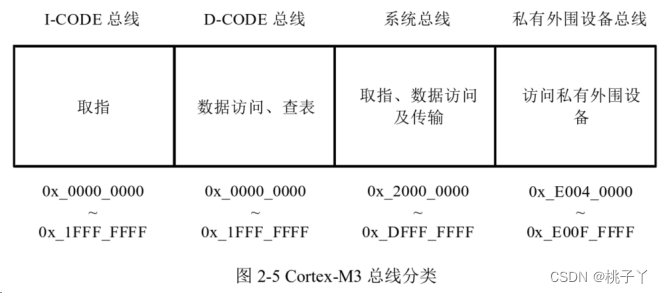

Cortex-M3处理器内核基于AHB总线协议的32位总线接口包括:I-CODE总线、D-CODE总线、系统总线和外设总线,如下所示。

三、芯片内部数据怎么传输?(AMBA总线)

3.1 AHB总线特性和构成

计算机不同部件之间通过什么通信呢?以及各种电子设备之间通过什么传输数据呢?我们知道UART、I2C和SPI等通信协议都是需要对应的线缆进行通信的,并且有对应的通信协议。

那么SOC内部之间各个模块之间的数据是怎么传输的呢?同样的道理啦,也是需要在芯片内部构建对应的“线缆”和“通信规则”。即,在SOC里,单个芯片内部集成了内部总线和微处理器,那么这就称为片上系统总线。一个新概念的提出,必定会有其定义和名字及相关规则吧。而ARM公司推出了面向高性能微处理器的片上通信协议,即先进微控制器总线结构(Advanced Microcontroller Bus Architecture)协议。我们现在常用的微处理器采用的就是AHB总线,该总线就是AMBA总线协议中的一种,其支持多总线主机和流水线操作,典型的AHB总线系统如下所示。

AHB的总线信号一般分为主机接口信号、从机接口信号和其他信号三大类,部分关键信号名称和作用如下表所示。

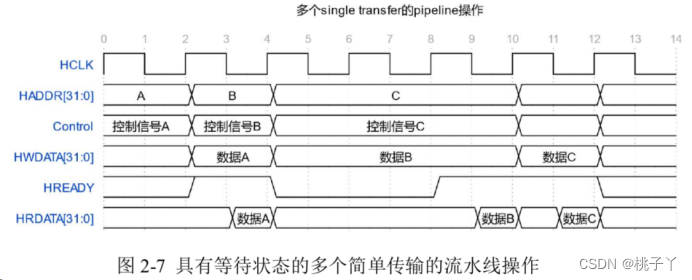

AHB采用流水线传输操作,其数据传输过程如下所示。

3.2 APB总线

与AHB总线不同的是,APB总线没有流水线操作,其主要的信号描述如下所示。

APB总线的传输状态如下图所示,我们可以看到,APB传输数据主要分为3个状态。①外设总线的默认状态;②SETUP状态,有传输数据时候,PSEL_x信号拉高,总线保持一个SETUP周期。③ENABEL状态,该状态下PENABLE拉高保持一个周期,传输数据。如果没有数据传输了则进入到状态①,负责进入状态②。

根据以上的状态机,APB写传输的时序如下所示。

APB读传输时序如下。

3.APB桥

AMBA总线协议提供了APB桥实现AHB总线和APB总线之间的时序切换。APB桥在总线系统中既是AHB的从机又是APB的唯一主机。APB桥接信号如下图所示。

三、MCU外围设备

不同的生产厂商根据自身的需求会增加对应的外设,包括有定时器、输入输出端口、通信接口、看门狗、SPI接口、I2C接口等。

我们现在使用的32位单片机,基本都是基于ARM的内核实现的MCU。比如我们常用的STM32F103,其内核是ARM的cortex-M3内核,在内核的基础上再配置了一些外设,如GPIO、ADC、DAC、USART、SPI、I2C等外设接口。且这些芯片公司基本都有成熟的固件库,芯片公司已经写好了对应外设的API接口函数,我们在应用的时候使用固件库开发就会轻松很多,不需要再去花时间去配置对应的寄存器。但是对于一个实际的系统开发,我们需要编写MCU控制器以外芯片对应的配置代码,需要访问对应芯片内部寄存器控制芯片功能。

3294

3294

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?