实验目的 1、掌握FPGA中lpm_ROM只读存储器配置方法。 2、用文本编辑器编辑mif文件配置ROM,加载于ROM中; 3、验证FPGA中mega_lpm_ROM的功能

步骤:

1.新建工程

设置硬件。不设置不影响仿真。

新建好了一个空的工程。

2.画原理图

注意:电路图文件名和顶层名字要一样。

开始画图,双击空白地方。

点击ok,弹出如下窗口。实例化器件。注意:器件不要和顶层实体重名。

next之后继续定制器件。

选择是否初始化。先写一个文件(不需要存在,后面再关联)即指定一个地址。

next,finish,yes。

定义输入输出引脚:

插入input和output。

在地址输入引脚:点住input,右键。在properties中修改

a[5..0]语法表示六根线。

时钟输入和输出也同样方式命名。

连线。

node tool是单线的。

bus tool是排线的。

3.初始化

建立一个内存初始化文件。这个是本实验特有的部分。

选规模,和硬件定义的一样规格。

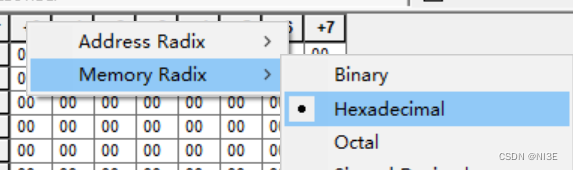

地址通常16进制表示。

随机写入地址。

save保存,名字和之前的留的mif文件名字相同。

4.功能仿真

新建波形文件。

设置:

在这里是功能仿真。并且指定功能仿真文件(.vwf文件)。

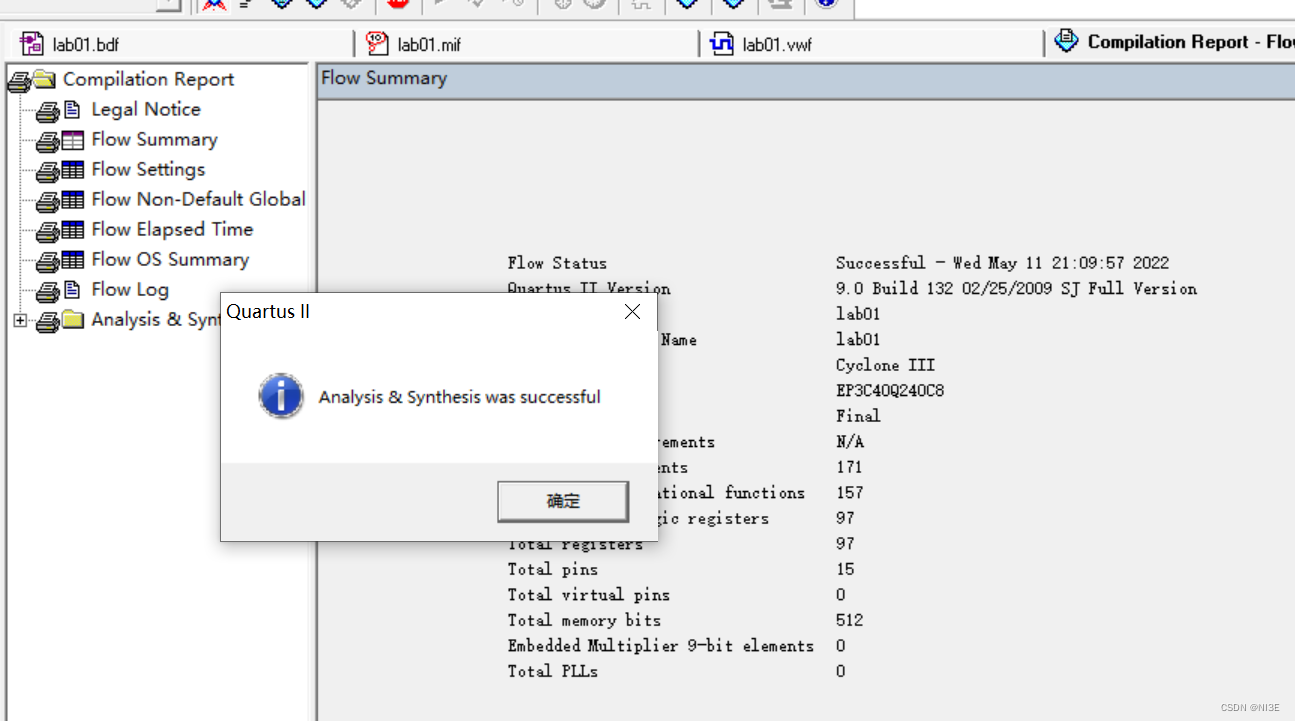

分析和综合(编译):

不显示成功说明前面有问题。

回到仿真文件。双击图示区域。

点击node finder。找到之前全部的引脚。点击list。需要做编译和产生功能网表。

选中a,q,clk。

ok。

为输入加入激励。

分别配置属性。右击点击properties。

加载激励:

(1)时钟

自己随意定义:

地址:要从第一个到最后一个。

(2)a

也可以随意设置。

一个常见错误:不要把上升沿放在地址中间,而是在有效区域内。

开始仿真。

读出来的应该和内存初始化的一样。

3446

3446

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?