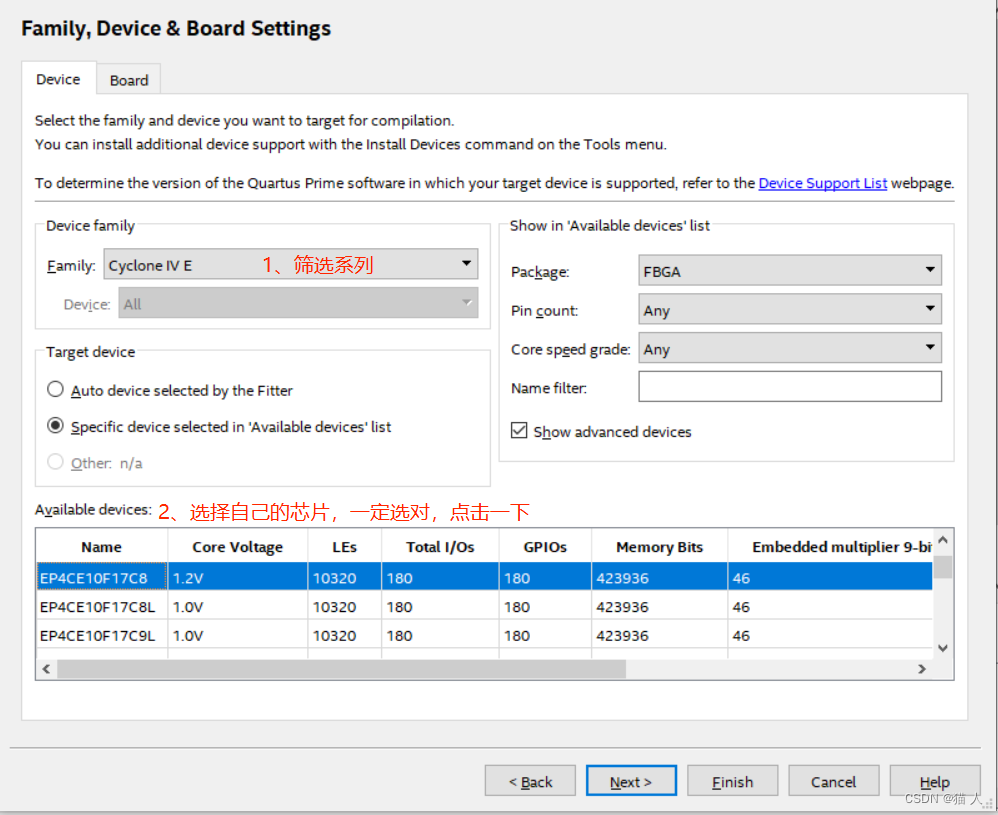

对于nios的详细知识这里不做解释,网上有很多大牛写的见解。本文只举例建立一个nios工程,并在fpga上run和和固化。本次使用EP4CE10F17C8,其他芯片同理。

在fpga跑一个nios软核需要硬件部分和软件部分。硬件即quartus工程建立代码综合,布局布线再将sof文件烧录进fpga实现nios硬件基础。

软件则通过eclipse进行代码工程添加和编写。

一、Quartus工程建立

1、建立工程文件夹nios_text,方便管理,名字任取,但请看图片下面注释。

注意:工程路径不要有中文和空格,之前使用vivado时出现过很恶心的问题,以防万一这里也不要有!

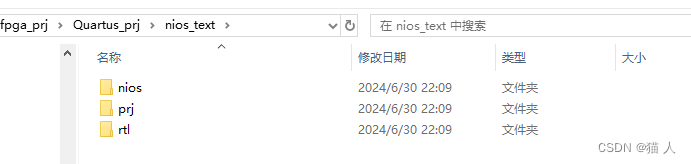

2、在nios_text文件夹中建立这三个文件,分别存放工程、nios相关文件、verilog代码

3、打开Quartus 点击new project wizard

下一步

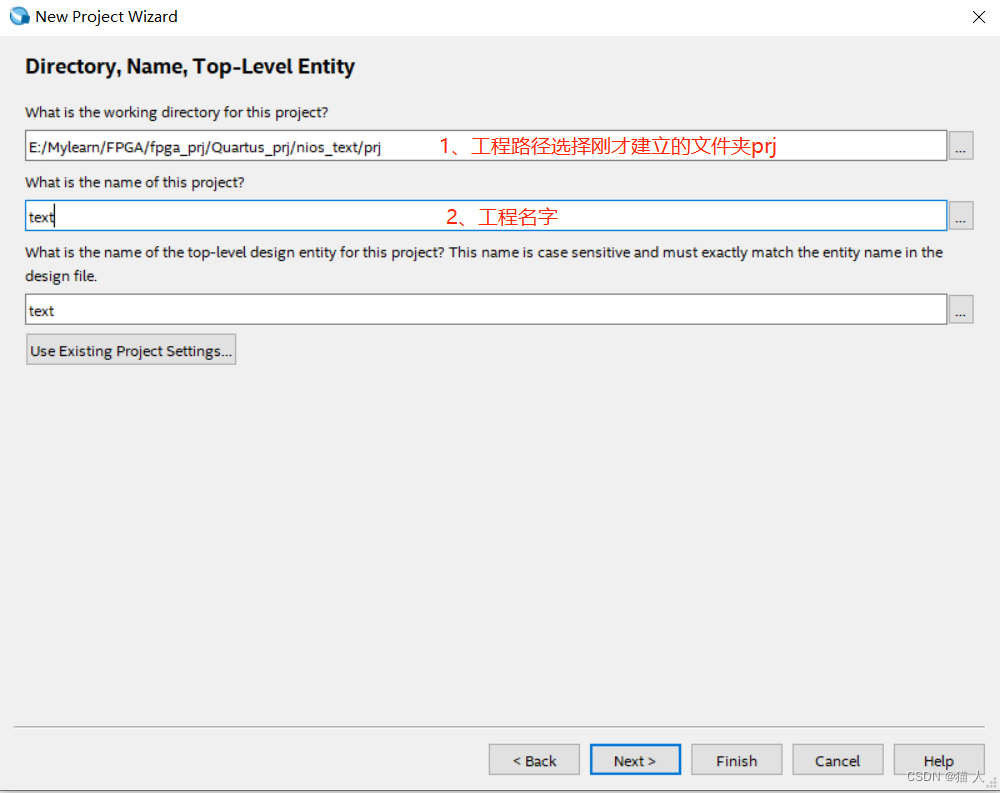

下一步

下一步

下一步

下一步,下一步,finish工程建立完成。

二、硬件部分

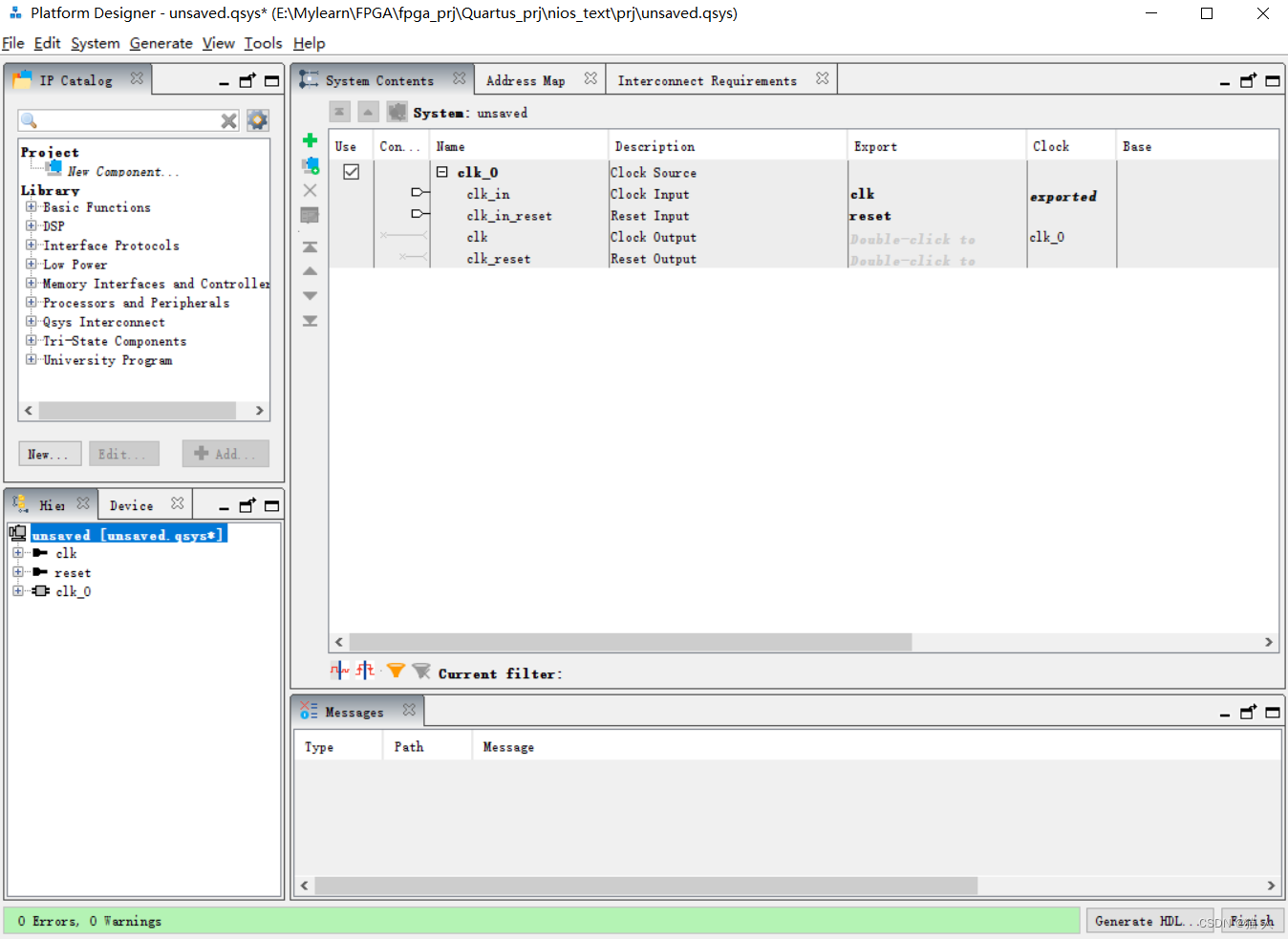

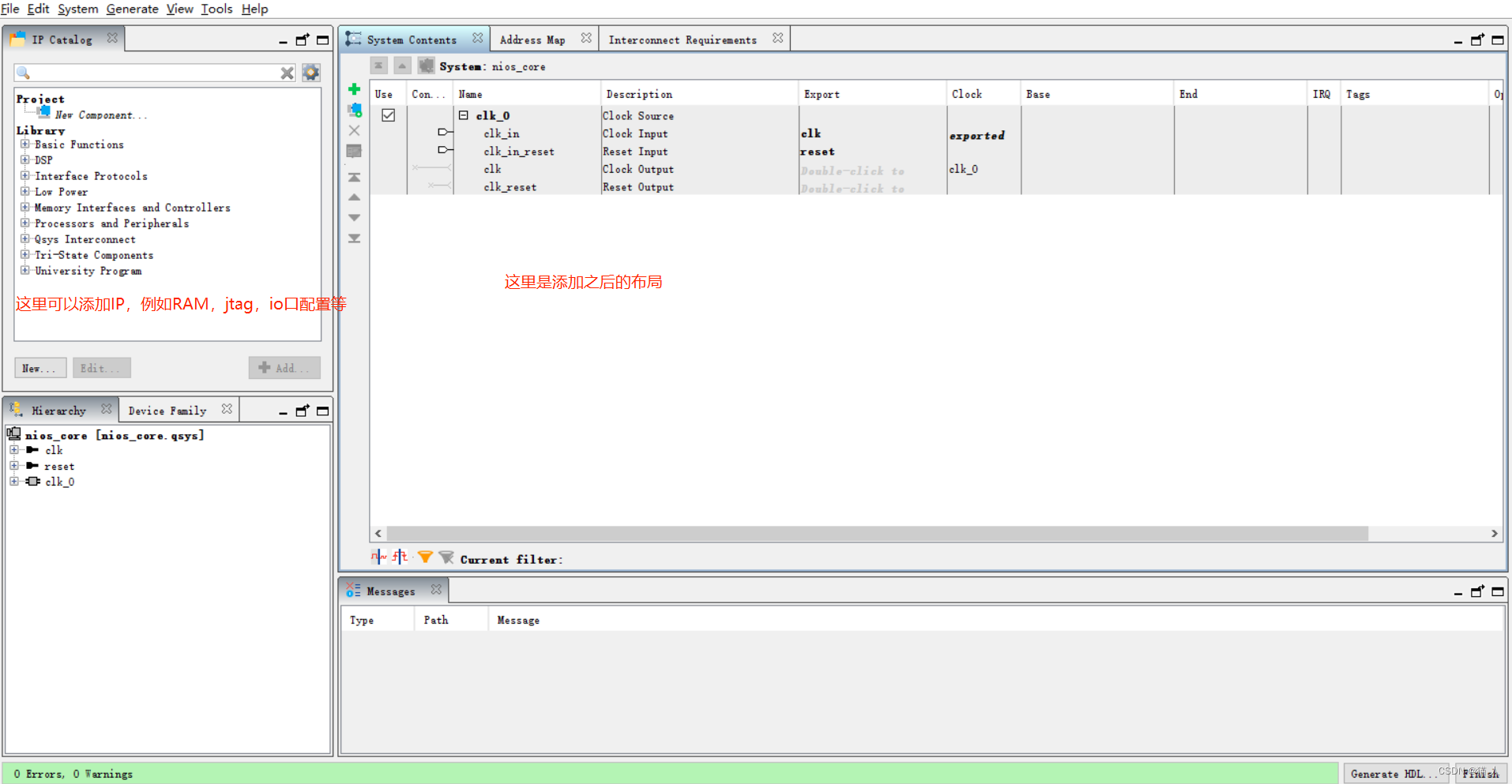

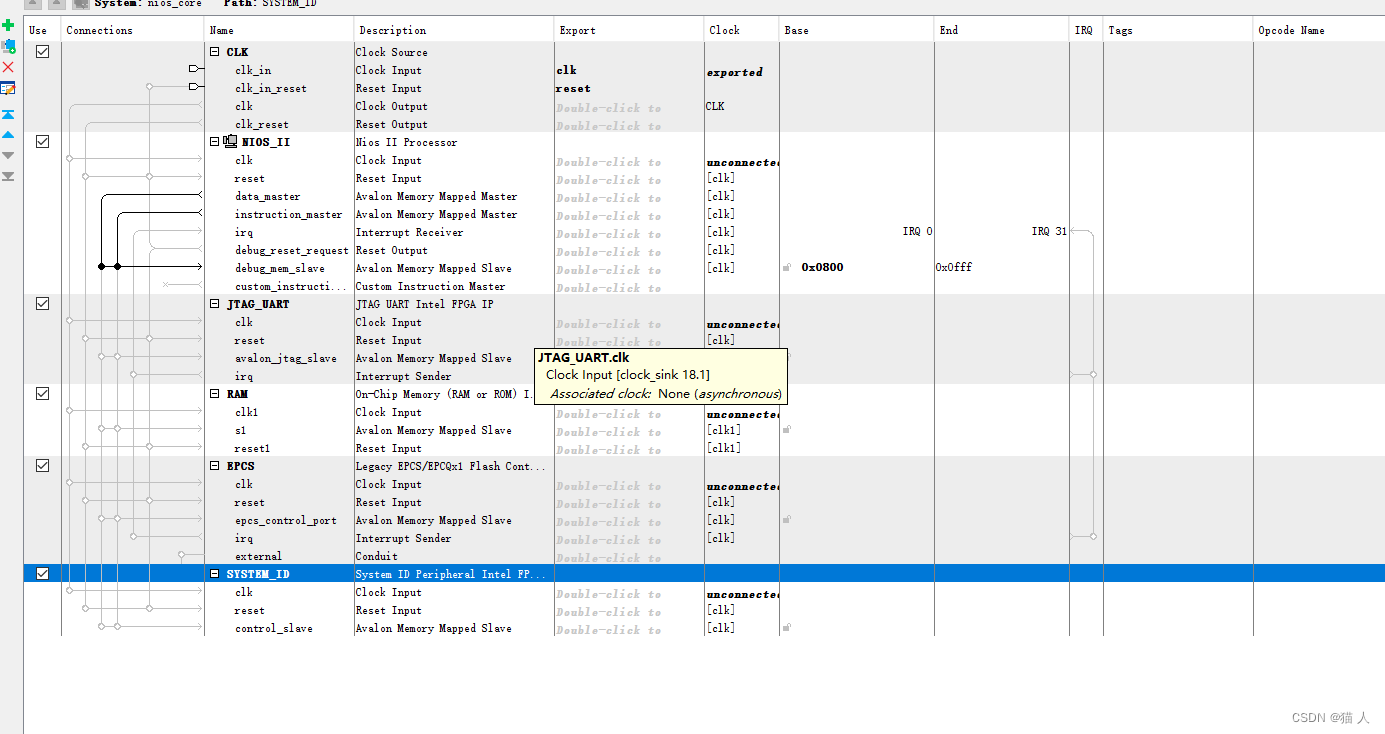

1、选择上方选项卡Tools—Platform Designer,打开Nios ii设计界面

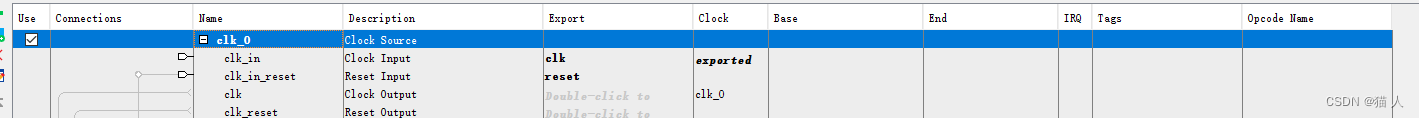

2、ctrl+s 保存设计文件,命名nios_core,路径选择文件夹nios

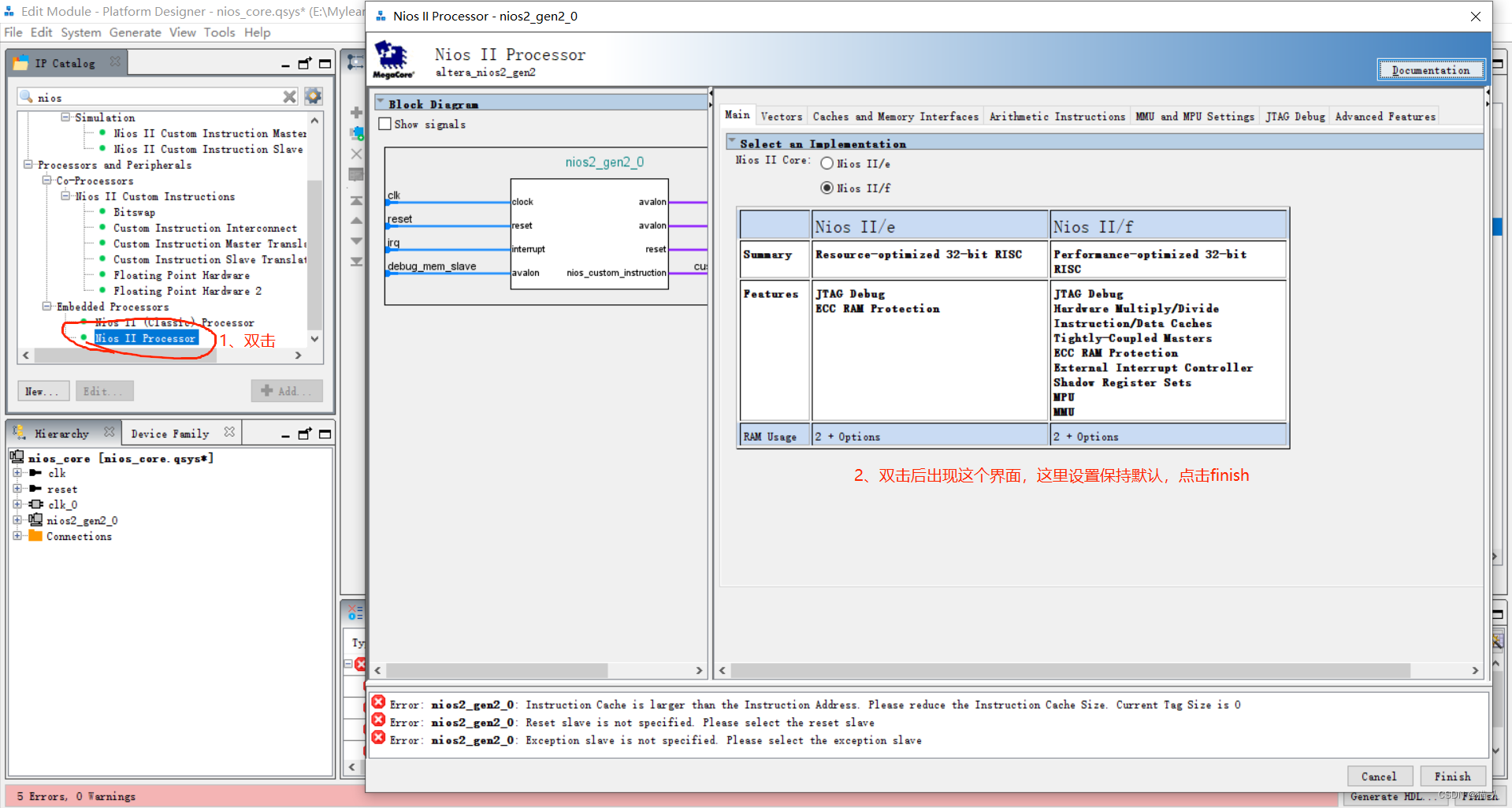

3、在左上的选项卡IP Catalog搜索nios II,双击nios II Processor,

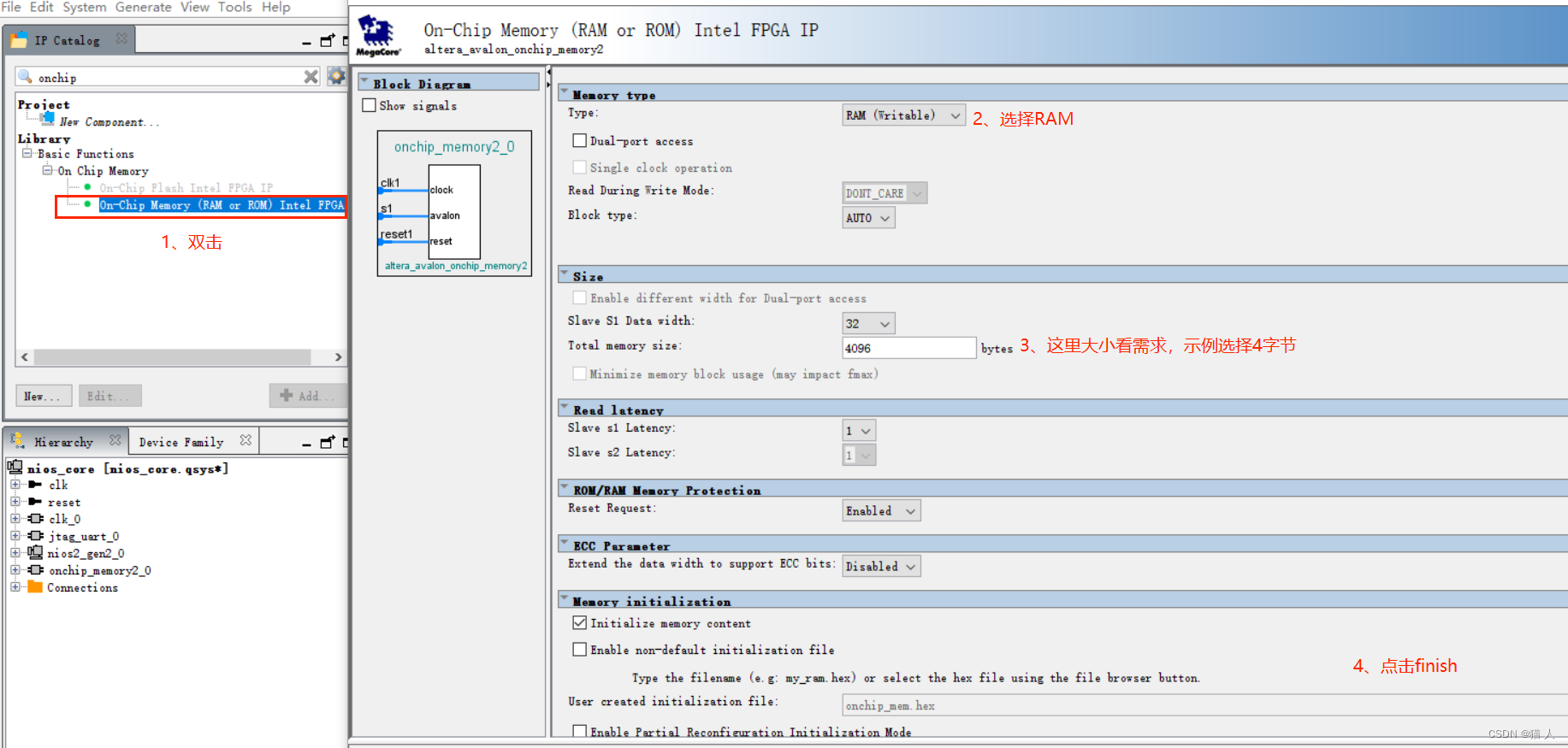

4、搜索onchip,双击on-chip memory(RAM OR ROM)Intel FPGA

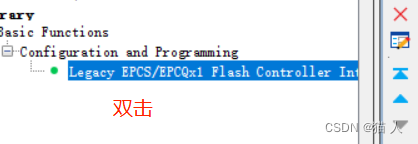

5、搜索epcs,nios固化用,双击,然后保持默认,点击finish

4、搜索JTAG ,双击JTAG UART intel FPGA IP(一定要点准,不然会弹出上一次的ip选项卡) 然后保持默认,点击finish。

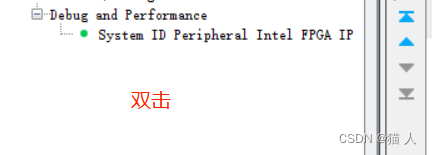

7、搜索sysid ,双击,然后点击finish。IP添加完成。

,

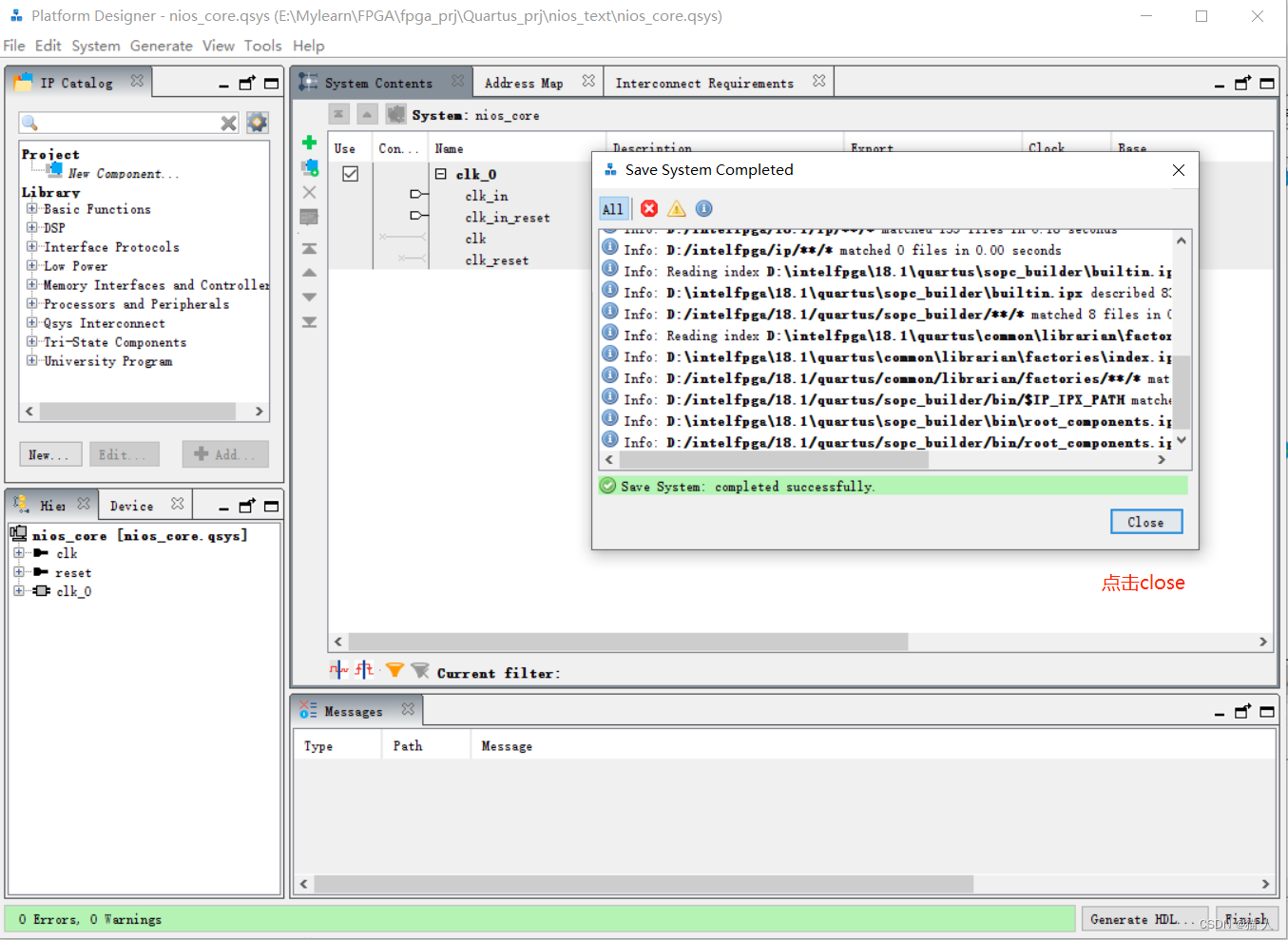

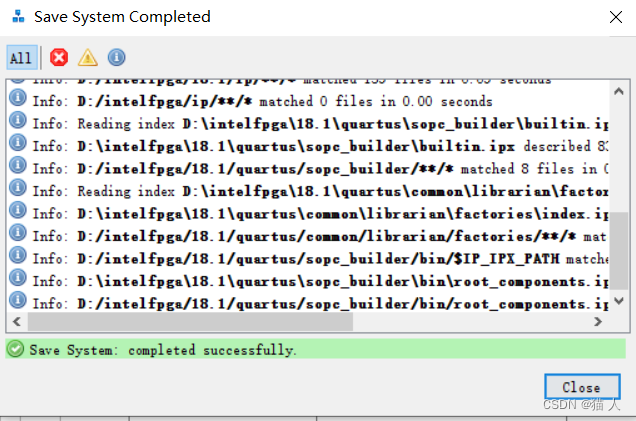

8、ctrl+s保存,然后点击close

9、对每个IP右键选择rename改名字,选中这里,变成蓝色后右键

改成如下图,然后Ctrl+s保存

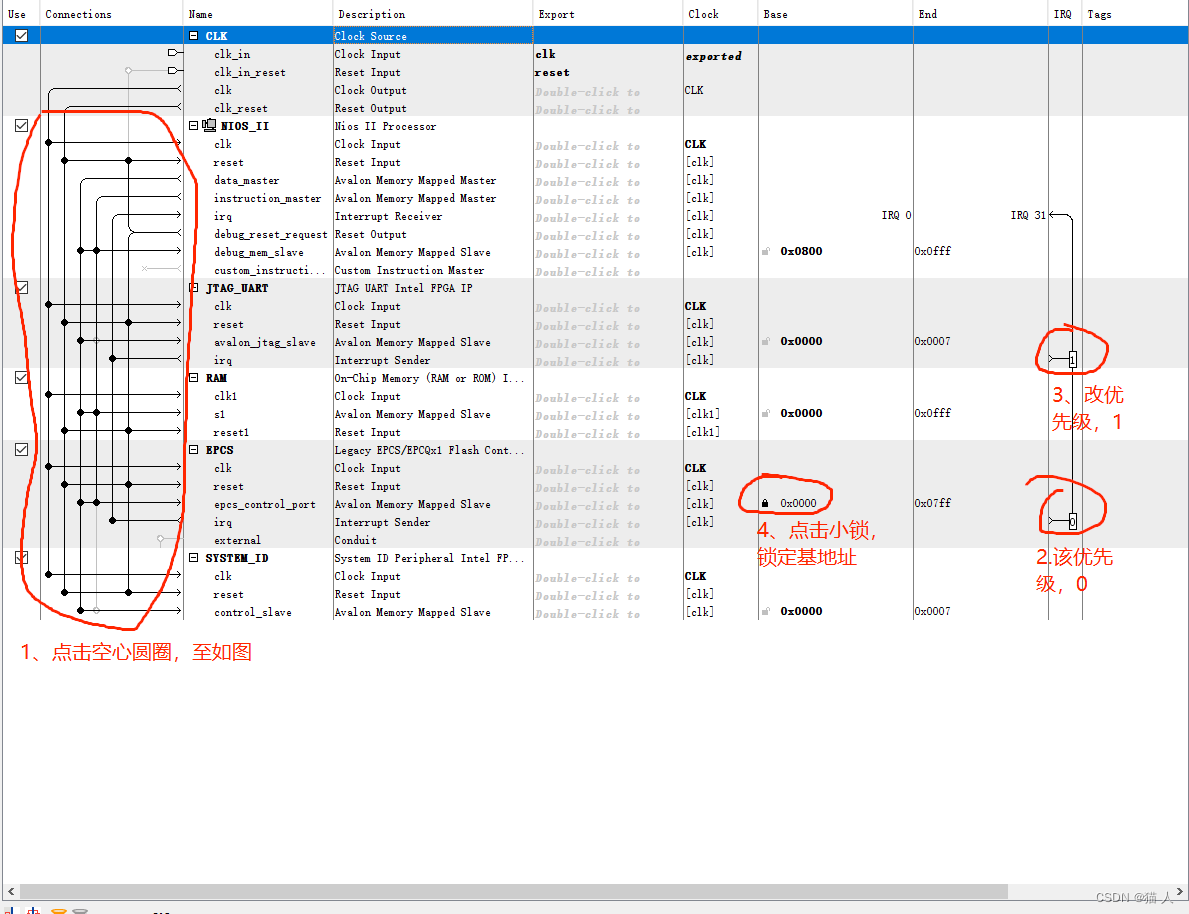

10、连线,点击空心小圆点,该优先级和锁定EPCS的基地址。然后ctrl+s

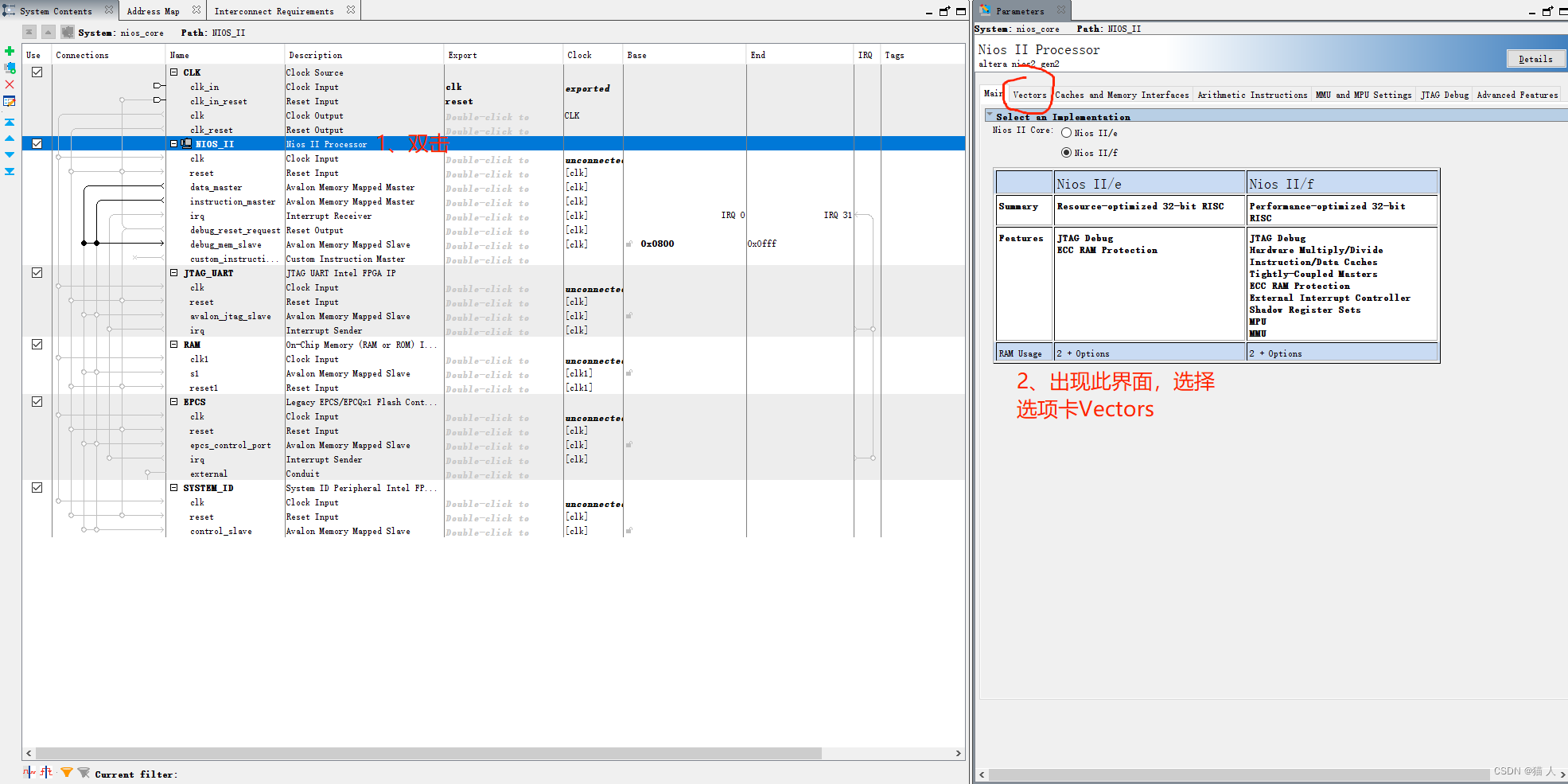

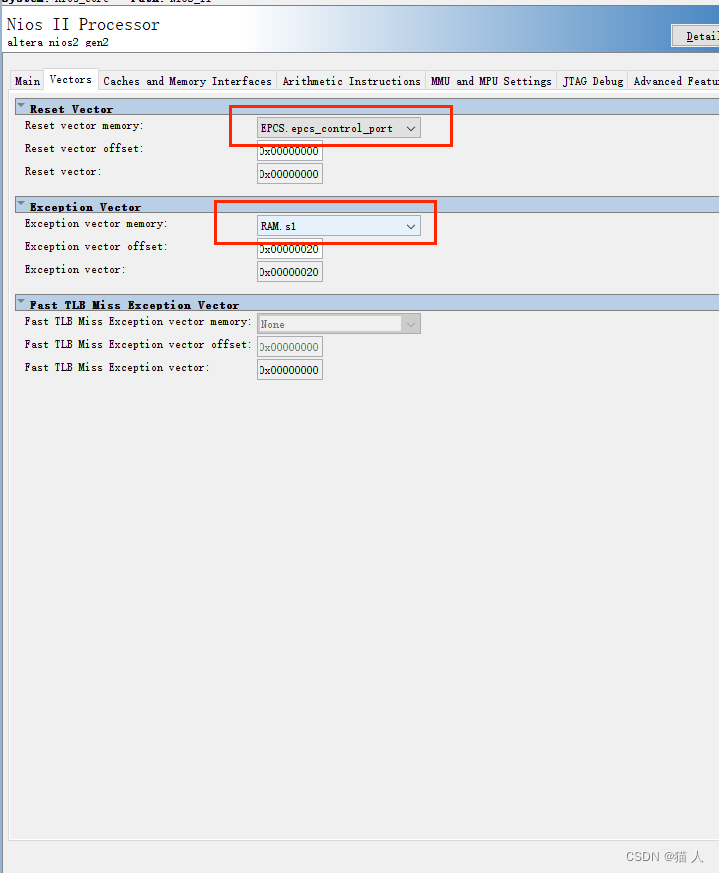

11、双击NIOS_II

配置如图,然后ctrl+s

12、此使底部message还有报错,点击上方System选项卡,选择Assign Base Addresses,然后ctrl+s

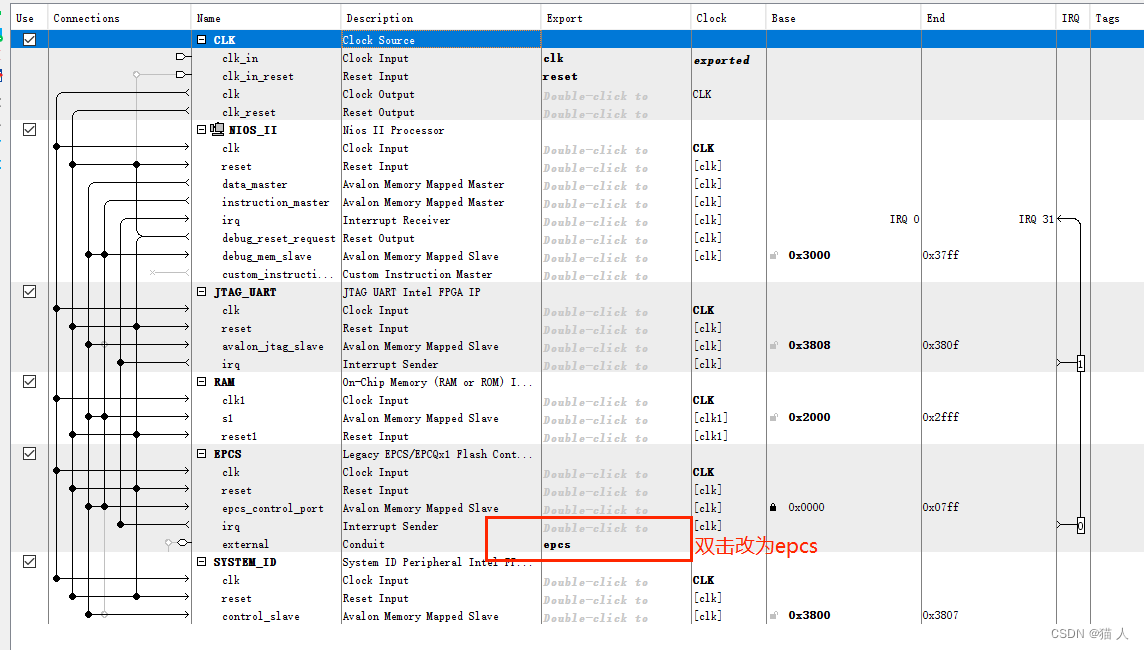

13、此时下方message选项卡有一个warning,需要给EPCS的IP一个输出,然后ctrl+s

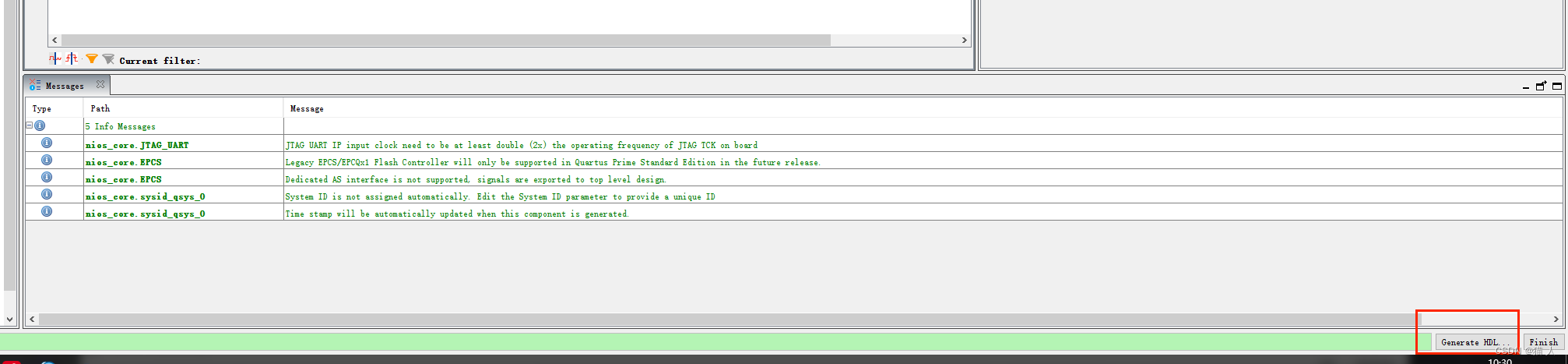

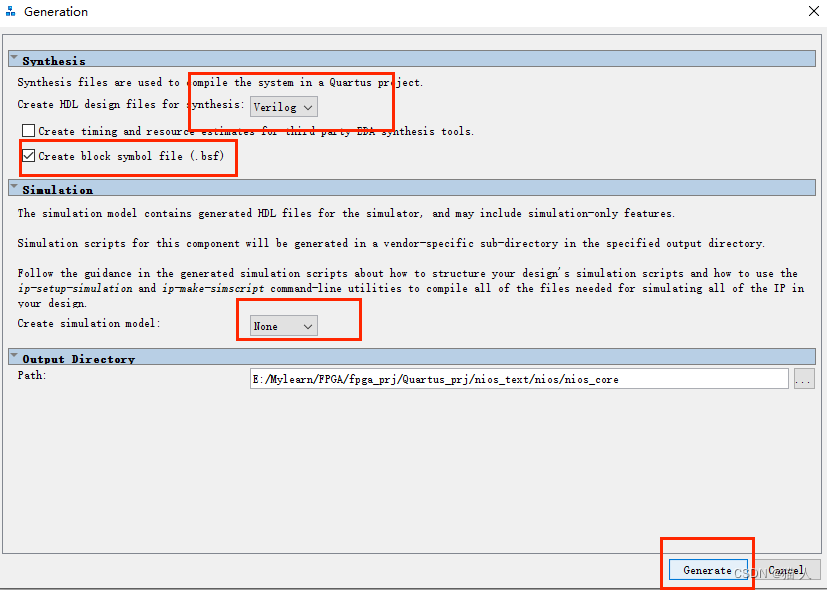

14、点击Generate HDL

一般默认,然后点击Generate,等待完成后可以退出Platform Designer

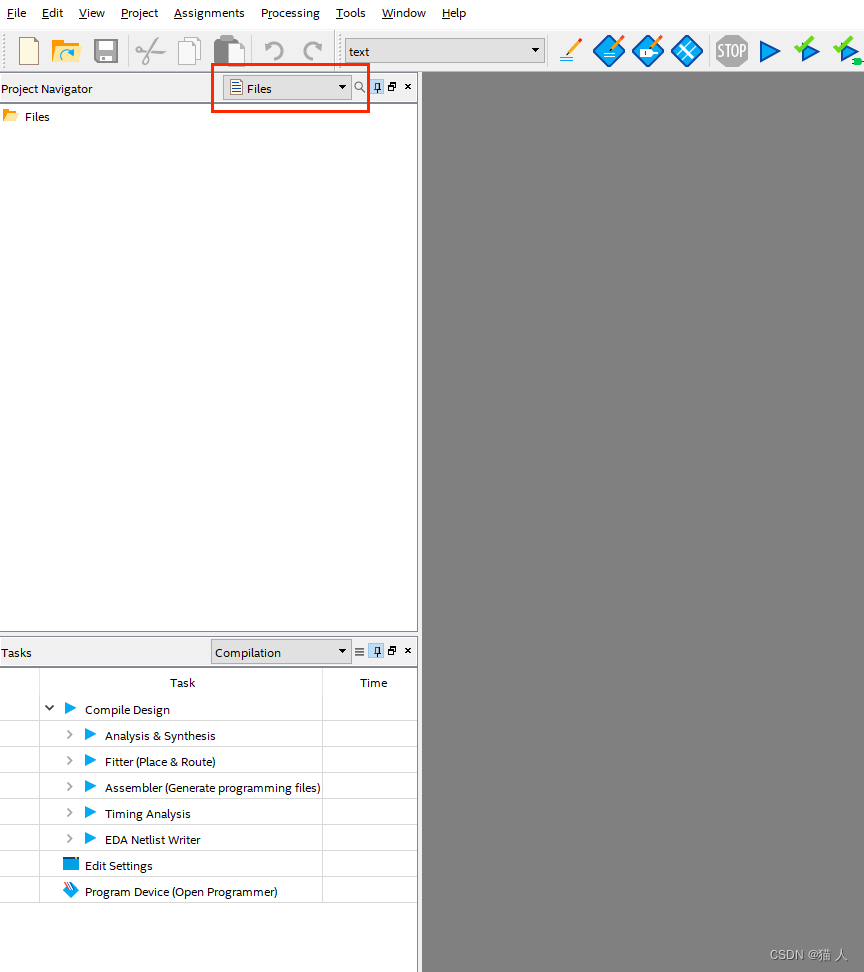

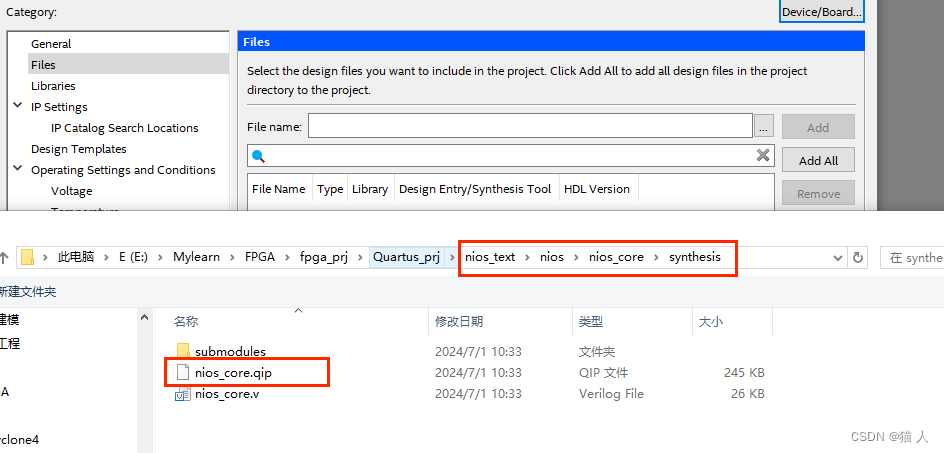

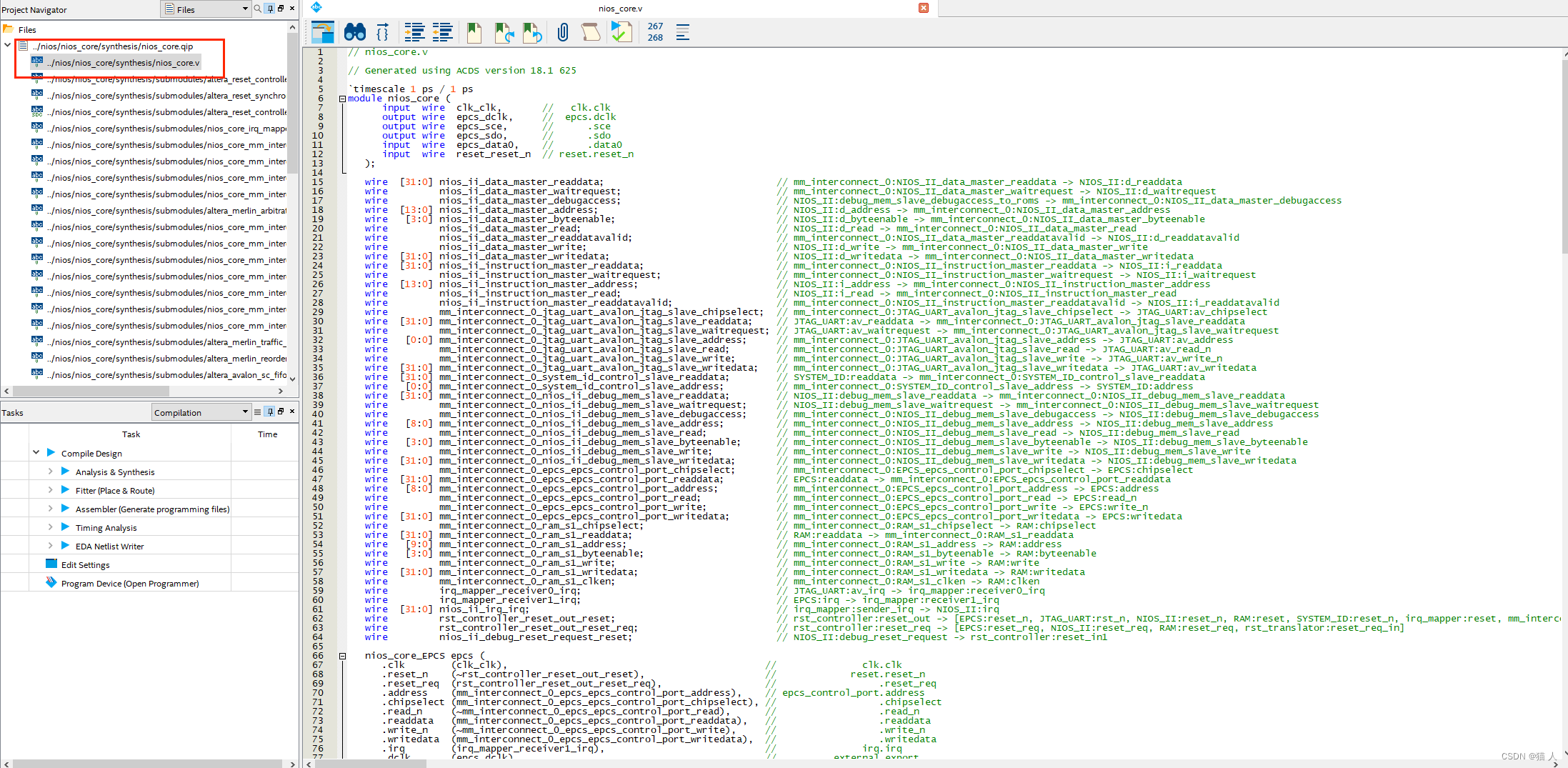

15、添加qip文件

路径如图,双击qip文件后,先选择Apply,然后点击OK

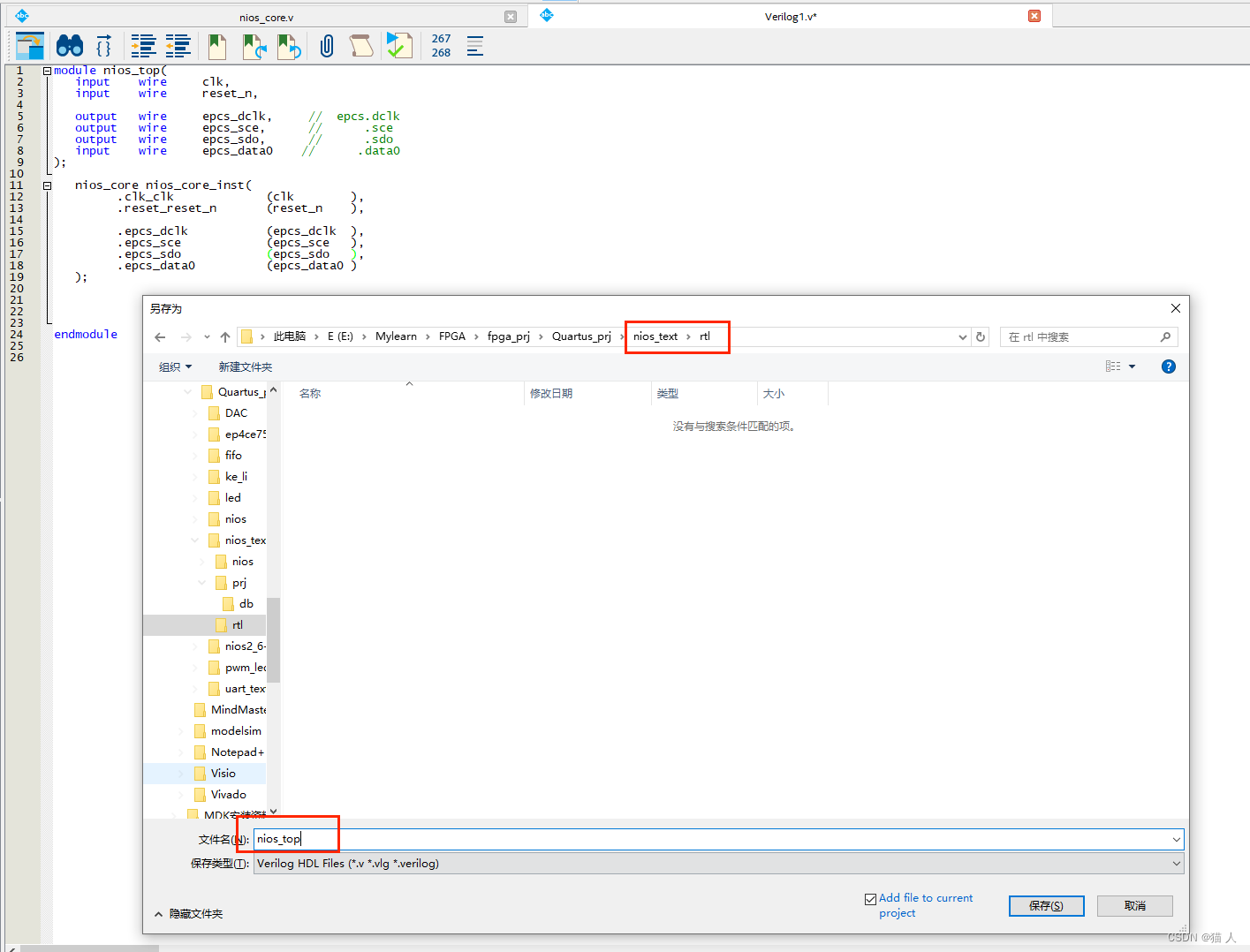

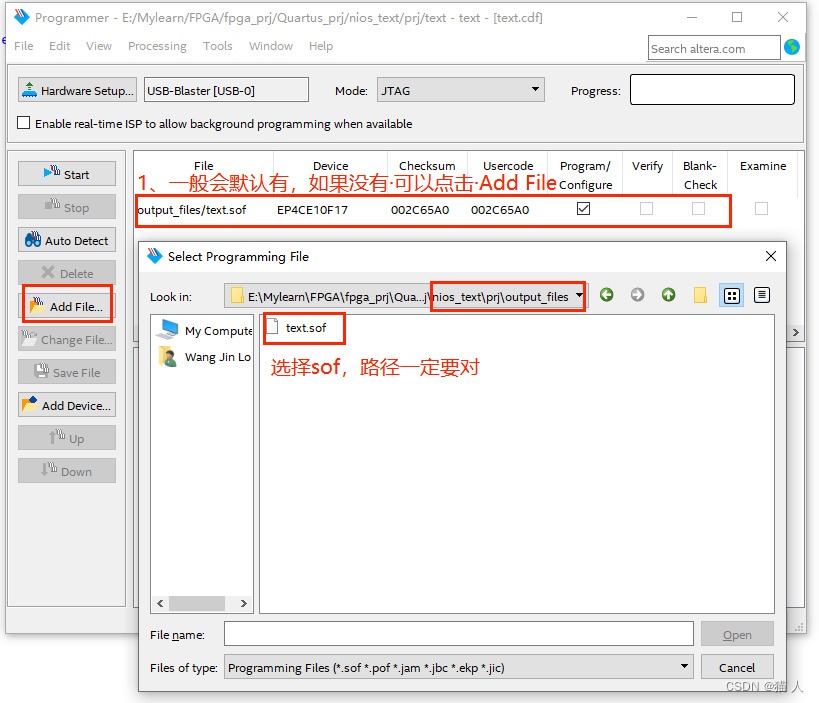

16、新建verilog文件,作为顶层文件,Ctrl+N,选择verilog HDL文件,代码如图,下面给出可复制代码,ctrl+s保存路径如下,改名nios_top.v

module nios_top(

input wire clk,

input wire reset_n,

output wire epcs_dclk, // epcs.dclk

output wire epcs_sce, // .sce

output wire epcs_sdo, // .sdo

input wire epcs_data0 // .data0

);

nios_core nios_core_inst(

.clk_clk (clk ),

.reset_reset_n (reset_n ),

.epcs_dclk (epcs_dclk ),

.epcs_sce (epcs_sce ),

.epcs_sdo (epcs_sdo ),

.epcs_data0 (epcs_data0 )

);

endmodule

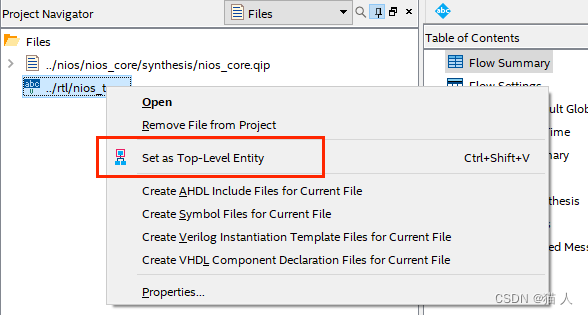

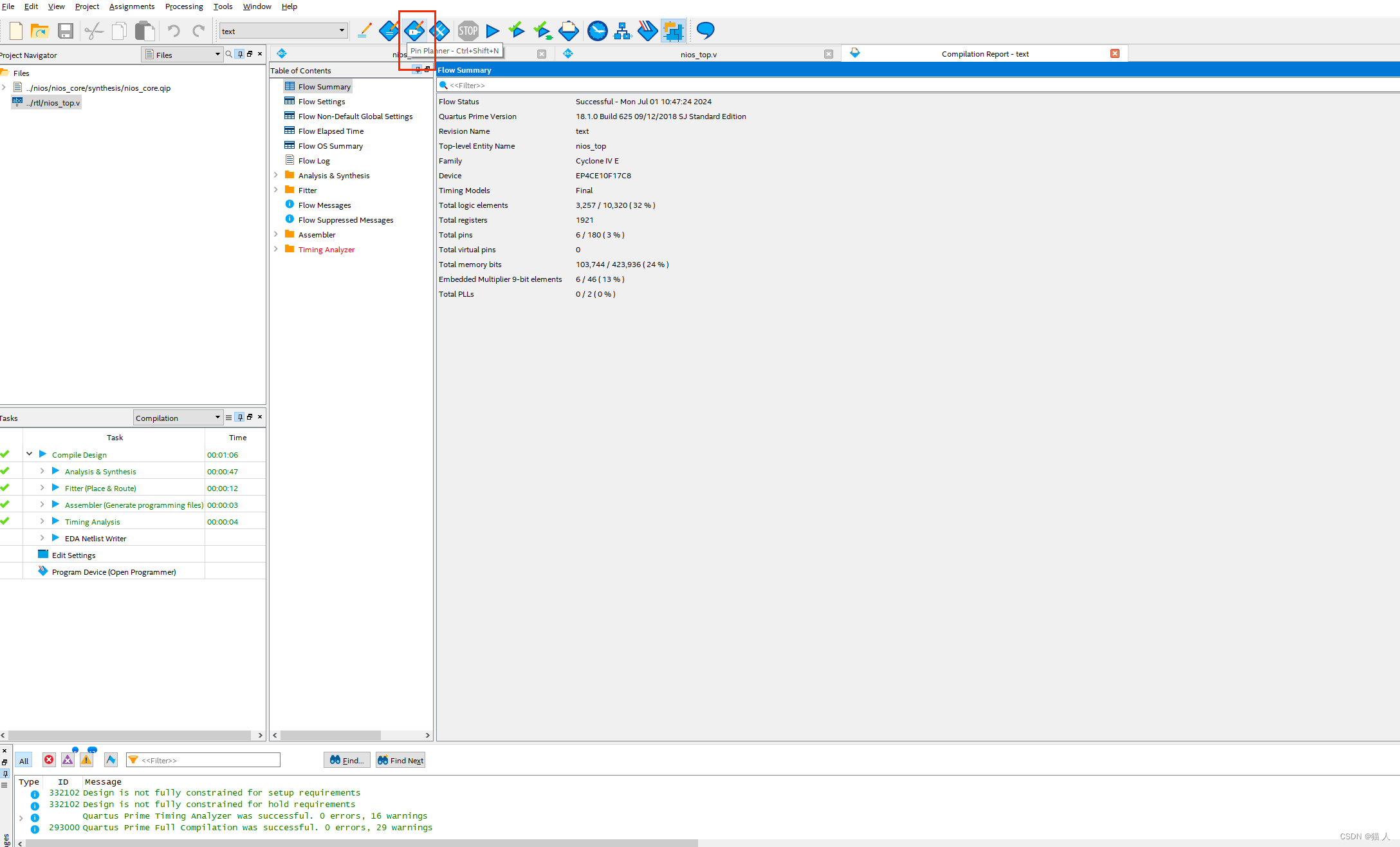

右键设置顶层文件,然后ctrl+L编译通过

17、分配引脚

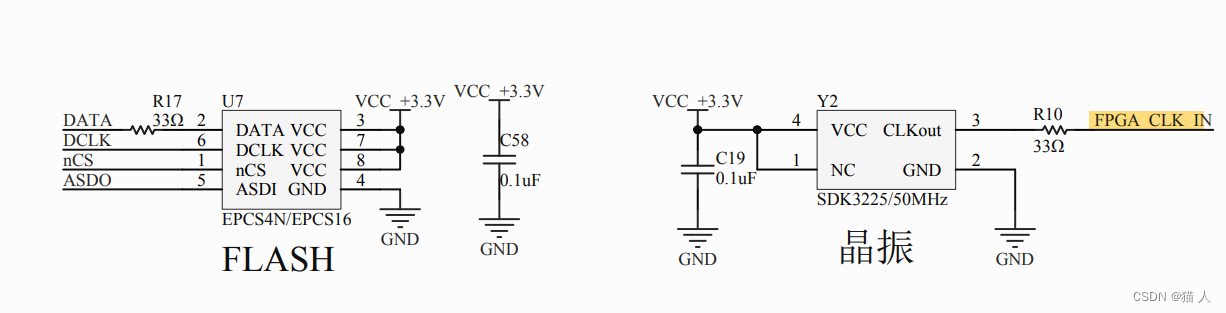

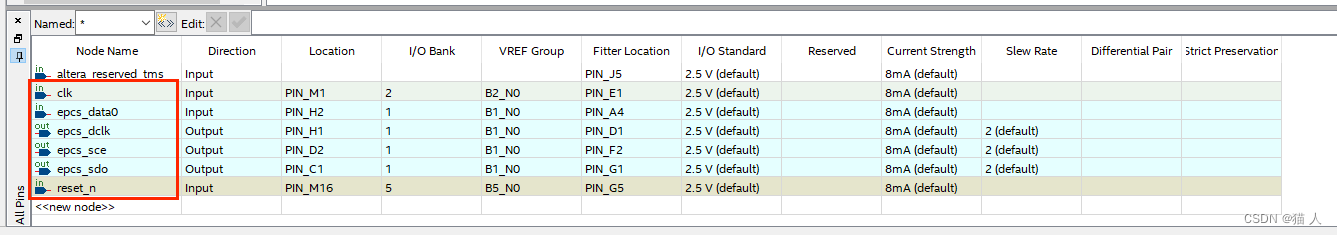

这里使用EP4CE10F17C8,核心板硬件上时钟在M1,随便选择一个按键作为复位M16,flash引脚如图,引脚分配根据自己的硬件实际分配

分配完成关闭Pin Planner 然后Ctrl+L编译,不小心翻车了,此时会报错,是因为flash引脚双用的问题

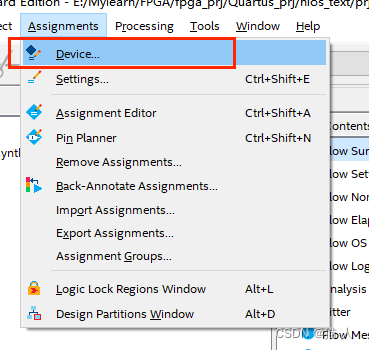

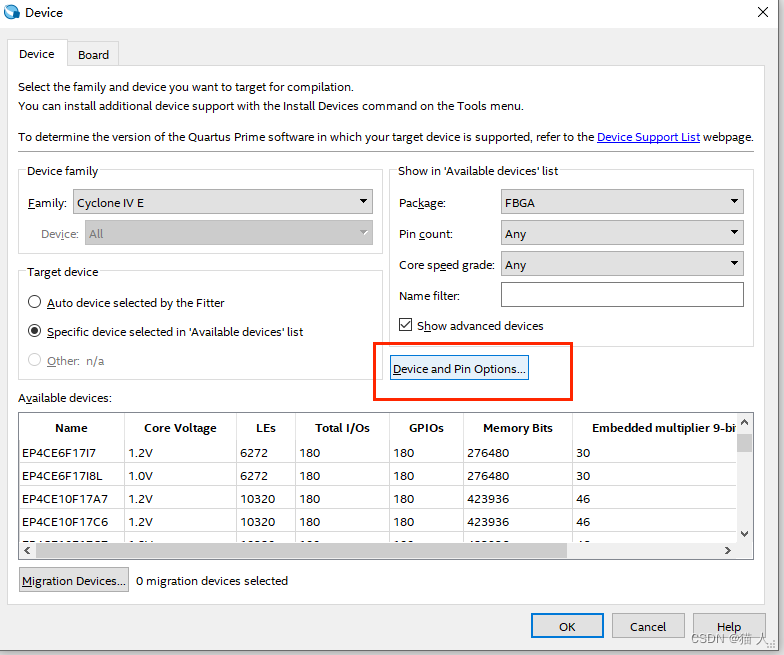

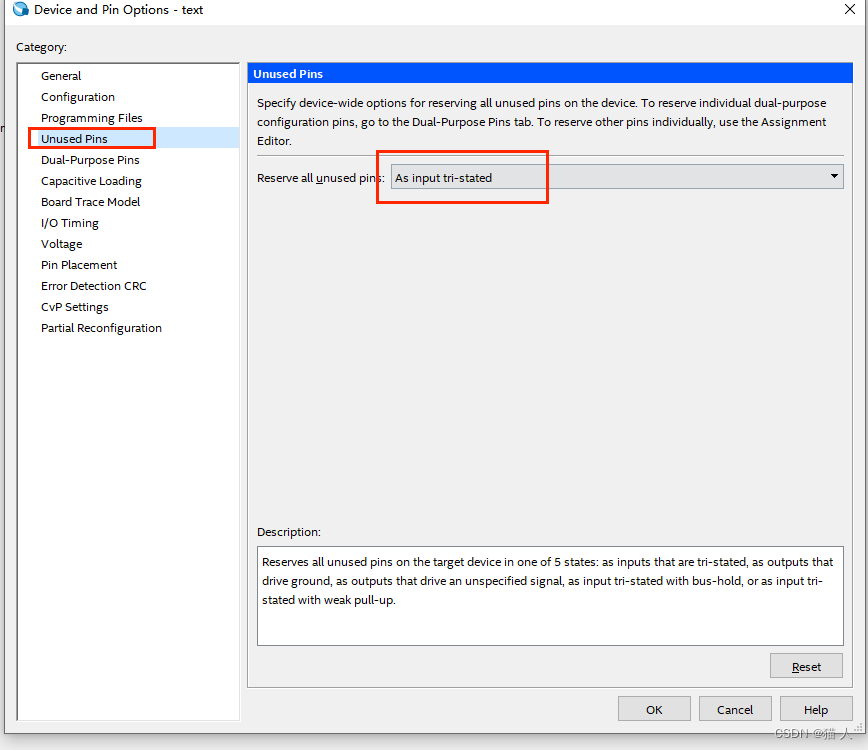

18、点击上方选项卡Assignment选择Device

选择红框的东东

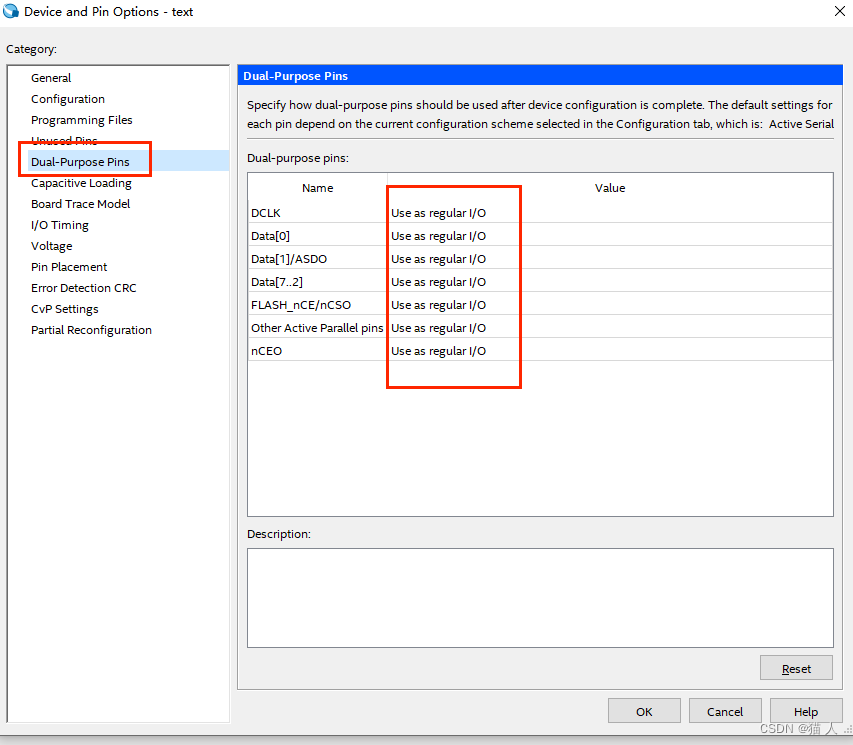

有双重使用的IO配置如图Use as regular I/O

顺便把没有使用的IO设置成高阻态,然后ok,ok,在编译就不会报错了

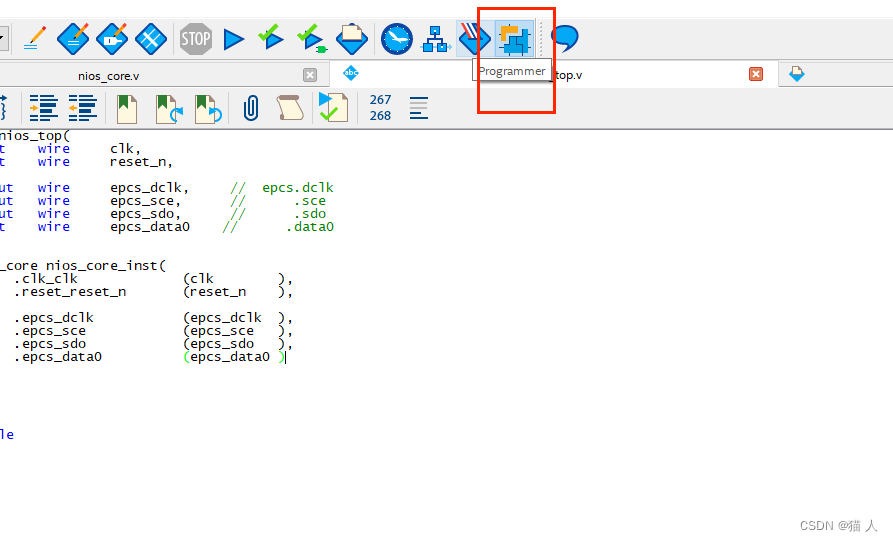

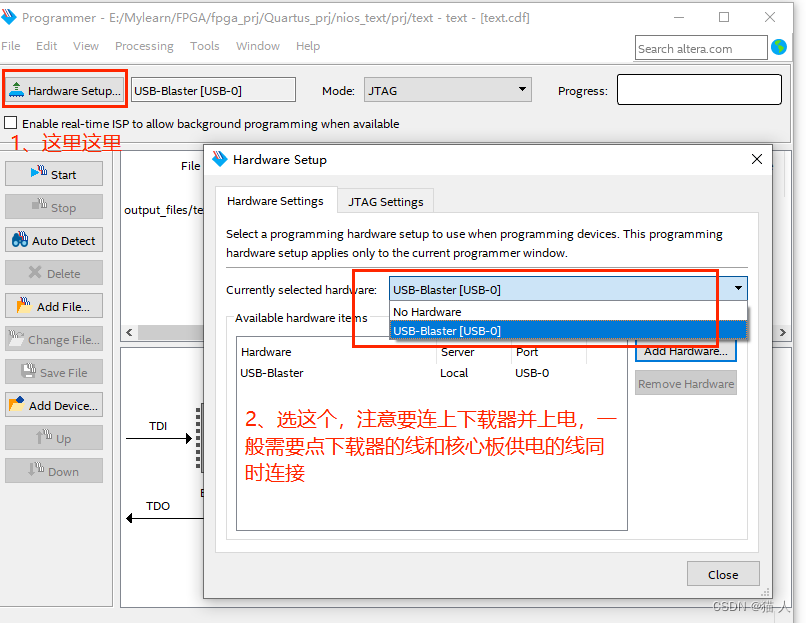

19、选择Programmer,进行下载sof文件,fpga实现硬件布局

一般会默认识别jtag,如果没有如下图。

注意:sof这个文件只能有一个,如果多了,可以右键Delete

20、如图这个样子,可以点击start了,等待成功,注意核心板不可以断电,这不是固化,断电后会硬件电路消失。下载完成后关掉Programmer,可以不保存。

三、软件部分

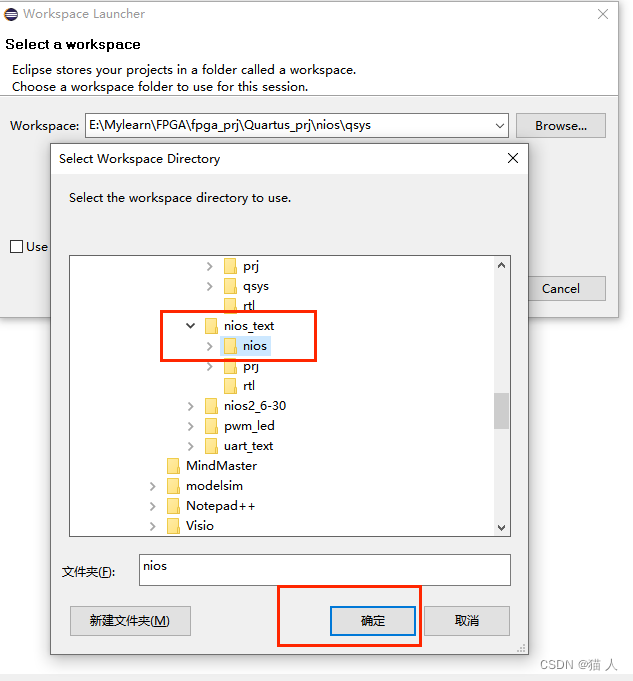

1、选择上方选项卡Tools—Nios II software Build Tools For Eclipse

路径一定要注意,因为打开默认是之前的

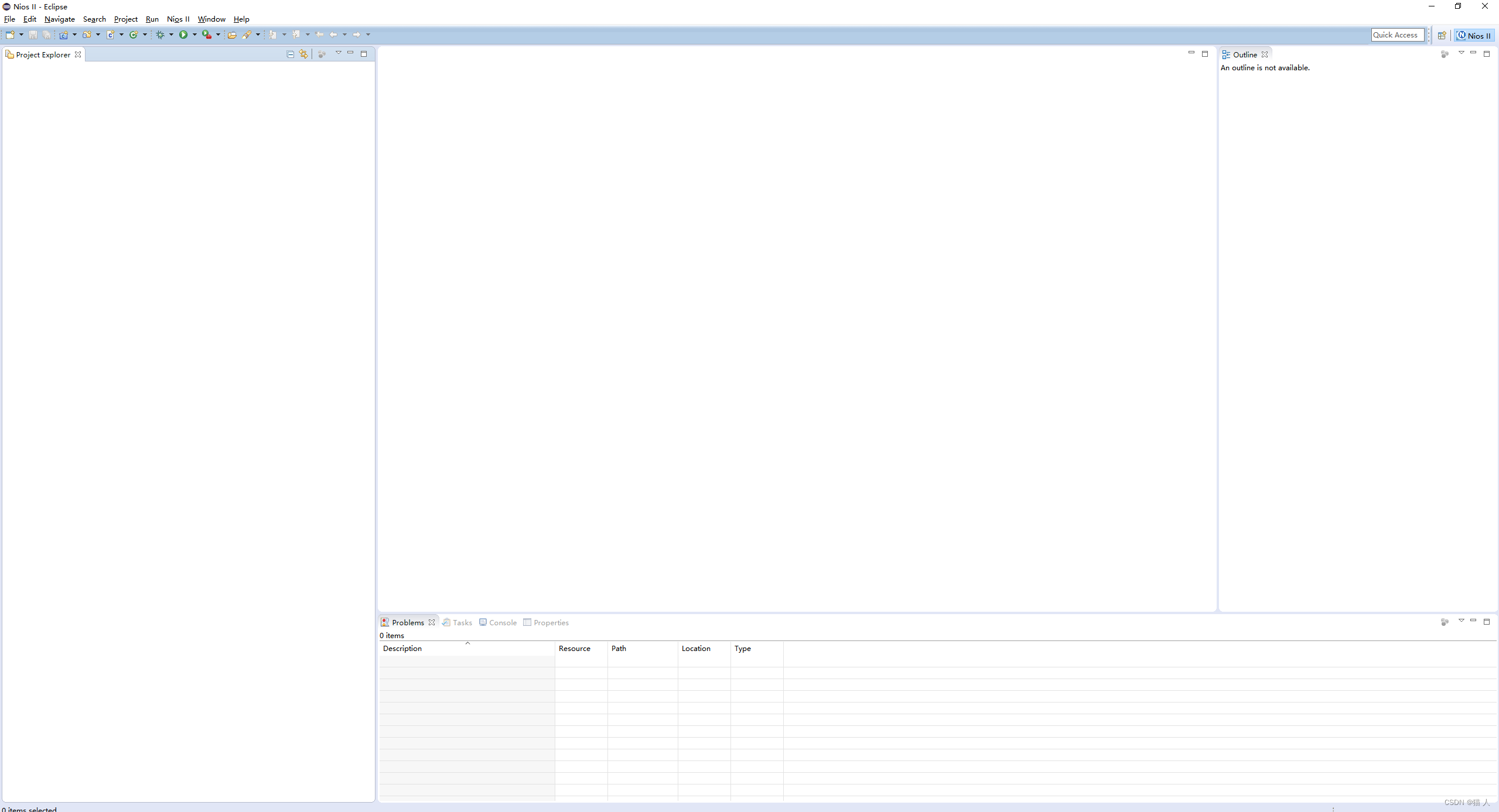

此时空空的,感觉一片茫然

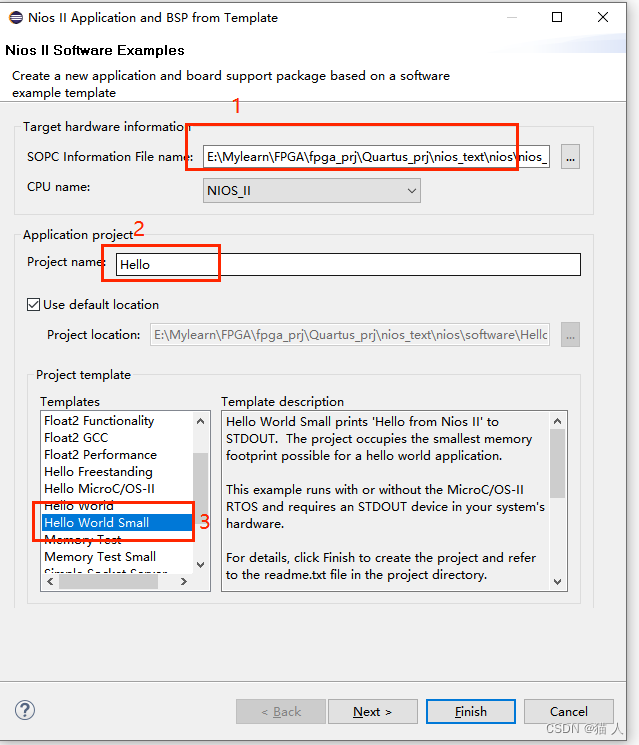

2、选一个模板,点击选项卡File–New–Nios II Application and BSP from Template

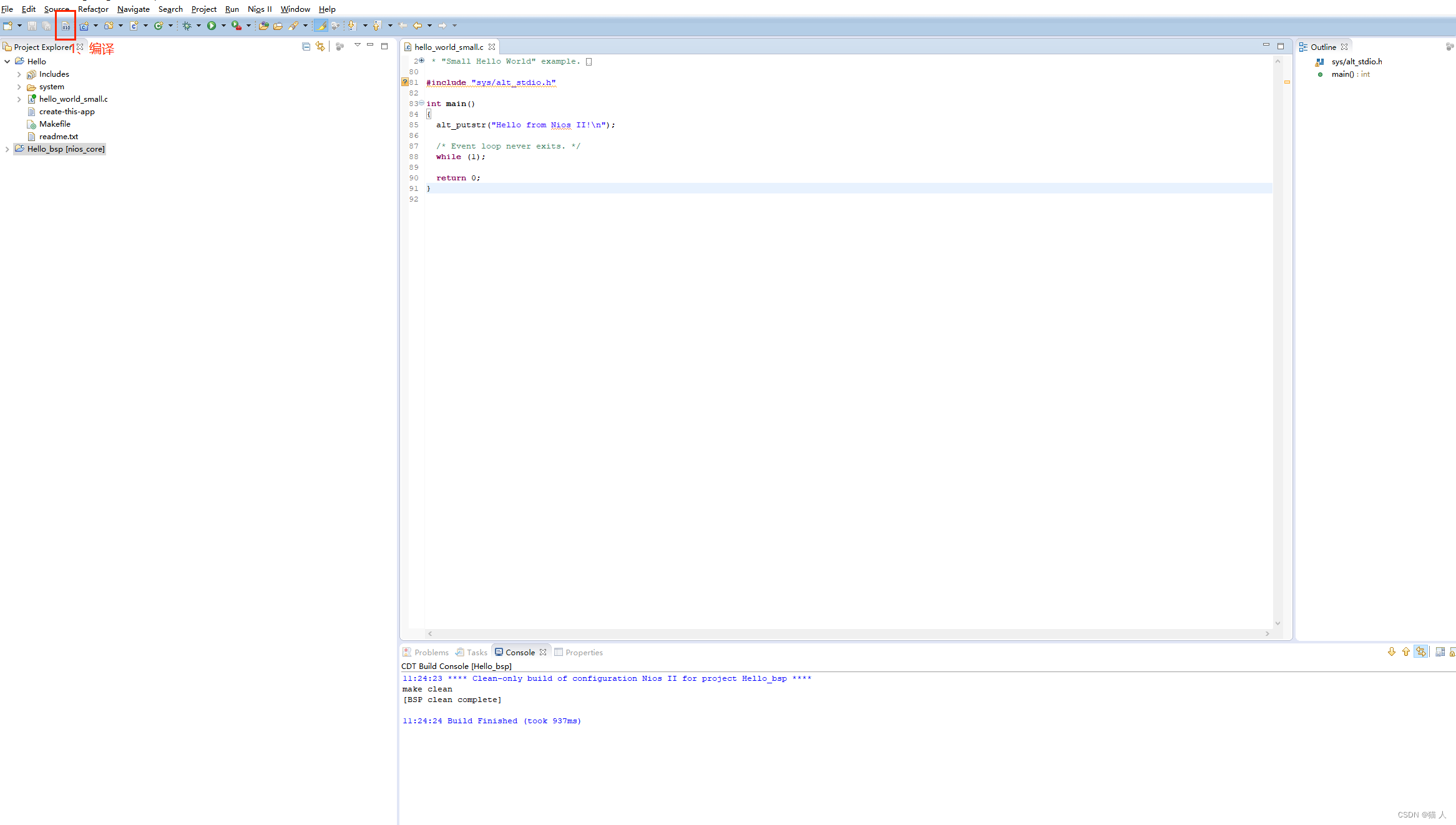

3、点击finish

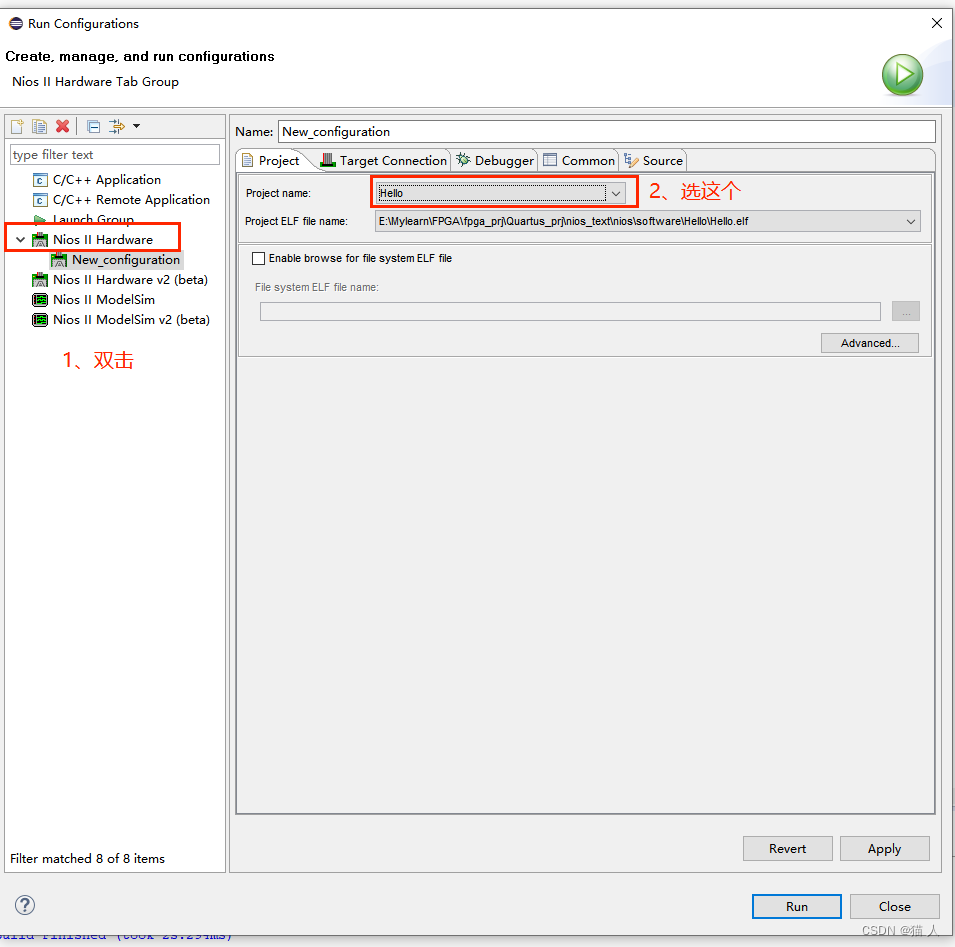

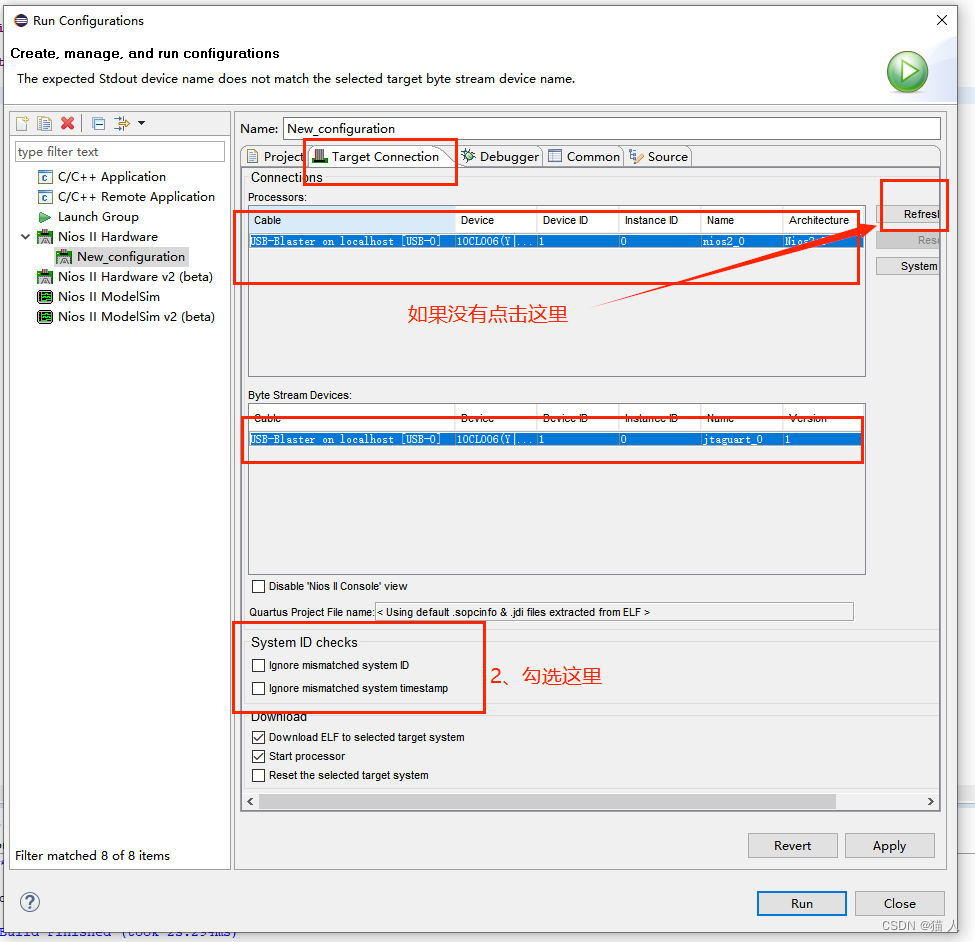

4、将程序下载进去。选择选项卡Run—Run Configurations

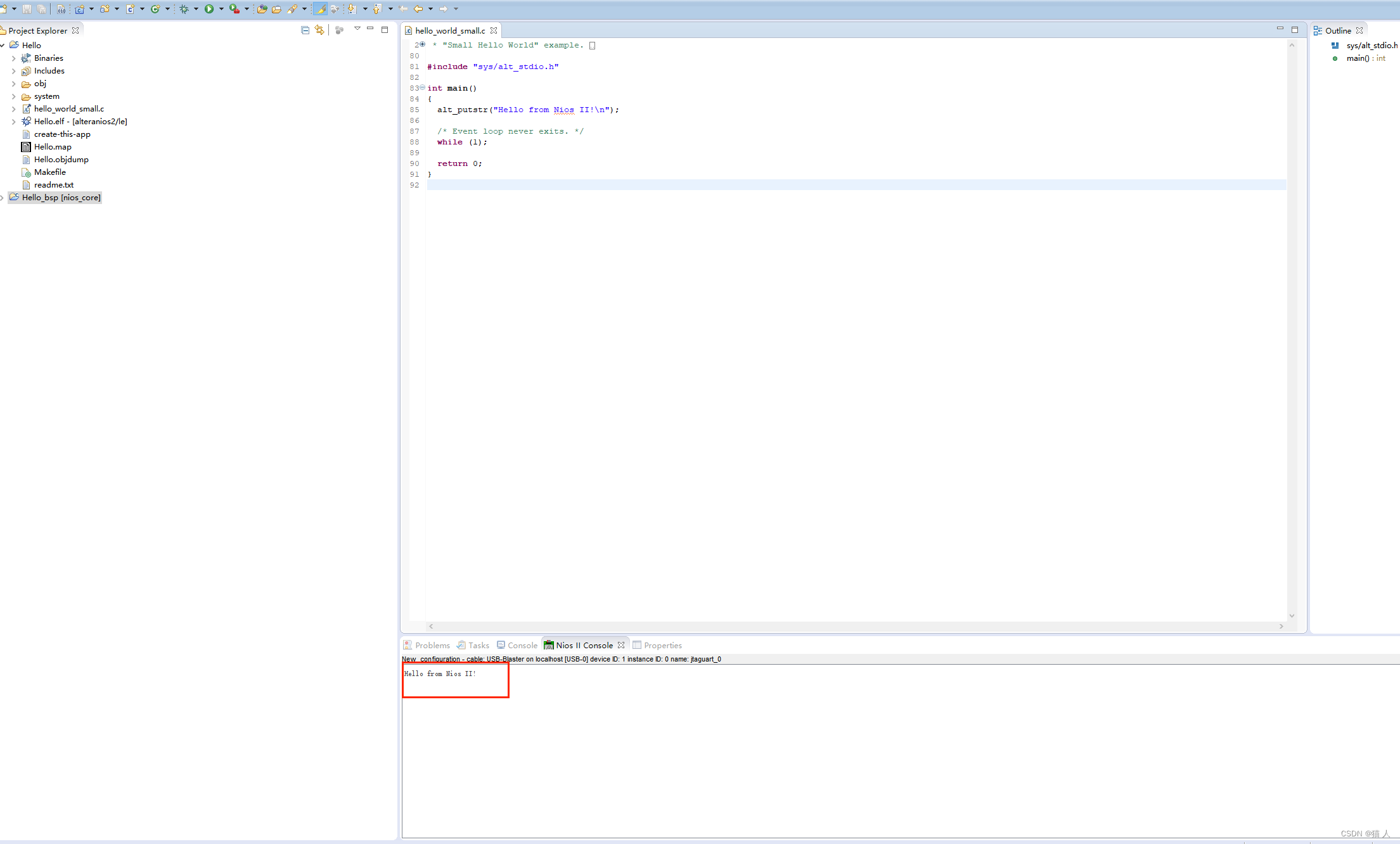

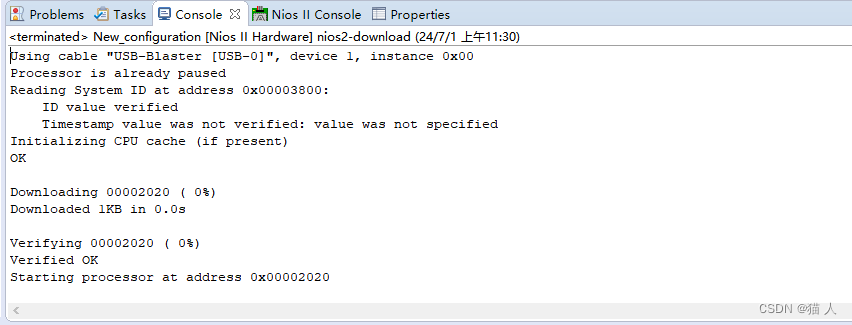

然后点击Apply ,在点击RUN,下载成功如下图

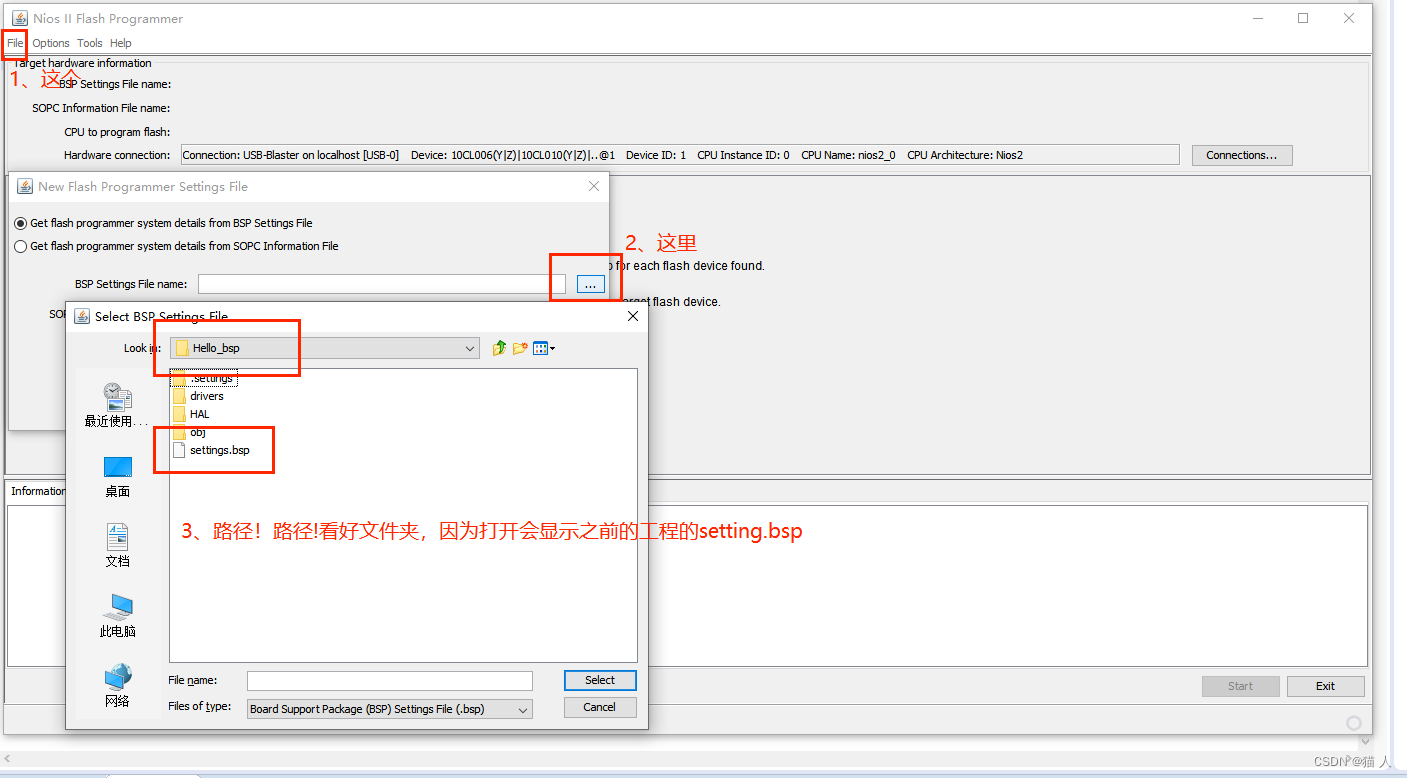

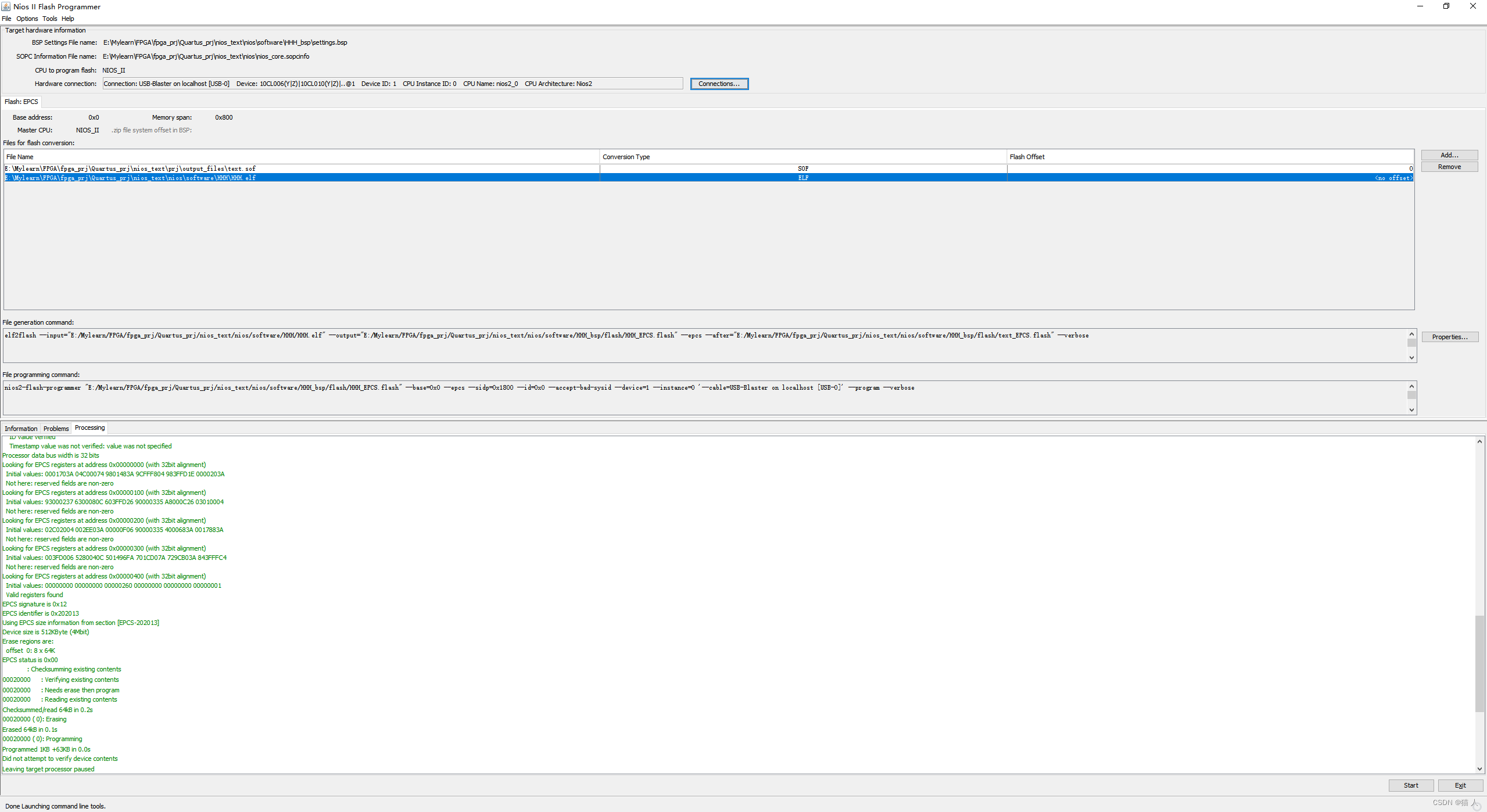

5、然后进行程序固化,选择上方选项卡Nios II----Flash Programmer,点击file-new

然后点击ok

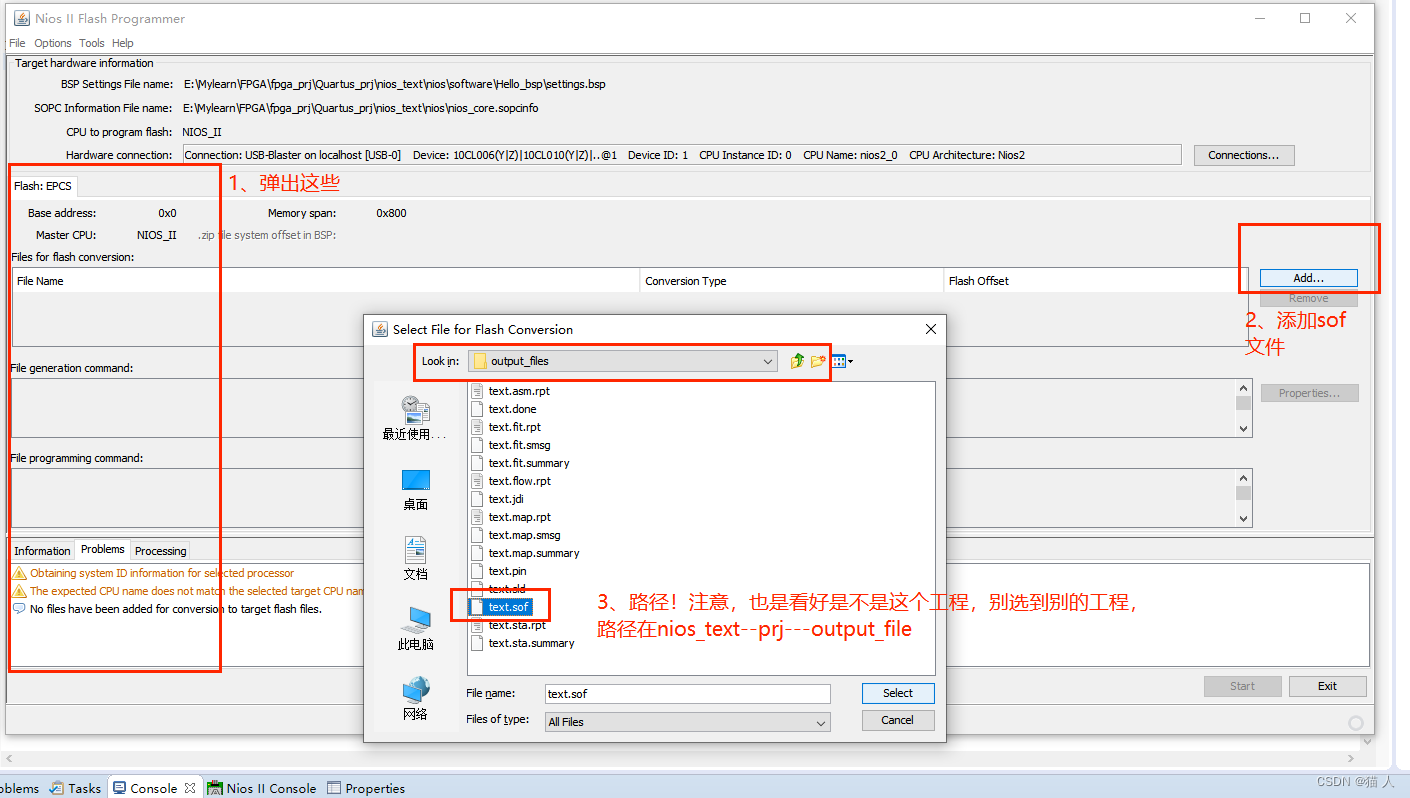

6、添加sof文件

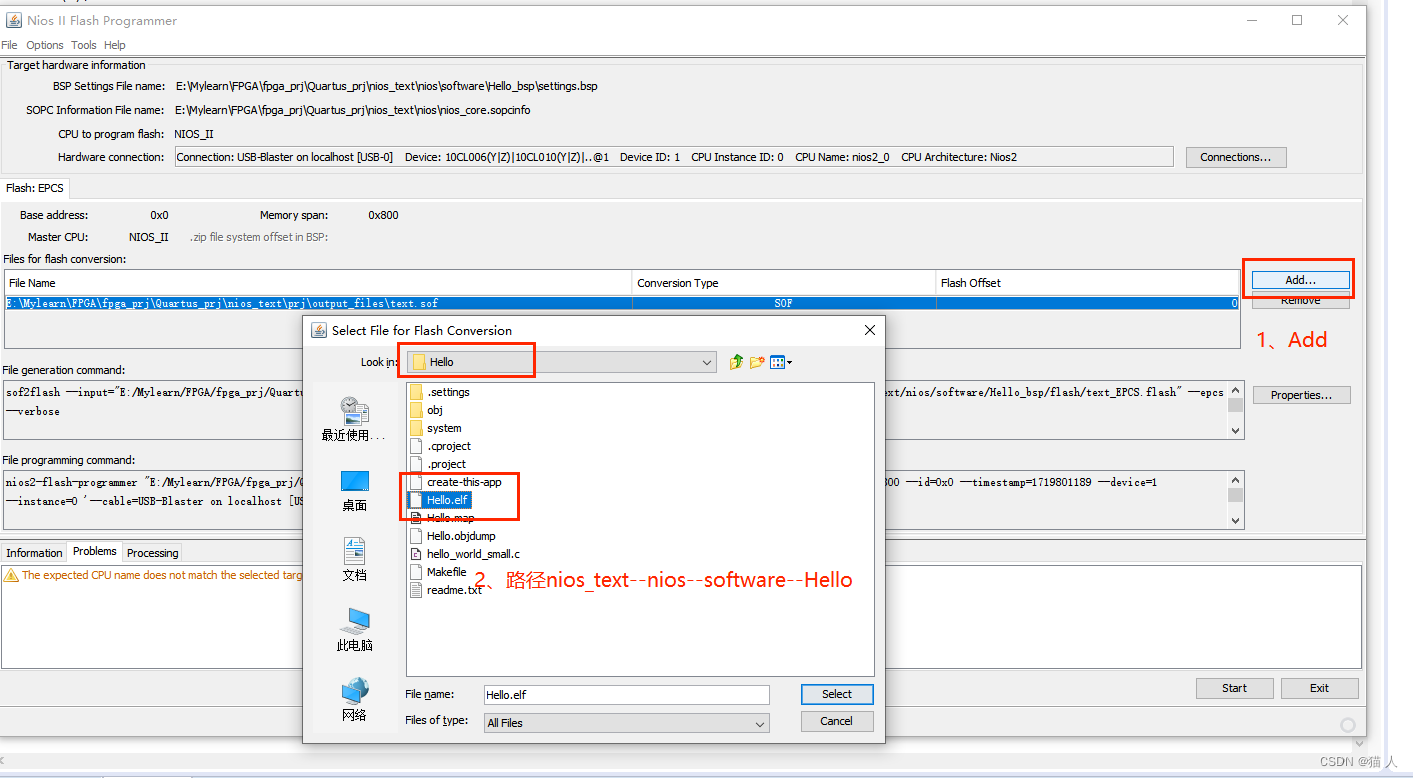

7、添加elf文件

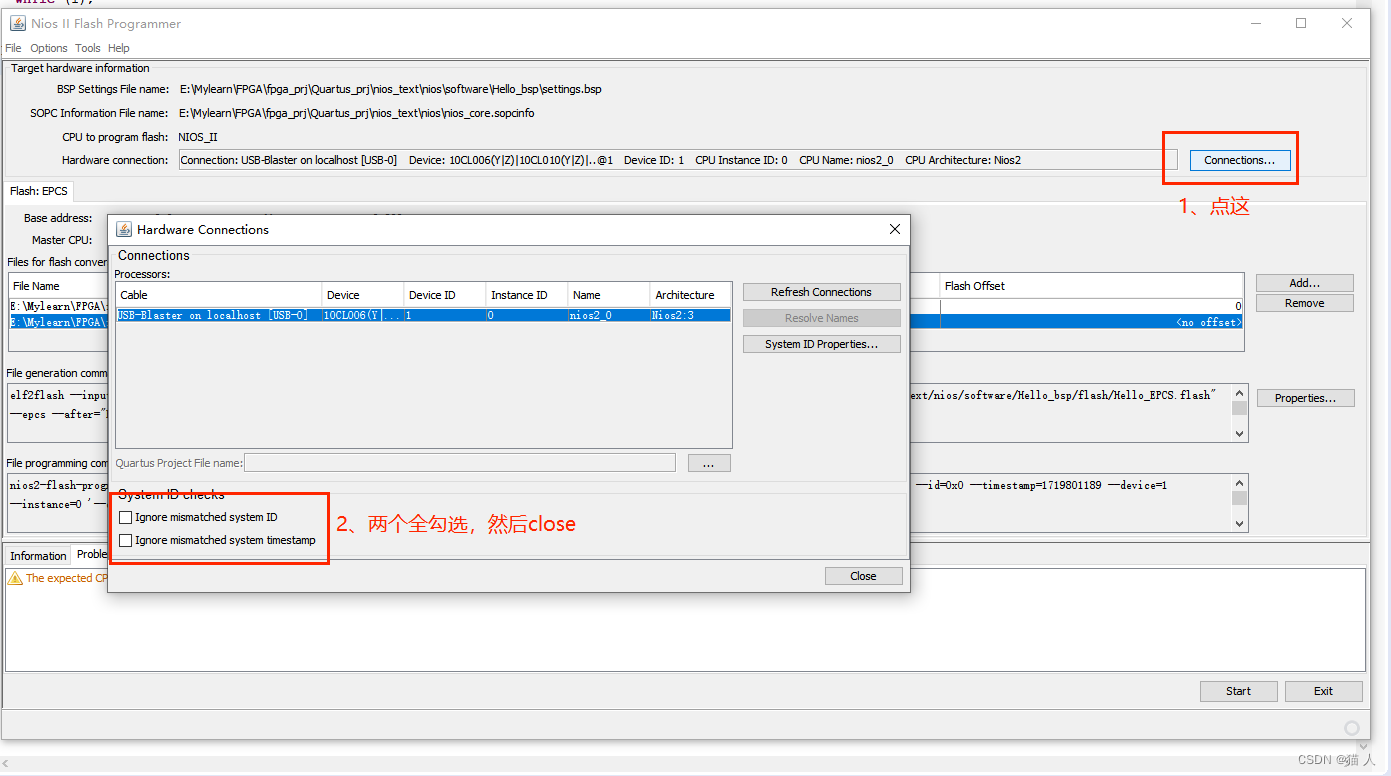

8、然后点击start,不出意外的话会报错

注意:如果不报错那么恭喜你,如果报错以下方法解决

(1)、在Quartus工程中的nios_top.v这个顶层文件移除工程,然后把这个文件剪切到prj这个文件夹中,在添加到工程(添加方法如上一样),意思就是这个nios_top.v文件要和工程放在同一个文件夹。别问,我也觉得很离谱,浪费了我一上午时间,一模一样的步骤就改一下这个文件位置就好了。

(2)、如果步骤8勾上后Erasing那里还有错,那就全部取消勾选来回试,这个软件很离谱,也可能是我水平问题。

(3)、改完位置还是不行,检查路径有没有中文,空格,如果都没有,只能在重新建一下了。

9、以下是固化成功的结果。

1525

1525

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?