NIOS II 程序flash固化

这两天尝试着NIOS II程序固化,遇到很多问题,在网上搜索资料也没有一个统一的固化方法,各种尝试都已失败告终。本人结合自己的经验,将NIOS II 程序固化方法记录下来。分享发表希望以自己的成功案例给NIOS II开发者解决程序固化这方面的问题。

alteral官网关于NIOS II程序flash少些提供的手册描述支持两种程序固化方法。一种EPCS flash固化,一种CFI flash固化。本文分别对这两种固化方法进行描述。最后介绍将elf和sof合并成jic文件稍写至EPCS。本人的开发平台是quartus 14.1版本,NIOS的开发使用的是QSYS平台。

本人默认为读者熟悉quartus开发平台和NIOS II软核开发.

第一部分 EPCS flash固化

EPCS flash主要用于固化FPGA的配置文件,与FPGA以SPI总线进行数据交互,在NIOS II软核开发过程中,可以将FPGA的配置文件和NIOS II应用程序一起固化置EPCS flash。本人的片子使用的是EPCS64N。

具体固化步骤如下:

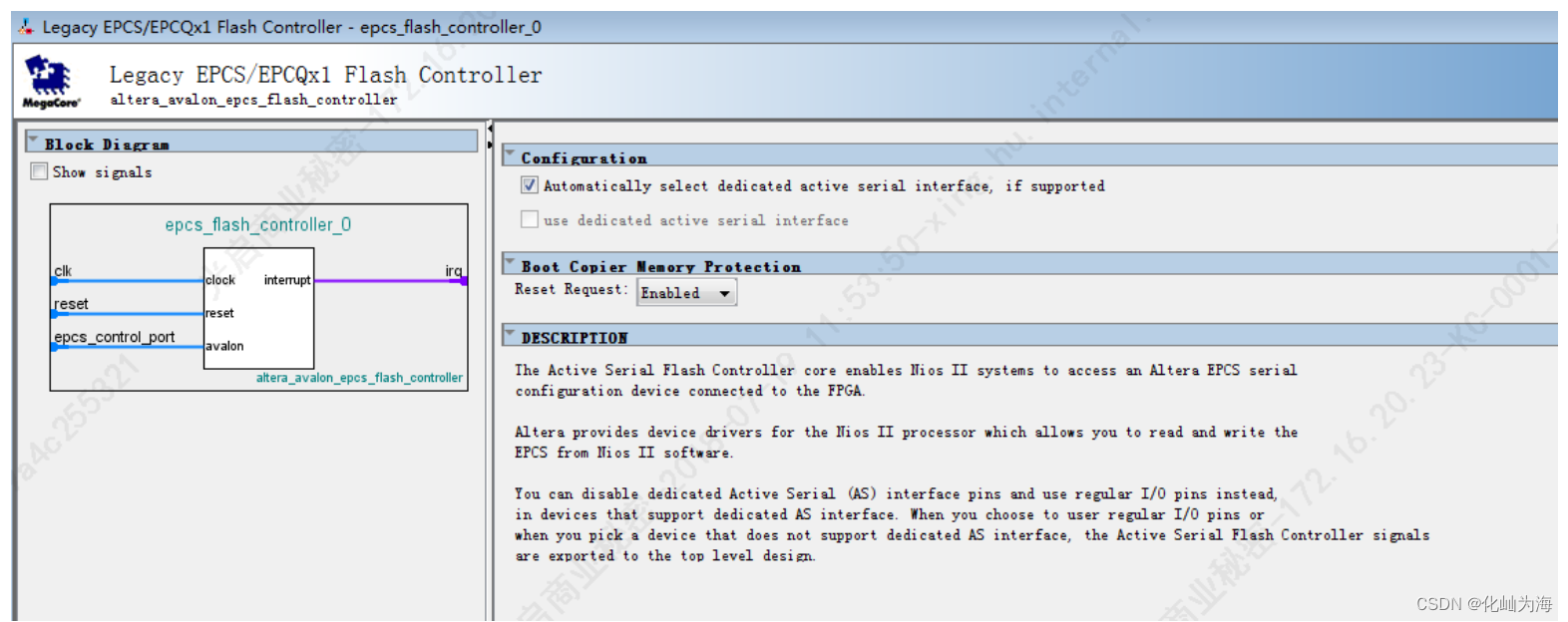

第一步:创建EPCS控制器

EPCS flash固化需要在搭建好NIOS软核后创建EPCS控制器,quartus 14.1的版本创建如图所示:

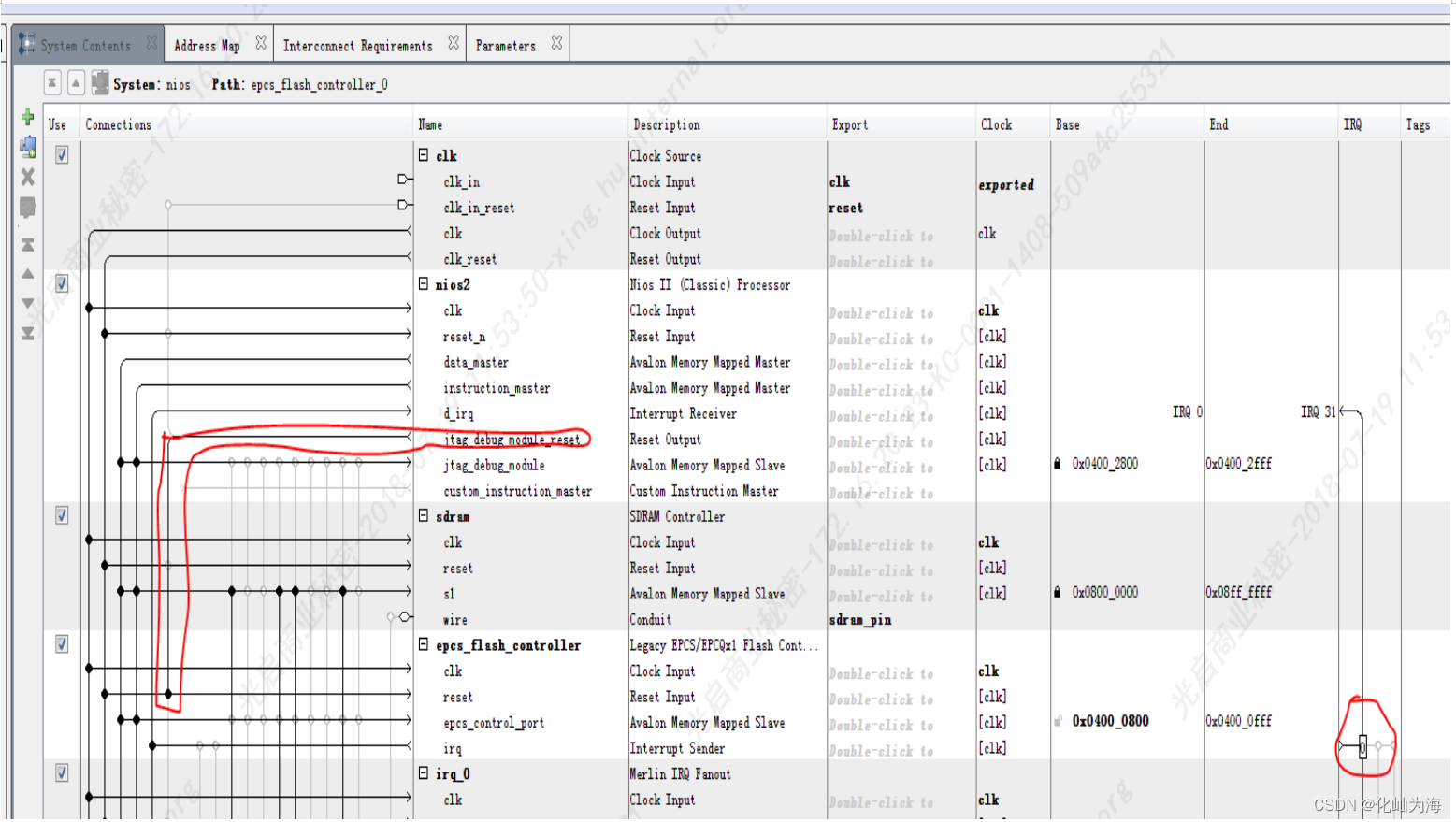

选择默认方式即可。生成EPCS控制器后,按照下图方式连接到NIOS软核和并设置中断号为0。具体连接方法如EPCS连接图所示:

注意:

1、网上很多资料需要将EPCS的SPI引脚迁出,并需要对quartus进行相关设置。本人认为应该是SOPC的开发方式。在quartus 14.1的版本中默认加载EPCS控制器时没有SPI控制引脚。因为alteral已经优化这部分设计,在工程编译间断会自动连接至SPI引脚,且不需要设置时序。且并有要求EPCS的地址必须从0开始。本人使用的是随机地址,并没有设置EPCS的地址为0。

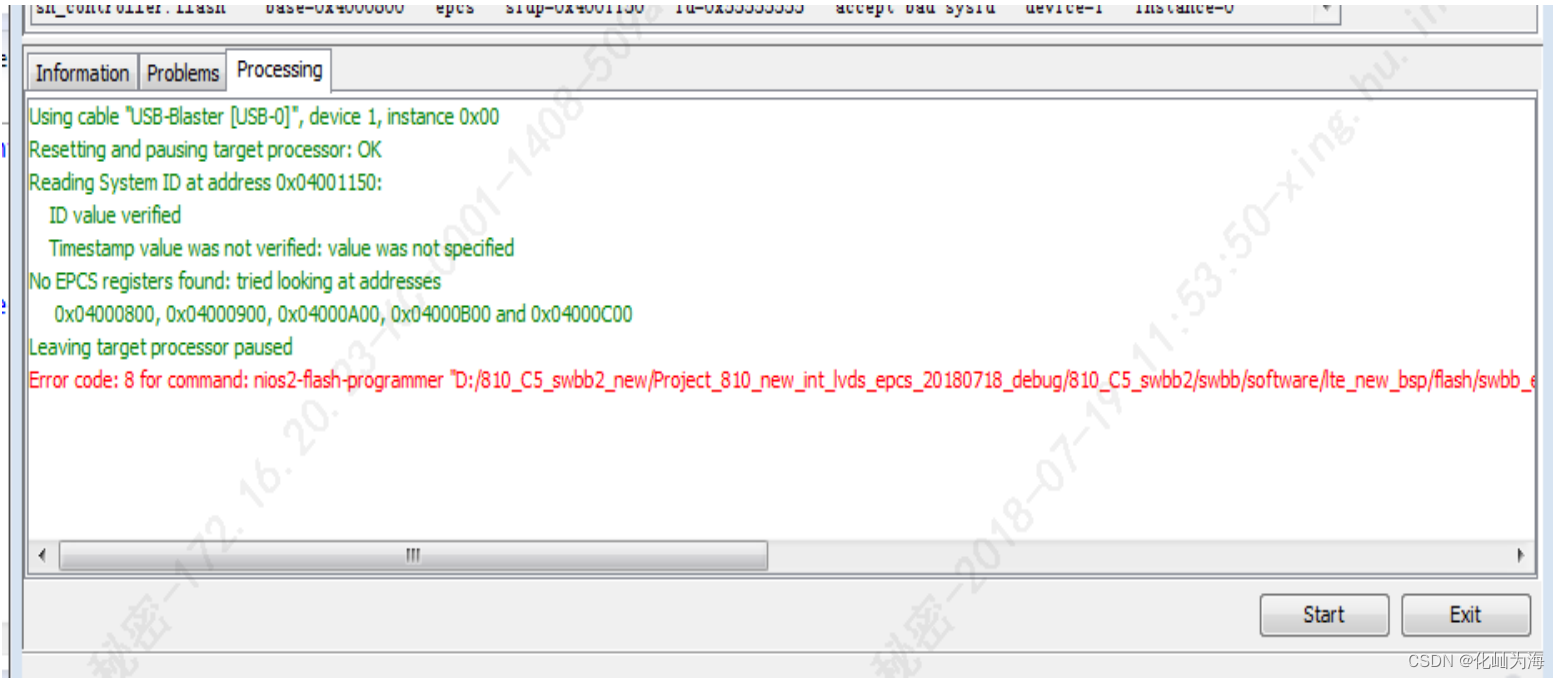

2、在连线的时候需要把NIOS软核的jtag_debug_module_reset引脚和EPCS的复位引脚相连。不然会稍写失败报出如下图(稍写失败提示)故障。

3、必须要将EPCS的中断编号设置为0,以保证EPCS的中断级别为最高。不然会稍写失败报出如下图(稍写失败提示)故障。

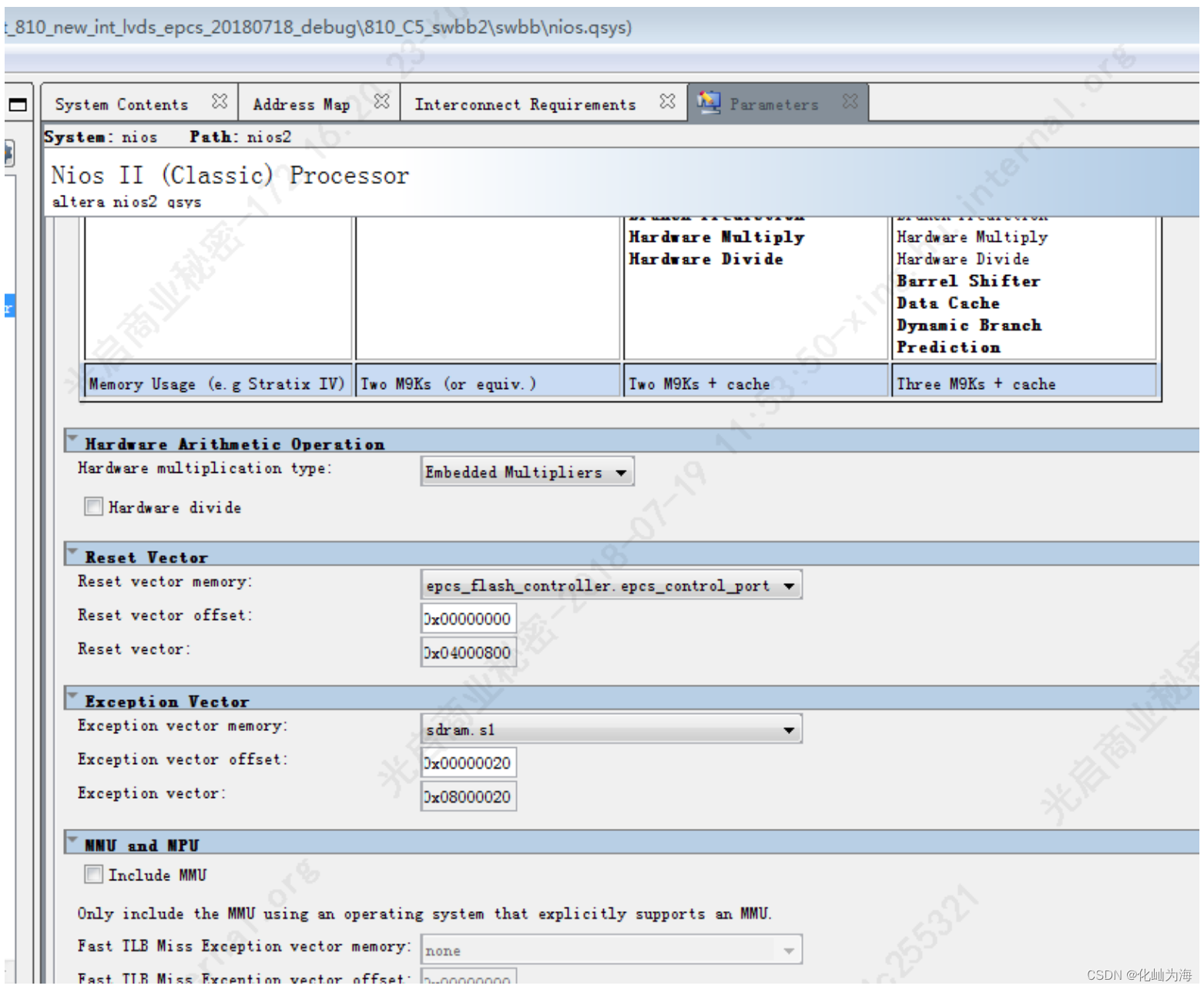

第二步:设置NIOS软核配置

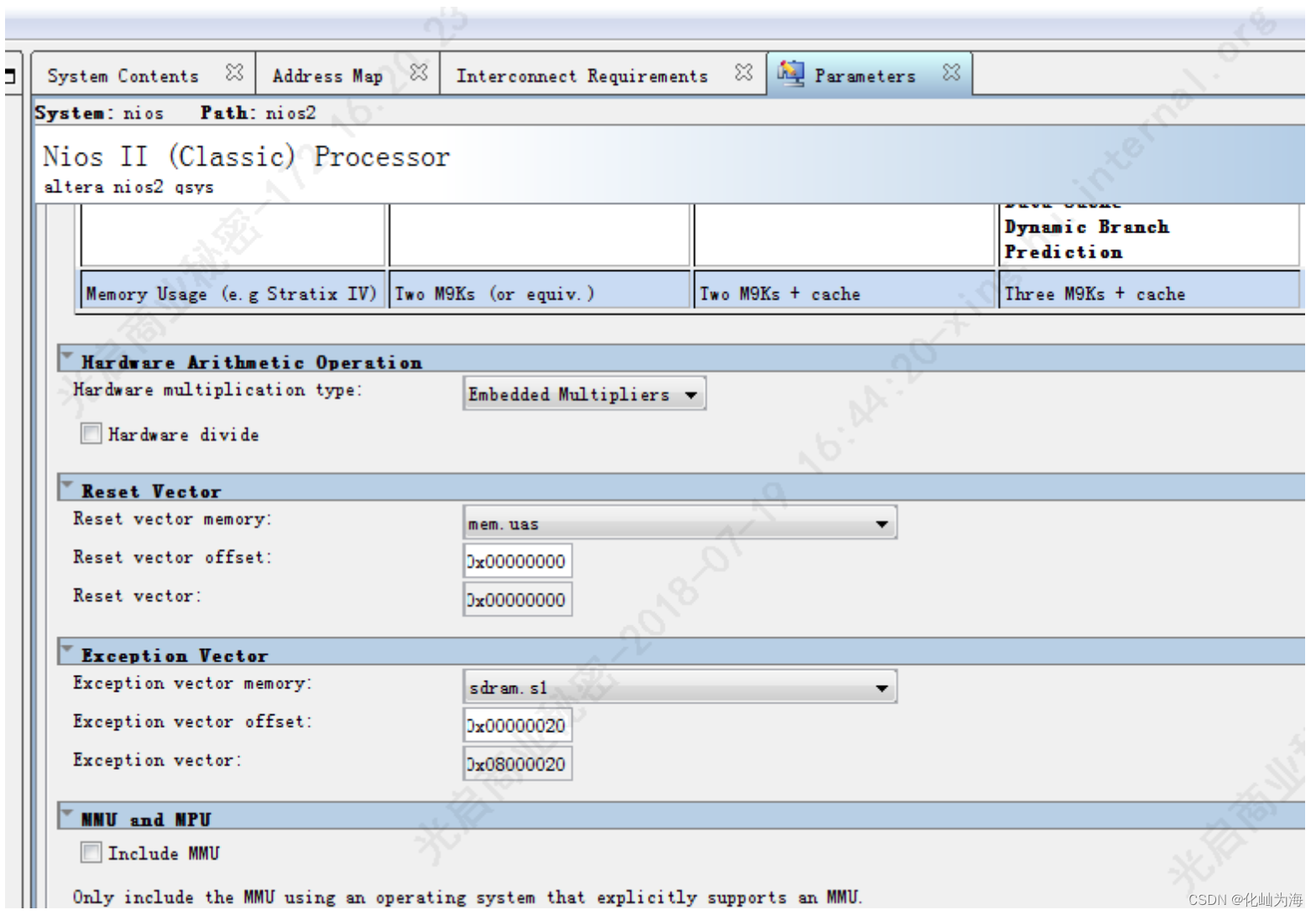

EPCS与NIOS软核连接好后,给EPCS控制器分配地址空间。接着配置NIOS软核复位向量为EPCS控制器地址空间,配置异常向量空间为SDRAM,或者on_chip_ram地址空间。本文程序运行在FPGA的片外外设SDRAM里,所以配置异常向量空间为SDRAM地址空间。具体配置如NIOS配置图所示:

第三步:eclipse配置

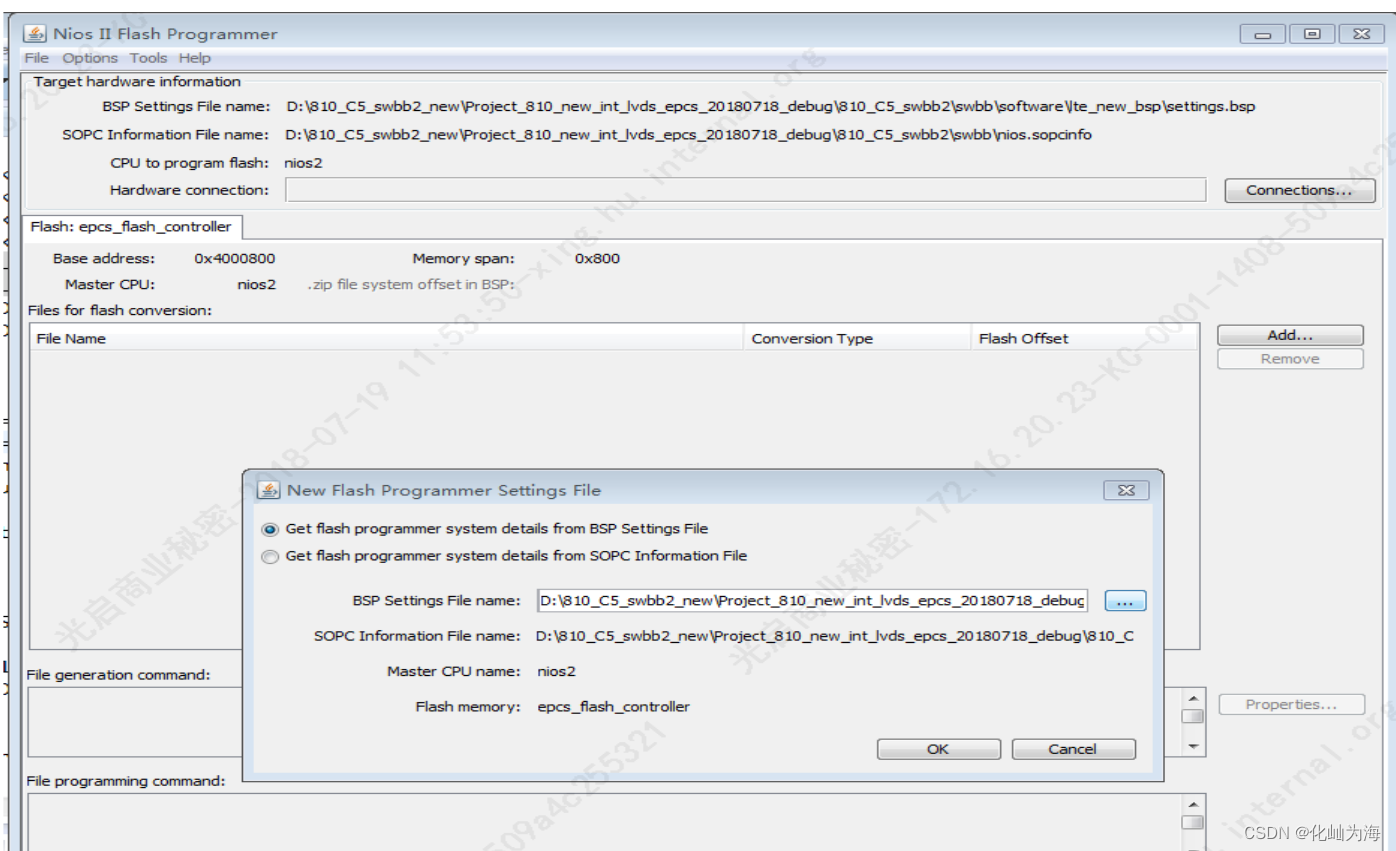

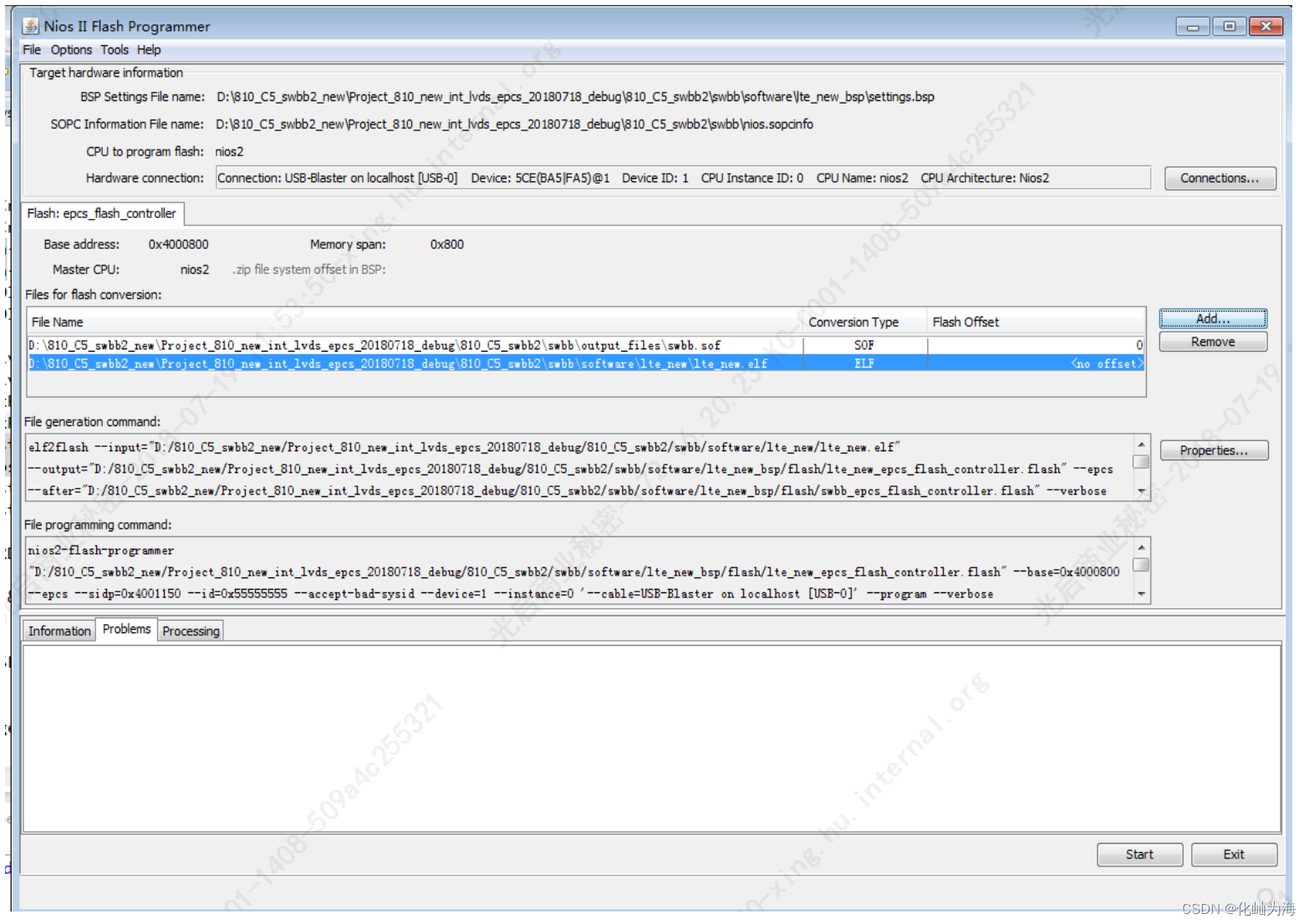

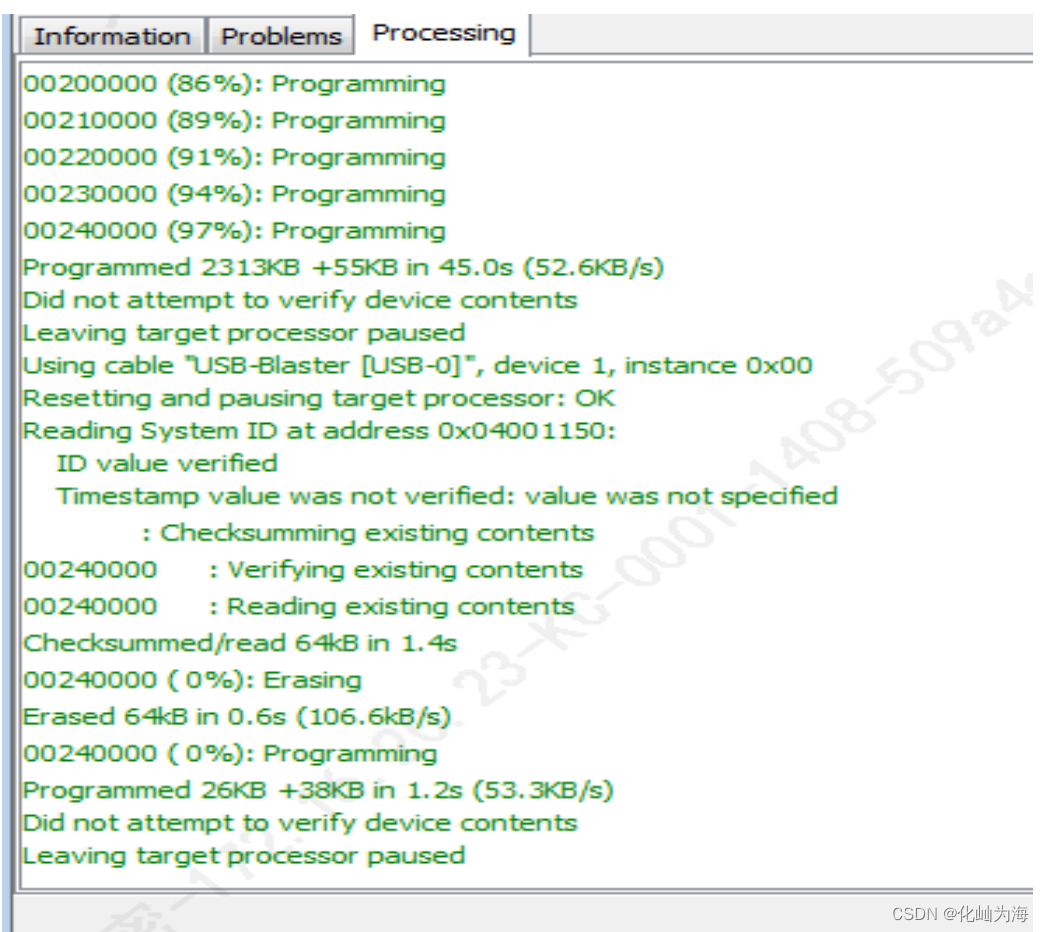

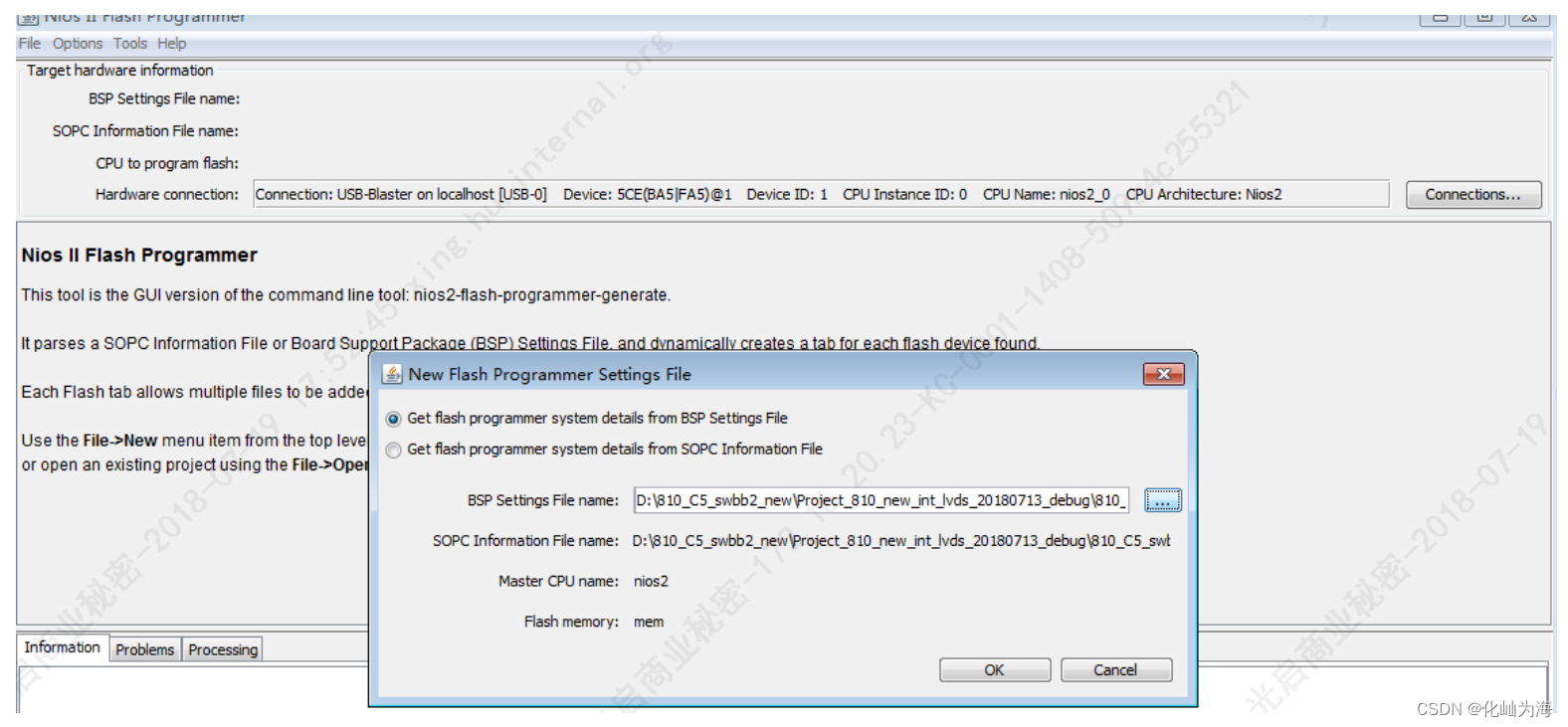

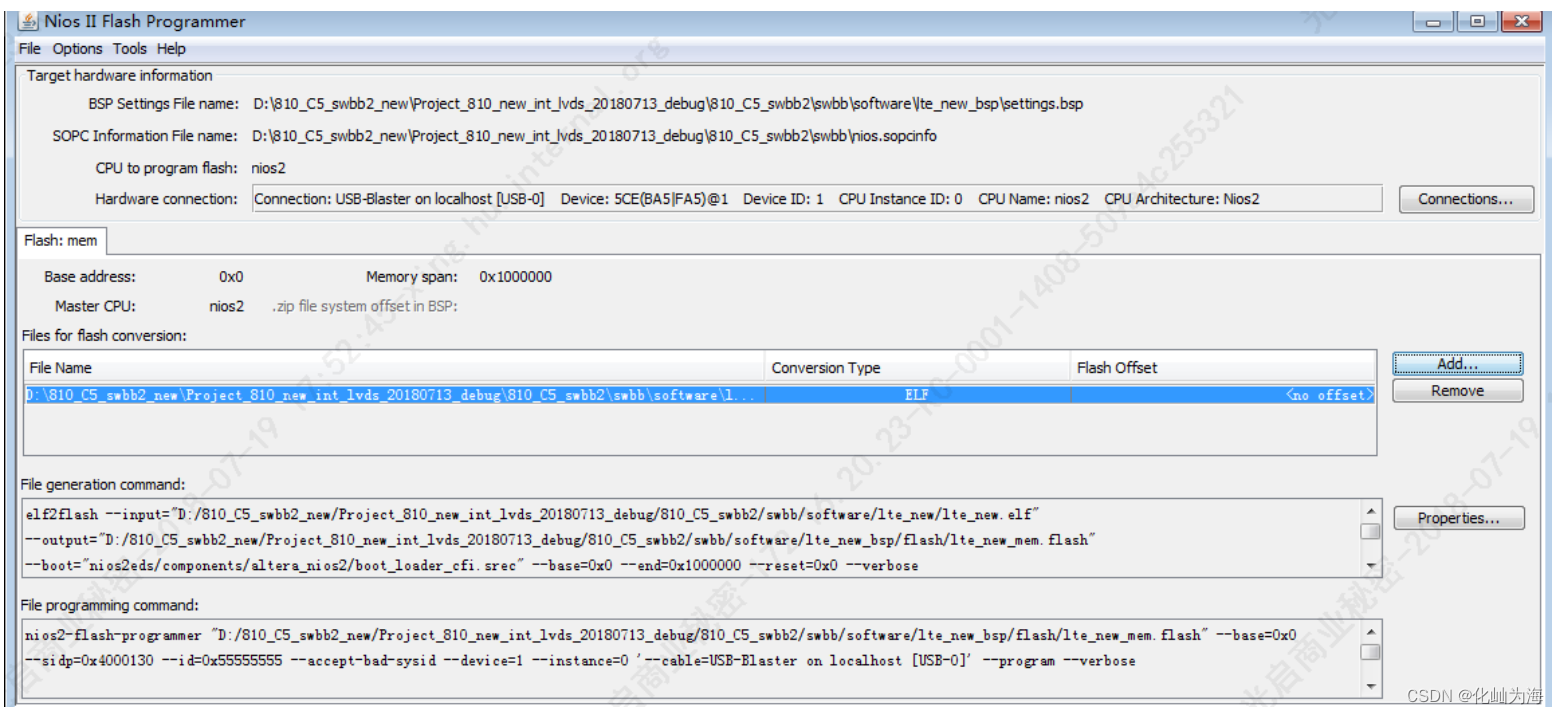

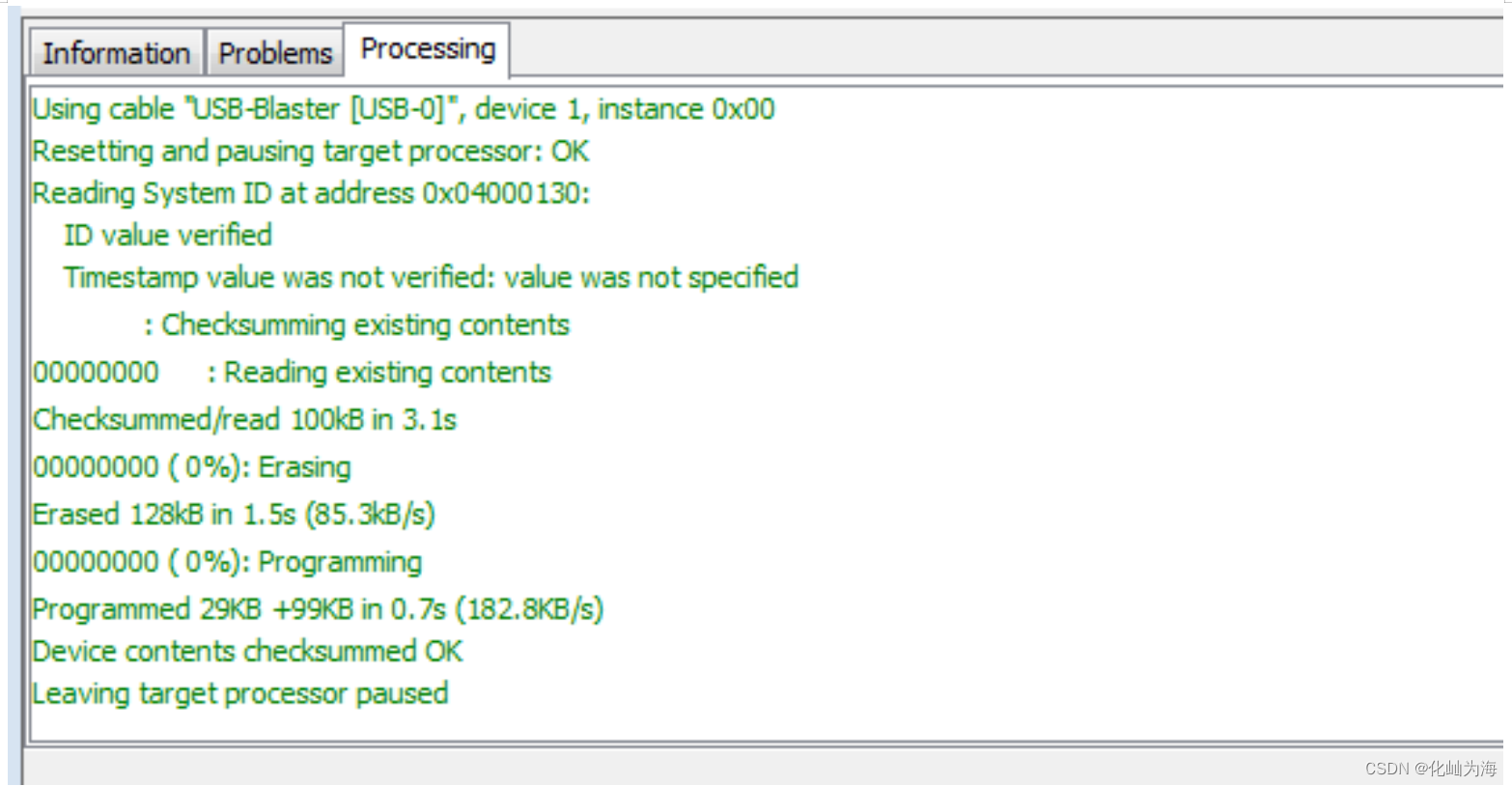

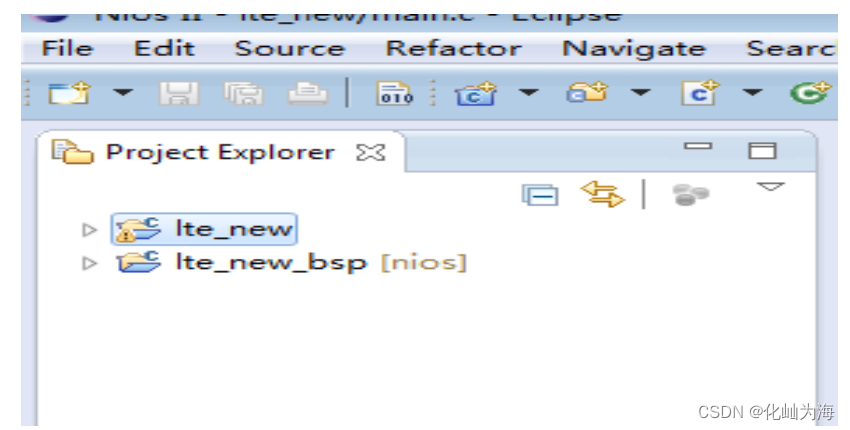

在稍写之前先将.sof文件下载至FPGA,搭建好硬件坏境。打开IDE,编辑好程序后点击IDE菜单栏的NIOS II->flash programmer,打开NIOS II flash programmer窗口。点击file->new打开New Flash Programmer Settings File窗口。添加bsp文件,如bsp文件添加图所示:

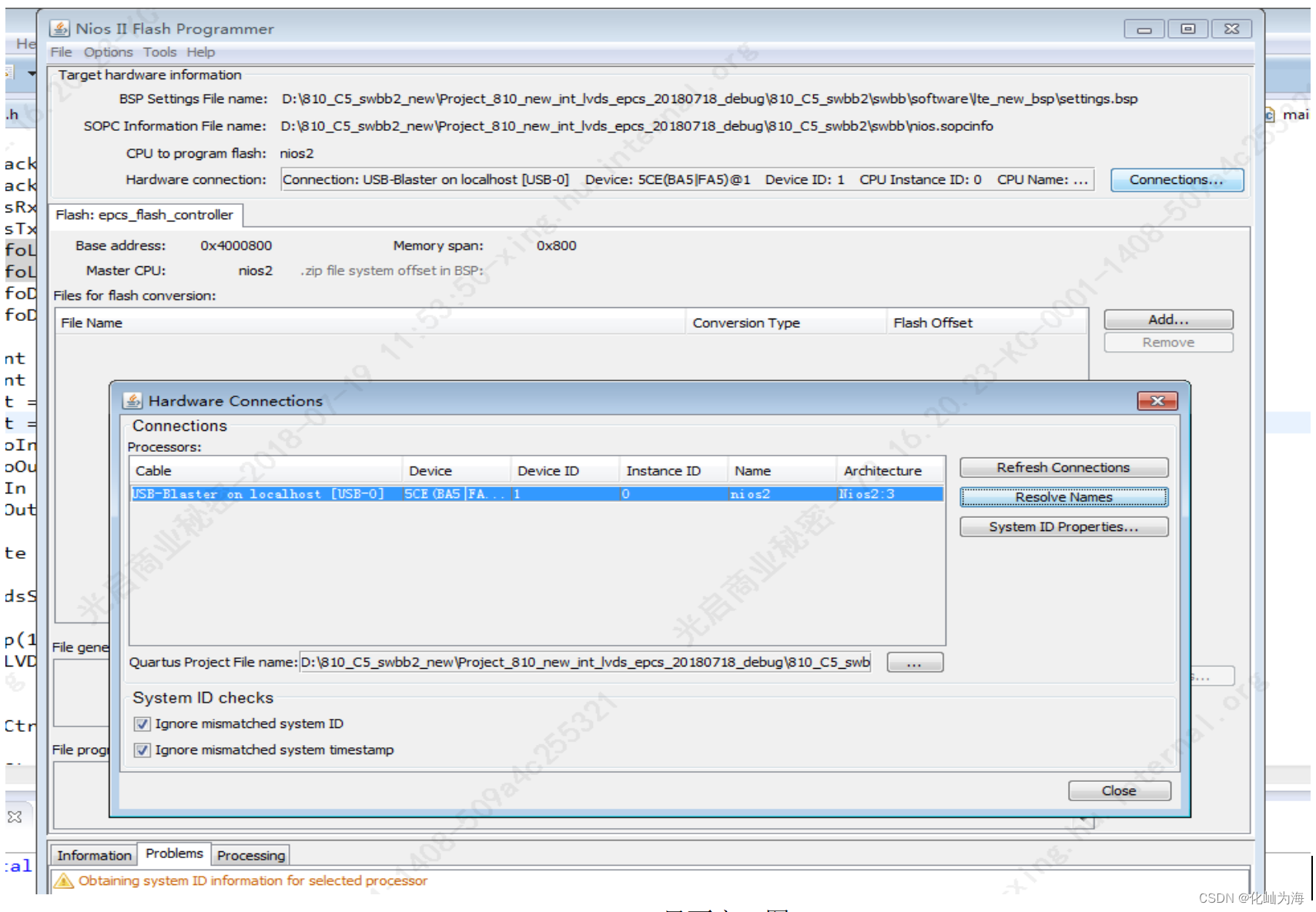

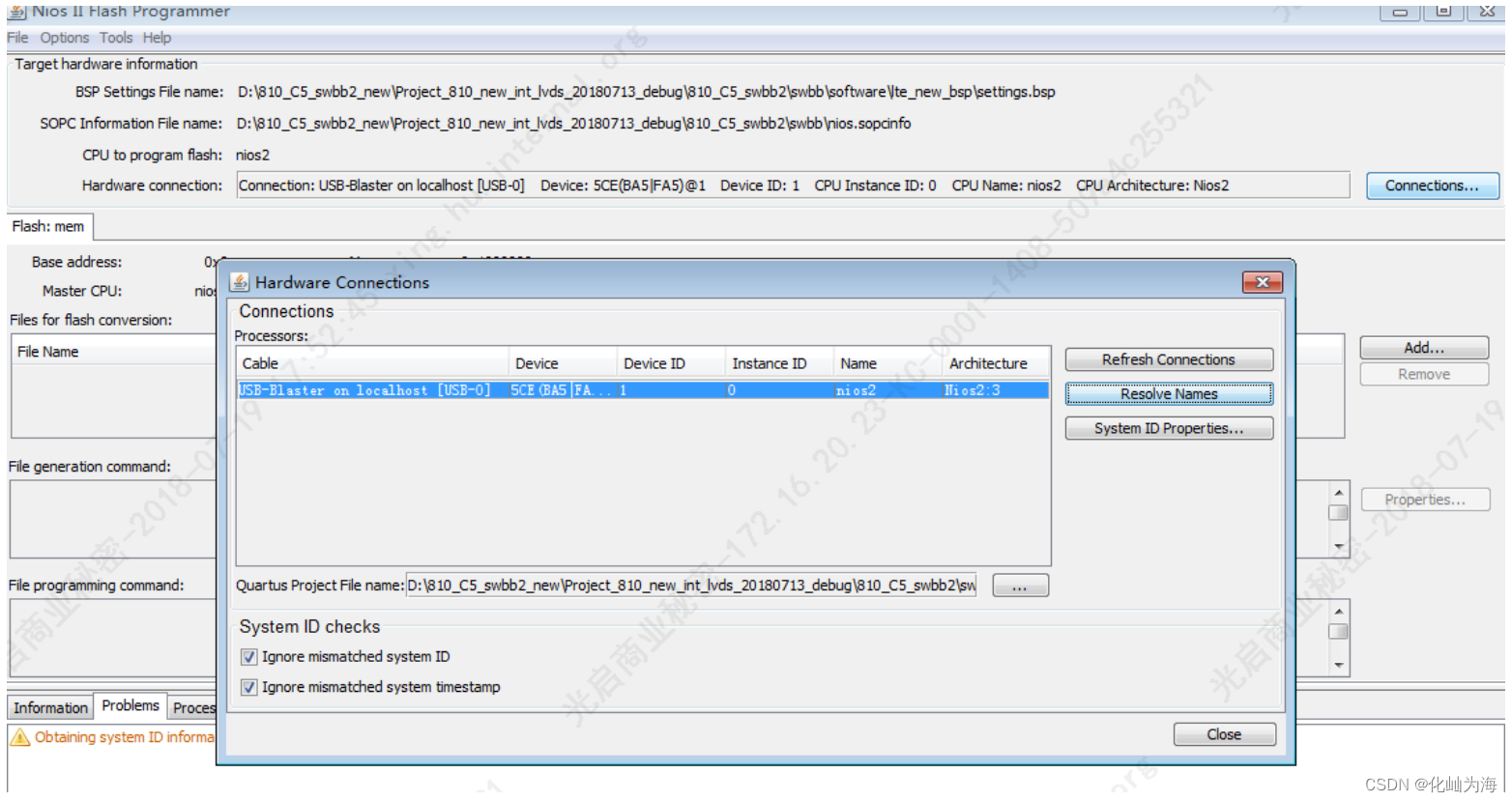

点击OK。进入New Flash Programmer Settings File窗口。点击connections…。打开Hardware Connections界面窗口(如Hardware Connections界面窗口图所示)。在Ignore mismatched system ID和Ignore mismatched system timestap前打钩。点击Reflash Connections按钮更新连接。出现黄色警告可以忽略。红色表示错误。

第二部分 CFI Flash程序固化

与EPCS flash稍写相比CFI Flash固化最大不同点在于FPGA配置文件和应用程序分开存放。EPCS将带有SPI接口的flash分成两个区域,分别存放FPGA配置文件和NIOS应用程序。而CFI Flash程序固化,则是将FPGA的配置文件存放在EPCS中,NIOS应用程序存放在带有CFI接口的Flash存储器中。而在quartus ii 14.1的版本中通过三态控制器连接外部flash。需要加普通的三态控制器接口改为CFI接口。最后连接到外部flash芯片引脚。下面分步介绍CFI Flash程序固化的过程。

第一步:CFI接口添加与时序配置

在Qsys界面中添加Generic Tri-State Controller(三态控制器)和Tri-State Conduit Bridge(三态流桥),连接时钟和复位信号连线。将三态控制器的uas连接至Avalon-MM Pipeline Bridge的m0信号线(本人项目使用Avalon管道桥)或者直接将uas连接到NIOS软核的数据线和指令线。将三态控制器的tcm信号线与三态流桥的tcs信号线连接在一起。到出三态流桥out信号,用于连接外部flash引脚。具体连接方式如三态控制器连接图所示,设置好三态控制器的相关信号以及时序。给三态控制器分配地址空间锁定改地址空间。本项目设置为从0地址开始的地址空间,并且锁定该地址空间。

第二步:设置NIOS软核配置

点击NIOS组件,进入NIOS软核配置窗口。配置软核复位向量为三态控制器地址空间,配置异常向量空间为SDRAM,或者on_chip_ram的地址空间。本文程序运行在FPGA的片外外设SDRAM里,所以配置异常向量空间为SDRAM地址空间。具体配置如NIOS配置图所示:

sof2flash --input=.sof --output=hwimage.flash --epcs --verbose

elf2flash --input=.elf --output=swimage.flash --epcs --after=hwimage.flash --verbose

每步转换完成后输入ls命令均可看到新生成的文件(hwimage.flash或者swimage.flash)。

2.把flash文件转换成hex文件。先后输入以下命令:

nios2-elf-objcopy -I srec -O ihex hwimage.flash hwimage.hex

nios2-elf-objcopy -I srec -O ihex swimage.flash swimage.hex

输入ls命令可以看到新生成的hex文件。

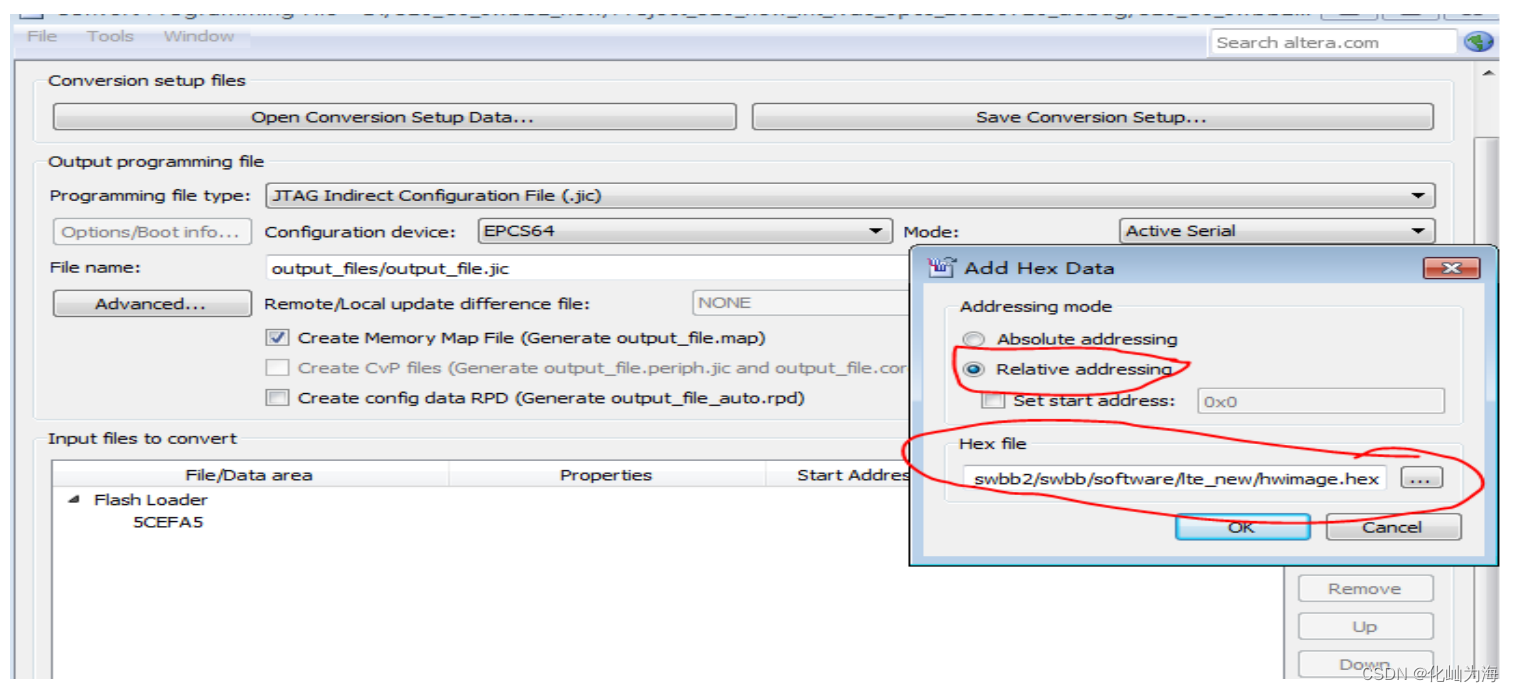

3.打开quartus II的Convert Programming File工具给FlashLoad添加 器件类型然后添加hex文件,先添加hwimage.hex再添加swimage.hex文件。添加文件时选择相对地址。如下hex文件添加图所示。

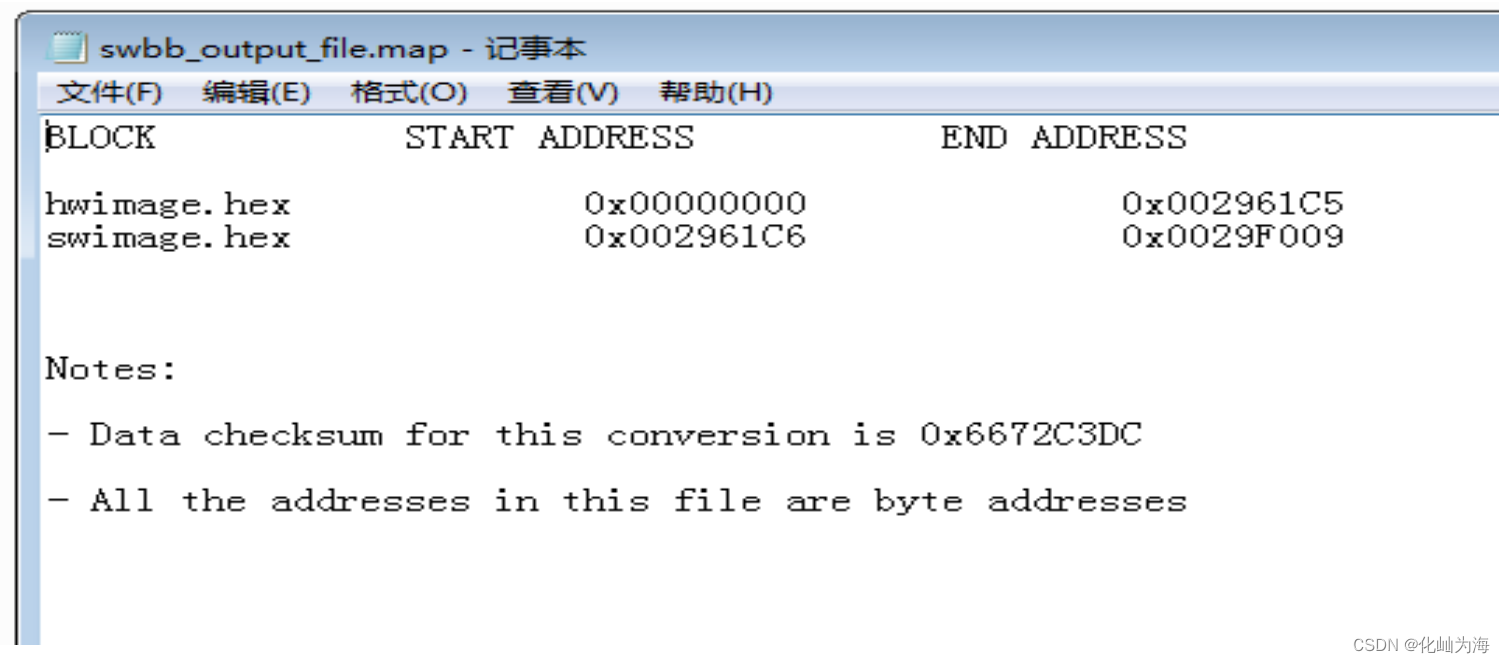

4.最后点击Gererate,即生成jic文件。再检查生成的.map文件有 hwimage.hex在起始地址0x0,swimage.hex文件在hwimage.hex结束后的地址。如下图map内容显示图所示:

文章详细介绍了如何进行NIOSII程序的EPCS和CFIFlash固化过程,包括EPCS和CFI控制器的创建与配置,NIOS软核设置,Eclipse的配置以及程序写入步骤。同时,文中提供了遇到的问题及解决方法,并提到了SOF和ELF文件合并生成JIC文件的高效固件写入方式。

文章详细介绍了如何进行NIOSII程序的EPCS和CFIFlash固化过程,包括EPCS和CFI控制器的创建与配置,NIOS软核设置,Eclipse的配置以及程序写入步骤。同时,文中提供了遇到的问题及解决方法,并提到了SOF和ELF文件合并生成JIC文件的高效固件写入方式。

2481

2481

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?