功能描述

- 包含两个sub-channel, 总共24 DQ信号,两对WCK 差分信号,两对RDQS差分信号

- 每个sub-channel bank架构是4BANK 4BG

- WCK:CK比值固定为2:1

- CA pins用于传输命令,地址,bank,配置,训练信息给SDRAM,CA是CK双沿采样,CS是单沿采样

- 高速IO设计操作在0.5V VDDQ电压,Voh是0.5*VDDQ

- 低速模式IO操作在0.3V~0.5V VDDQ电压(unterminated).

- 数据访问大小取决于burst length,支持12n和24n 预取;

- 对于12-DQ sub-channel 的BL24读写,包含288bit传输,其中256bit 数据,32bit非数据,传输时间是12个WCK周期。

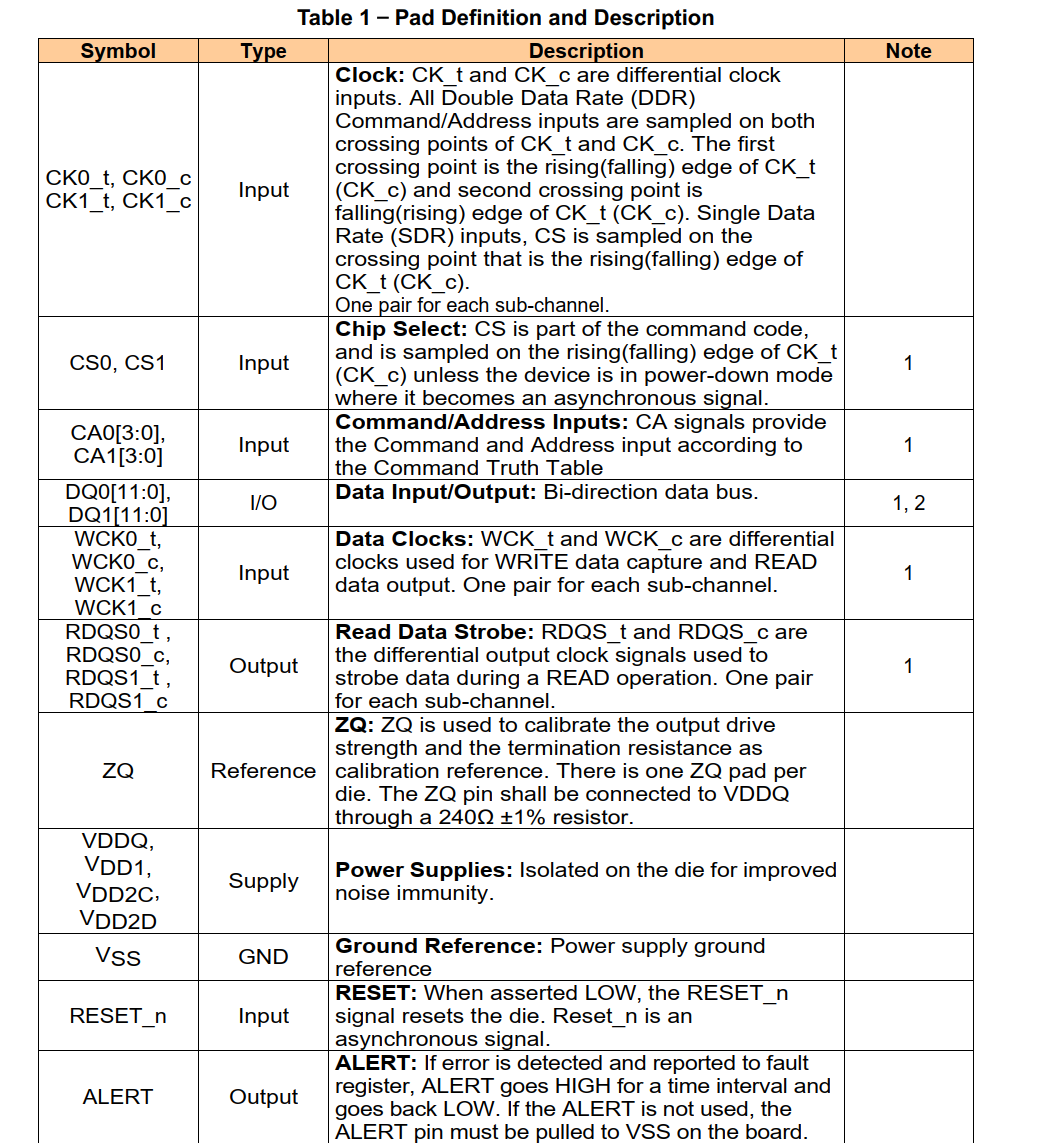

Pad definition

信号

CK_t/CK_c: 差分时钟,每个sub-channel有一对;CA是CK双沿采样,第一个采样是CK_t上升沿,第二个采样是CK_t下降沿;

CS:片选信号,每个sub-channel有独立的CS信号,CS是CK单沿采样,只在CK_t上升沿采样

CA[3:0]:命令、地址信号,每个sub-channel有独立的CA信号;命令的含义参考真值表

DQ[11:0]: 数据输入/输出信号,每个sub-channel有独立的DQ bus。

WCK_t/WCK_c: 数据差分时钟输入信号,每个sub-channel有一对,用于写数据采样和读数据输出

RDQS_t/RDQS_c: 输出读数据strobe信号,每个sub-channel有一对,,差分时钟用于strobe读数据

ZQ: ZQ pin用于校准电阻阻值和输出驱动强度,ZQ pin需要通过一个240欧姆的电阻连接到VDDQ上

VDDQ,VDD1,VDD2C,VDD2D: 电源信号

VSS: 电源地

RESET_n: 输入复位信号,低有效

ALERT: 输出信号,检测到错误报告给错误寄存器,高有效,会自动清除,不用需要接地

解析

相对LPDDR5的变化:

LPDDR6没有DMI信号

CA位宽变化:从7bit变为4bit * 2

DQ位宽变化: 从16bit/8bit 变为12bit * 2

架构变为sub-channel, CK,CS,CA,DQ,WCK,RDQS都是sub-channel独立的信号

LPDDR6新增ALERT信号,VDD2C,VDD2D电源信号

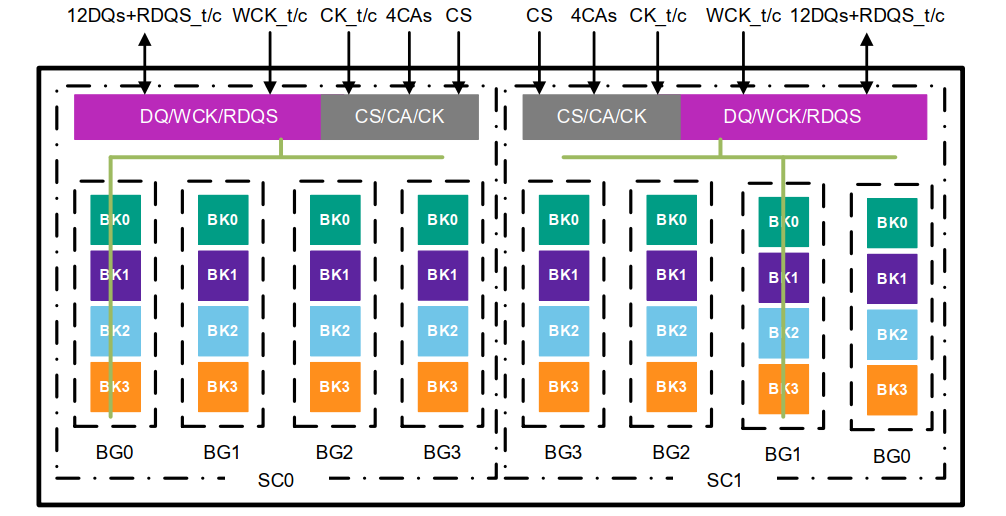

结构图

第一种是普通模式,包含两个sub-channel, 每个sub-channel 包含4个BG x 4个bank, 信号是12DQ, 1对RDQS, 1对WCK,1对CK,4个CA,1个CS共23根信号

X24模式 配置(MR0 OP[2]=0,MR1 OP[6]=0 )

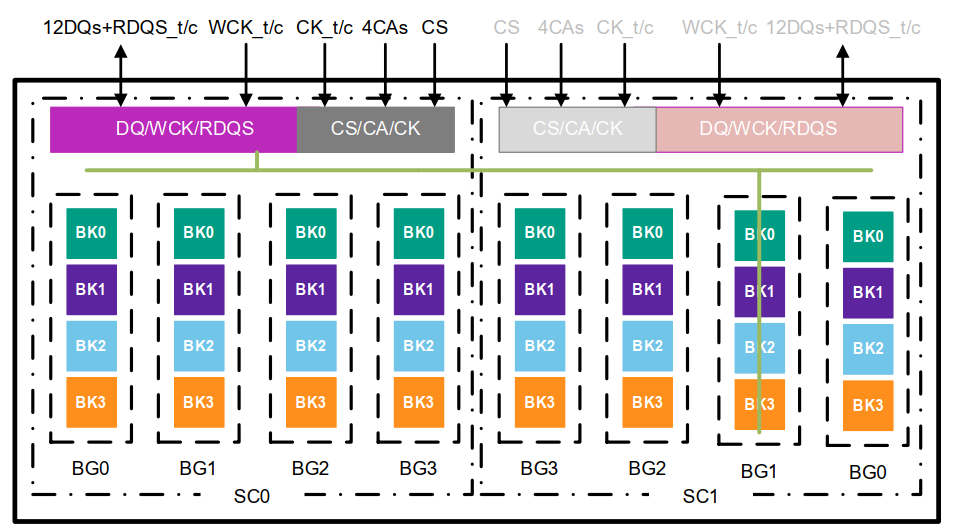

第二种是动态efficiency mode,此时只使用一组IO(12DQ, 1对RDQS, 1对WCK,1对CK,4个CA,1个CS),可以通过SC0 IO访问两个sub-channel。

X12模式配置(MR0 OP[2]=0,MR1 OP[6]=1 )

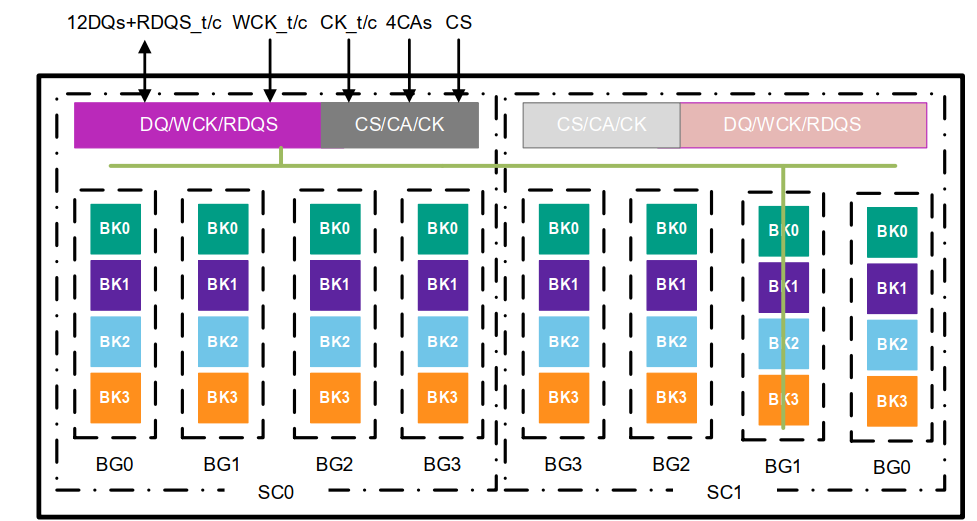

第三种是静态efficiency mode此时只有一组IO(12DQ, 1对RDQS, 1对WCK,1对CK,4个CA,1个CS),可以通过SC0 IO访问两个sub-channel。

静态efficiency mode和动态efficiency mode的区别是静态只有一个SC的IO信号,动态有两个SC的IO信号,只使用其中一个。

X12模式配置(MR0 OP[2]=1,MR1 OP[6]=0/1)

492

492

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?