可私信获取整个项目文件

8bit 即有8位二进制

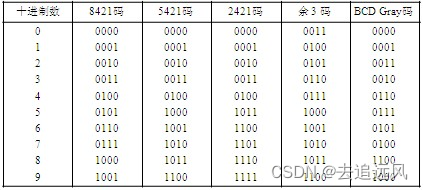

BCD码 ,全称Binary-Coded Decimal,简称BCD码或者二-十进制代码

利用四位二进制(0000-1111)16个中选择10个作为十进制0-9;

常见的BCD码是8421码

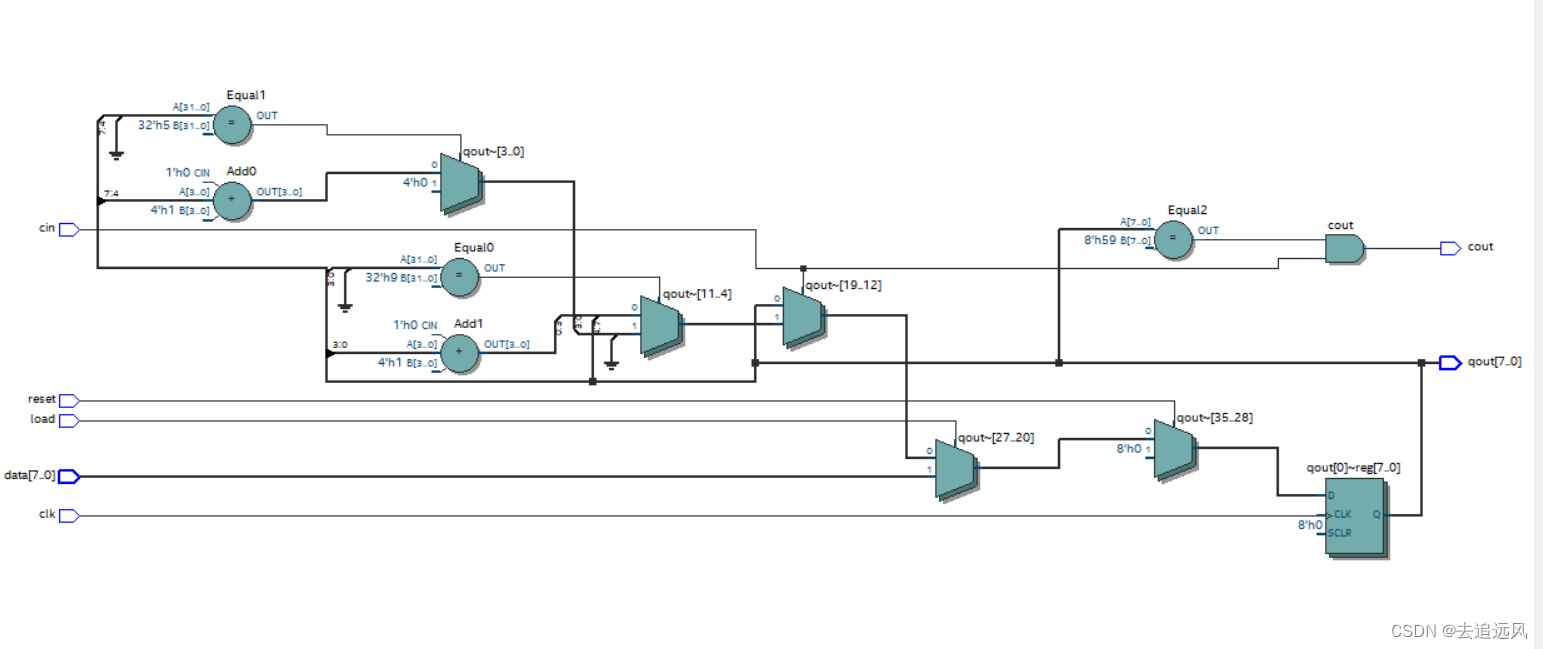

本项目使用两组BCD码(每组4bit,共8bit,故称为8bitBCD)(高位0-5,低位0-9)组成0-59计数器

闲话不多,上代码

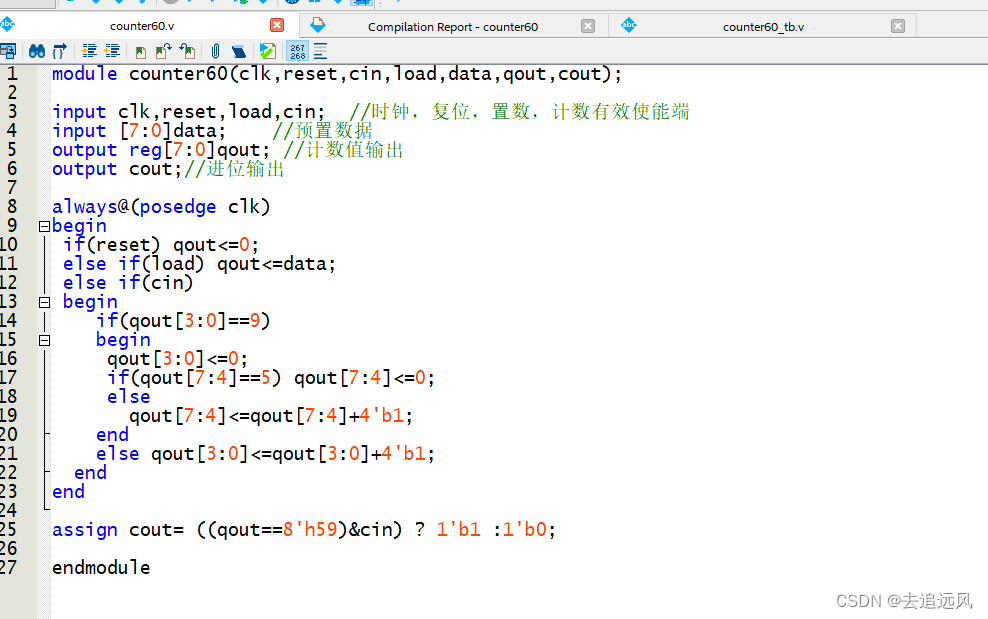

计数值qout达到60时,cout进位输出,

data是预知术,cin是累加计数使能端

module counter60(clk,reset,cin,load,data,qout,cout);

input clk,reset,load,cin; //时钟,复位,置数,计数有效使能端

input [7:0]data; //预置数据

output reg[7:0]qout; //计数值输出

output cout;//进位输出

always@(posedge clk)

begin

if(reset) qout<=0;

else if(load) qout<=data;

else if(cin)

begin

if(qout[3:0]==9)

begin

qout[3:0]<=0;

if(qout[7:4]==5) qout[7:4]<=0;

else

qout[7:4]<=qout[7:4]+4'b1;

end

else qout[3:0]<=qout[3:0]+4'b1;

end

end

assign cout= ((qout==8'h59)&cin) ? 1'b1 :1'b0;

endmodule`timescale 10ns/1ns

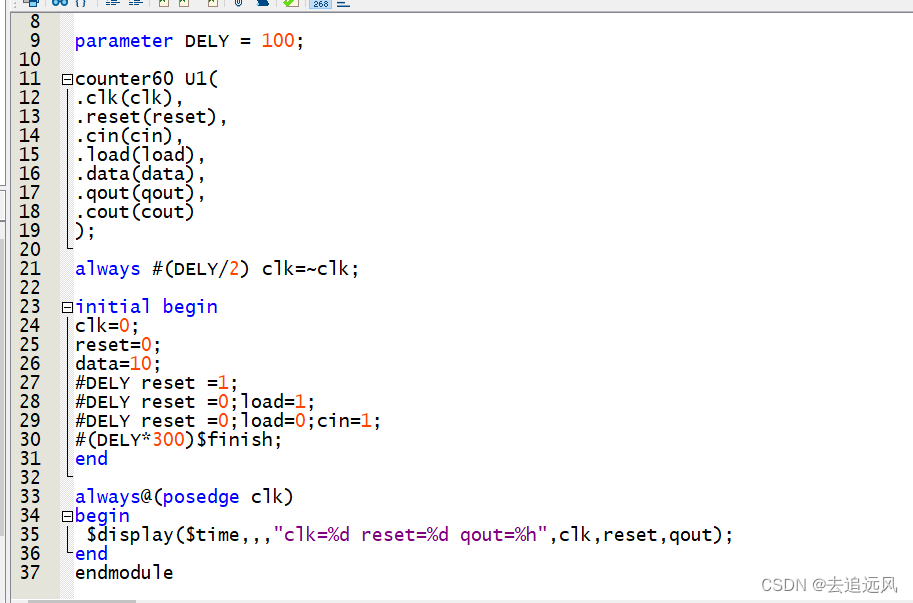

module counter60_tb;

reg clk,reset,load,cin; //时钟,复位,置数,计数有效使能端

reg [7:0]data; //预置数据

wire[7:0]qout; //计数值输出

wire cout;//进位输出

parameter DELY = 100;

counter60 U1(

.clk(clk),

.reset(reset),

.cin(cin),

.load(load),

.data(data),

.qout(qout),

.cout(cout)

);

always #(DELY/2) clk=~clk;

initial begin

clk=0;

reset=0;

data=10;

#DELY reset =1;

#DELY reset =0;load=1;

#DELY reset =0;load=0;cin=1;

#(DELY*300)$finish;

end

always@(posedge clk)

begin

$display($time,,,"clk=%d reset=%d qout=%h",clk,reset,qout);

end

endmodule

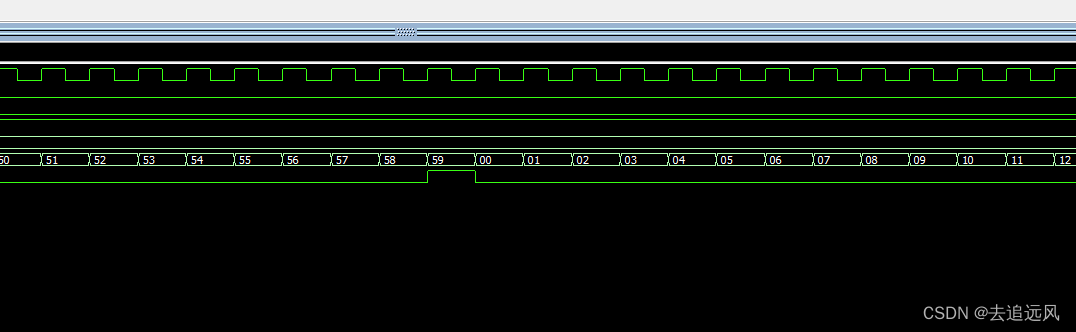

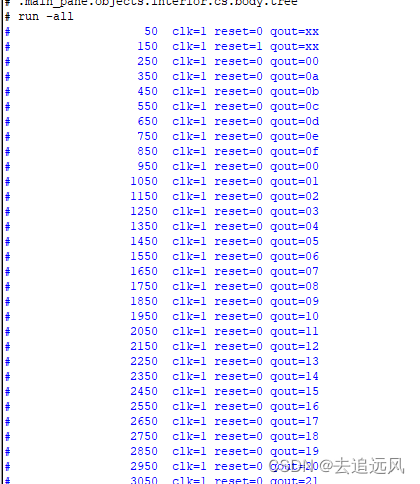

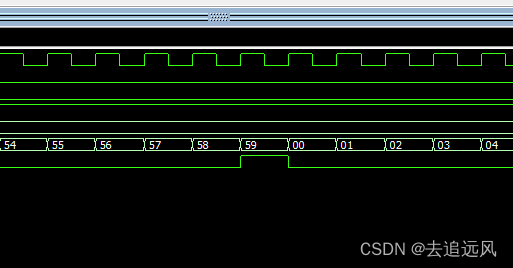

modsim端:

可私信获取整个项目文件

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?