一、存储器定义

存储器是计算机系统中的记忆设备,用来存放程序和数据。

二、存储器的分类

构成存储器的存储介质,目前主要采用半导体器件和磁性材料。

①按存储介质分:半导体存储器、磁表面存储器;

②按存取方式分类:随机存储器(半导体存储器)、顺序存储器(磁带存储器)、半顺序存储器(磁盘存储器);

③按存取内容分类:只读存储器(ROM)、随机读写存储器(RAM);

④按断电后的信息状态分类:易失性存储器(磁性介质)、非易失性存储器(半岛体介质);

⑤按信息存储的机理分类:静态读写存储器(SRAM)、动态读写存储器(DRAM);

⑥按在计算机系统中所起的作用分类:内部存储器、外部存储器;又可分为主存储器、高速缓冲存储器、辅助存储器、控制存储器。

两级存储系统:内存储器、外存储器;

三级存储系统:cache、主存、外存储器;(就是将内存储器分为cache和主存)

内存储器:正在执行的程序的指令和数据存储在CPU能直接访问的存储器中,这种狭义的存储器 就是内存储器。(速度高、容量小、价格高)

外存储器:为了扩大存储容量,在内存储器之外增加容量更大但访问速度稍慢的外存储器。 (速度低、容量大、价格低)

cache:用于提升访问速度,以便使存取速度和CPU的运算速度相匹配;

外存储器:主要解决存储容量问题,以满足计算机的大容量存储要求;

主存储器:介于cache与外存之间,要求选取适当的存储容量和存储周期,使它能容纳系统的核心 软件和较多的用户程序。

要解决对存储器要求容量大、速度快、成本低三者之间的矛盾:

多级存储系统的出发点是提高存储系统的性能/价格比,让整个存储系统在速度上接近cache,而在容量和价格上接近外存。

四、内存储器的性能指标

主要是存储容量和存储速度,后者通常可以用存取时间、存储周期和存储器带宽描述。

存储容量:指一个存储器中可存储的信息比特数,常用比特数(bit)/字节数(B)来表示。 (1B=8bit);

也可使用KB、MB、GB、TB等单位。(1KB=210B、1MB=220B、1GB=230B);

n位地址—>个存储单元,

存储容量=存储字数(存储单元数)×存储字长(每单元的比特数);

1Mbit=1M×1bit=128K×8bit=512K×4bit

五、SRAM

特点:存取速度快,但存储密度和容量不如DRAM大,价格贵,易失性存储器。

任何一个SRAM,都有三组信号线与外部打交道:

①地址线:n条,指定了存储器的容量是个存储单元;

②数据线:说明存储器的字长是n位;

③控制线:指定了对存储器的访问。

六、DRAM

特点:存取速度慢(与SRAM相比),存储容量大,相对价格比较低。

SRAM的存储元是一个触发器,它具有两个相对稳定的状态,DRAM简化了每个存储元的结构,因而DRAM的存储密度很高,通常用作计算机的主存储器。

七、cache存储器

1.cache的功能:

cache是一种高速缓冲存储器,是为了解决CPU和主存之间速度不匹配而采用的一项重要技术。

其原理基于程序运行中具有的空间局部性和时间局部性特征。

cache是介于CPU和主存之间的小容量存储器。

存取速度比主存快(5-10倍),容量远小于主存。

cache能高速地向CPU提供指令和数据,从而加快了程序的执行速度。

从功能上看,它是主存的缓冲存储器,由高速的SRAM组成。

为追求高速,包括管理在内的全部功能由硬件实现,因而对程序员是透明的。

2.cache的基本原理:

cache除包含SRAM外,还要有控制逻辑。

若cache在CPU芯片外,它的控制逻辑一般与主存控制逻辑合成在一起,称为主存/cache控制器;

若cache在CPU内,则由CPU提供它的控制逻辑。

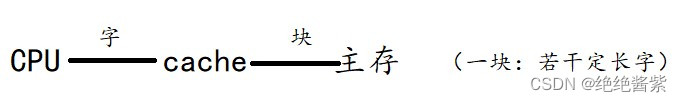

CPU与cache之间的数据交换是以字为单位;

cache与主存之间的数据交换是以块为单位。

(一个块由若干字组成,是定长的。)

注:字是CPU每次访问存储器时可存取的最小单位。

当CPU读取内存中的一个字时,便发出此字的内存地址到cache和主存。

此时cache控制逻辑依据地址判断此字当前是否在cache中:

①是:cache命中,此字立即传送给CPU;

②否:cache缺失(未命中),用主存读周期把此字从主存读出送到CPU,与此同时,把含有这个字的整个数据块从主存读出送到cache中。

3.cache的命中率:

(cache的命中率应接近于1。由于程序访问的局部性,实现这个目标是可能的。)

在一个程序执行期间,设Nc 表示cache完成存取的总次数,Nm表示主存完成存取的总次数,h定义为命中率,则有

若tc表示命中时的cache访问时间,tm表示未命中时的主存访问时间,1-h表示为命中率(缺失率),则cache/主存系统的平均访问时间ta为

我们追求的目标是,以较小的硬件代价使cache/主存系统的平均访问数据ta越接近tc越好。设r=tm/tc表示主存与cache的访问时间之比,e表示访问效率,则有

由上式可看出,为提高访问效率,命中率h越接近1越好.r值以5-10为宜,不宜太大。

4.cache结构设计必须解决的问题:

(cache设计原则:cache的命中率尽可能高、cache对CPU而言是透明的)

①主存的内容调入cache时如何存放?

②访存时如何找到cache中的信息?

③当cache空间不足时如何替换cache中已有的内容?

④需要写操作时如何改写cache的内容?

八、主存与cache的地址映射

①全相联映射方式 空位随意放

优点:灵活;

缺点:高速比较器电路难于设计和实现。

②直接映射方式 对号入座放

优点:硬件简单,成本低,地址变换速度快;

缺点:每个主存块只有一个固定的行位置可存放。

③组相联映射方式 按号分组,组内随意放

全相联映射和直接映射楼主方式的优缺点正好相反。 从存放位置的灵活性和命中率来看,前者为优; 从比较器电路简单及硬件投资来说,后者为佳。

而组相联映射方式是前两种方式的折中方案,它适度的兼顾了二者的优点又尽量避免二者的缺点,因此被普遍采用。

九、cache的写操作策略

1.写回法

①当CPU写cache命中时,只修改cache的内容,而不立即写入主存;只有当此行被换出时才写回主存; ②当CPU写cache未命中时,将包含此字的主存块拷贝到cache中再进行修改。 特点:减少了写入主存的次数,真正实现CPU与主存之间的高速缓冲作用,但这种方式会存在不一致性的隐患。

2.全写法

①当写cache命中时,cache与主存同时发生写修改,因此较好地维护了cache与主存内容的一致性; ②当写cache未命中时,只能直接向主存进行写入,但此时是否将修改过的主存块取到cache,有两种方法: a.WTWA法 取主存块到cache并为它分配一个行位置 b.WTNWA法 不取主存块到cache 特点:保证了写cache与写主存的同步进行,但cache对CPU向主存的写操作无高速缓冲功能。

3.写一次法

是基于写回法并结合全写法的写策略:写命中与写未命中的处理方法与写回法基本相同,只是第一次写命中时要同时写入主存。

十、cache的替换策略

①最不经常使用(LFU)算法 LFU算法认为应将一段时间内被访问次数最大号的那行数据换出,其缺点是不能严格反映近期访问情况。

②近期最少使用(LRU)算法 LRU算法将近期内长久为访问的行换出。这种算法保护了刚拷贝到cache中的新数据行,因而使cache有较高的命中率。

③随即替换 随即替换策略只要从特定的行位置中随机地选取一行换出即可,但其容易降低命中率和cache工作效率。

430

430

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?