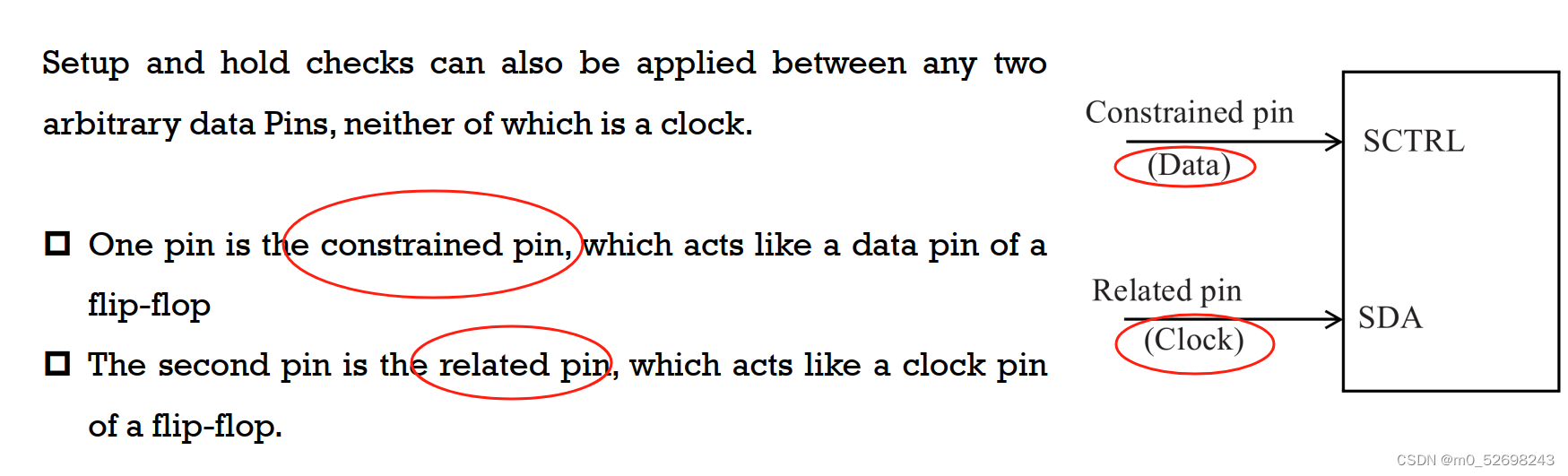

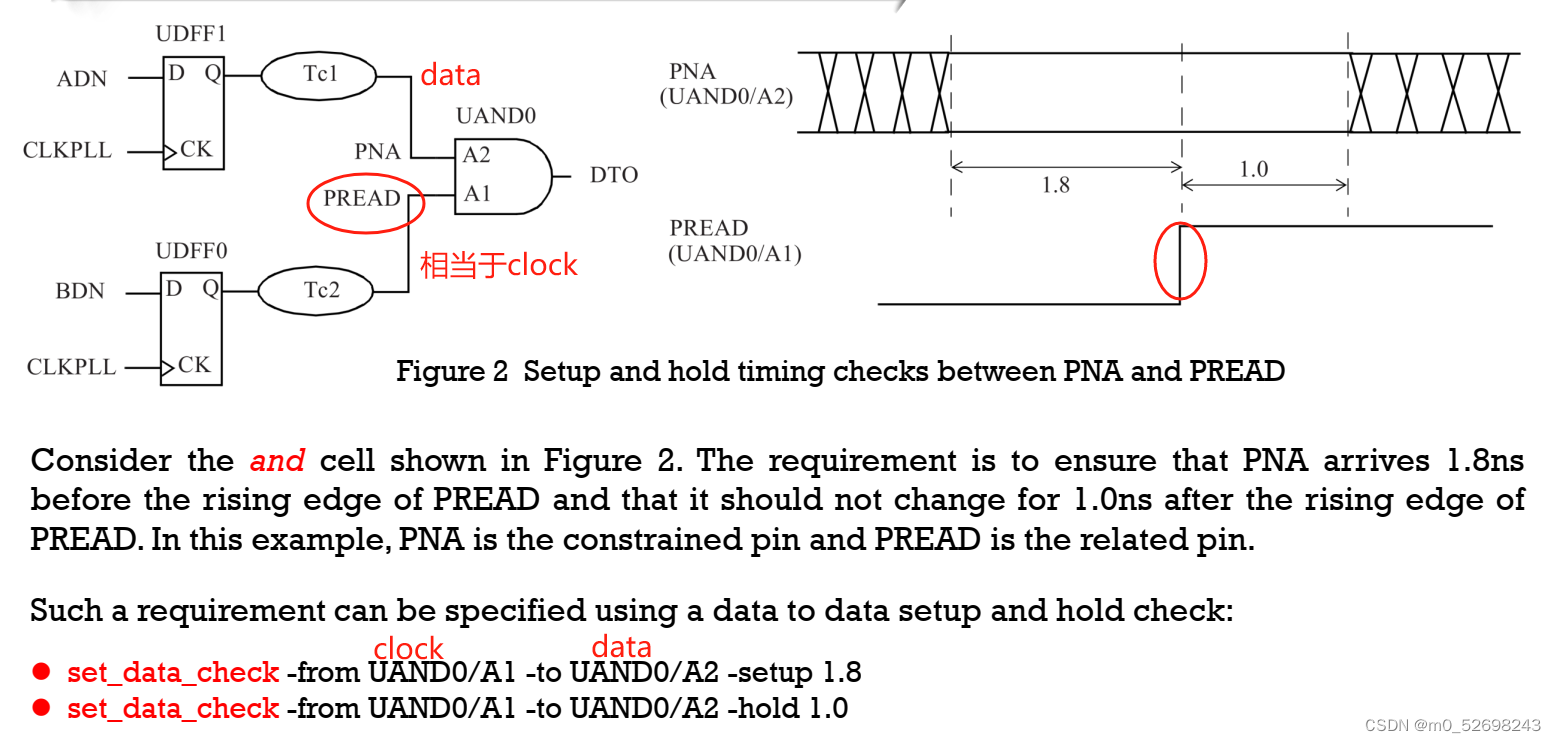

Setup check和Hold check也可以应用于任意两个数据引脚之间,检查它们之间的时序关系,但是这两个引脚之间没有clock。

1.Setup Check

例子:

1.The setup data check implies that SCTRL should arrive at least 2.1ns prior to the edge of the related pin SDA. Otherwise it is a data to data setup check violation。

2.The hold data check specifies that SCTRL should arrive at least 1.5ns after SDA. If the constrained signal arrives earlier than this specification, then it is a data to data hold check violation。

data to data clock :对于setup check 来说 launch edge 和 capture edge是一样的。

零周期setup check导致hold check与其他hold check报告不同-hold check不再位于同一时钟边缘.

2 hold check

1.不同边沿

在zero_cycle setup check引起的hold check时,capture edge 是在 launch edge 的前一个周期开始的。

2.同一边沿

在某些情况下,设计人员可能要求在同一时钟周期内执行数据到数据hold check。

hold check 时序报告

另一种方法(相同边沿)

另一种方法(相同边沿)

320

320

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?