一.时钟声明

1.主时钟定义

该引脚的约束命令如下:

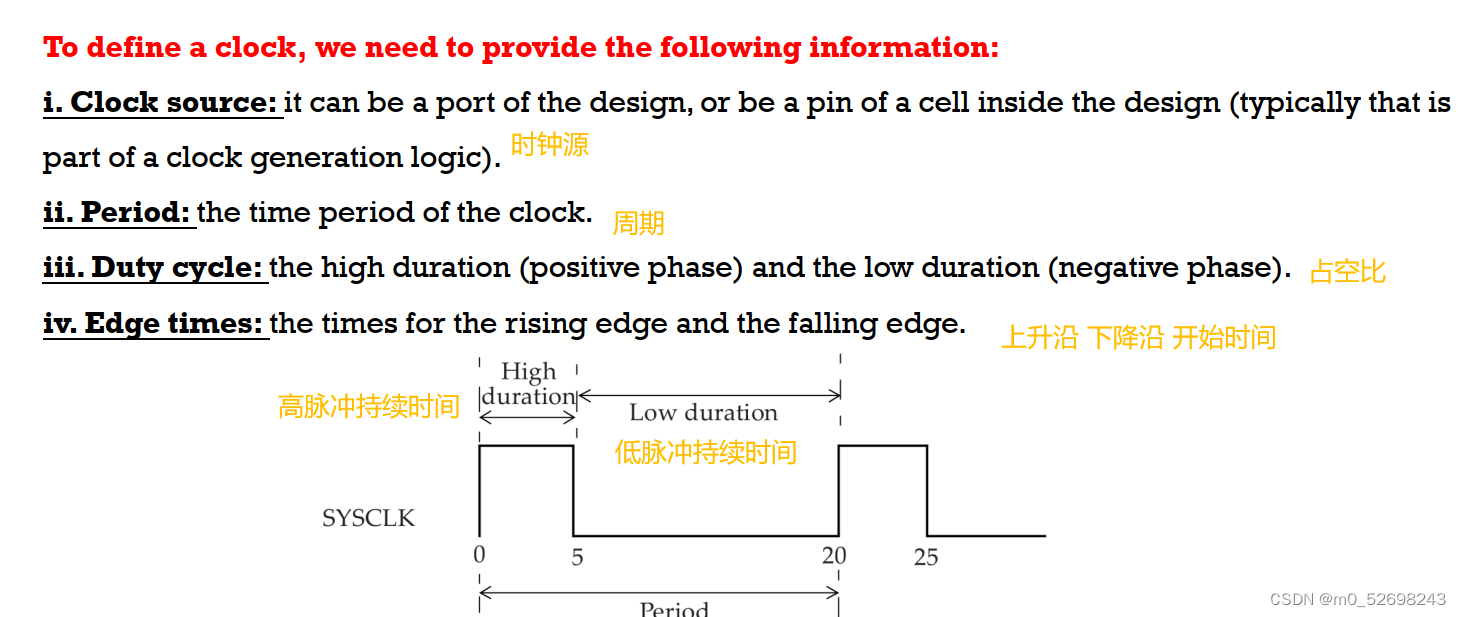

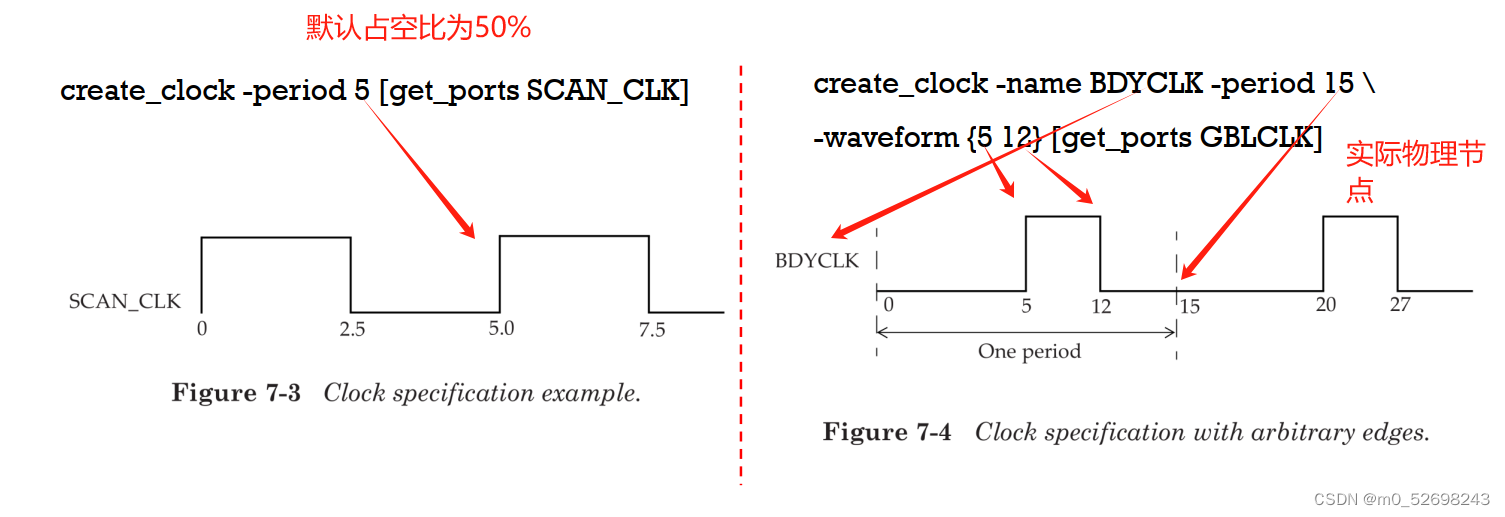

create_clock -name SYSCLK -period 20 -waveform {0 5} [get_ports SCLK]

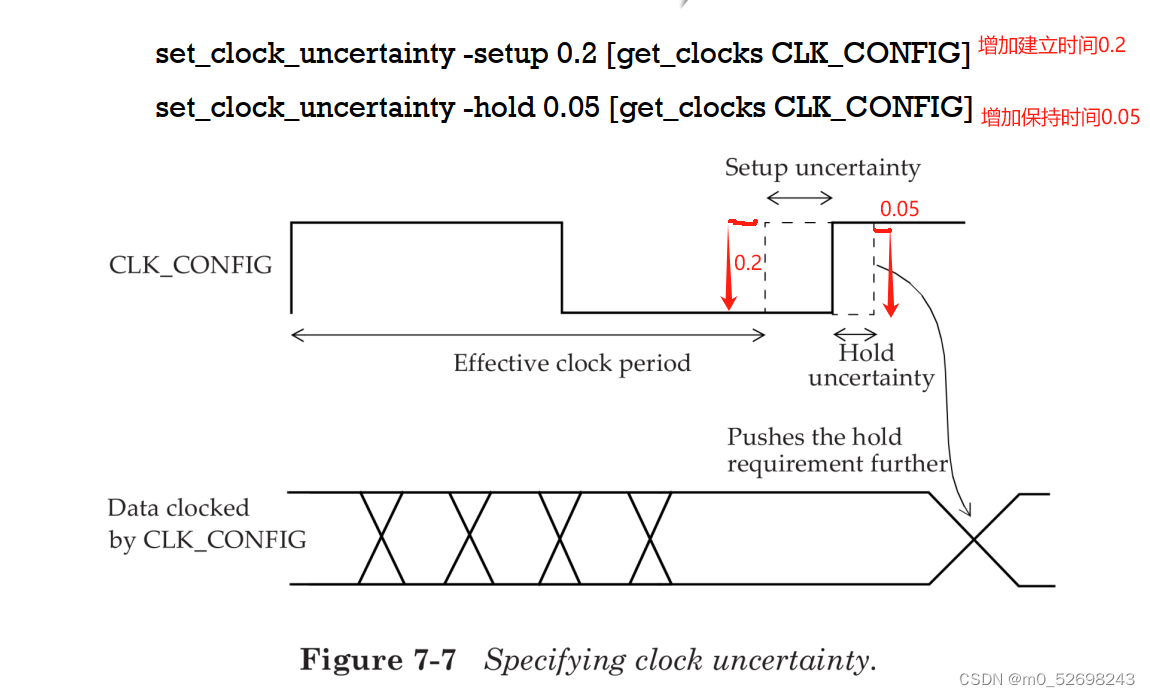

2.时钟不确定性

建立时钟不确定性声明,会使整个电路的时序变得更加严苛,满足设计的稳健性,增加时序余量。

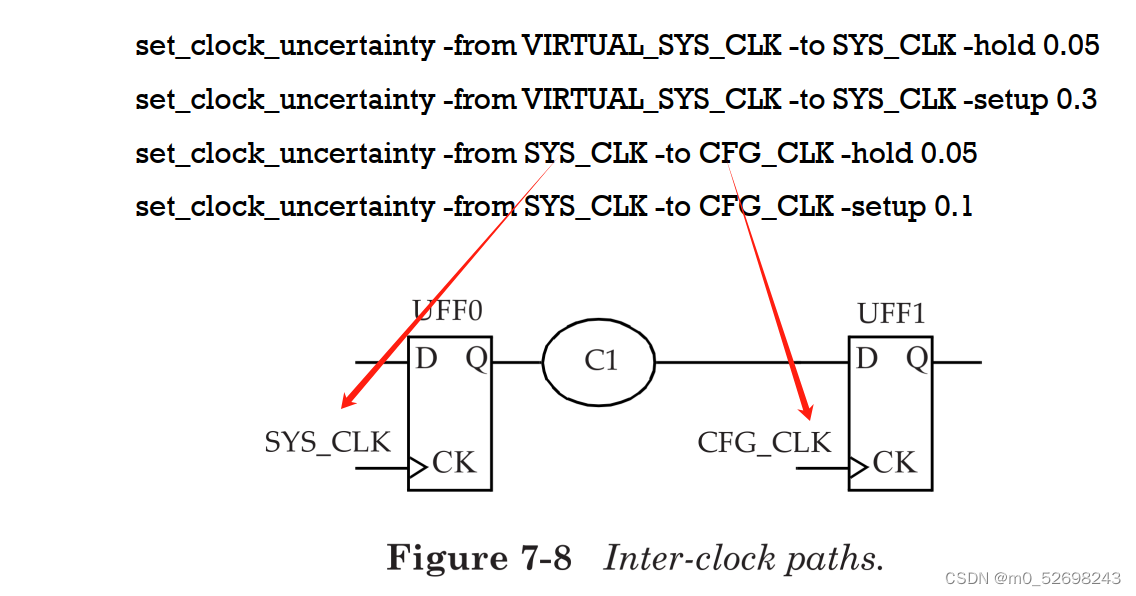

指定路径的不确定性,或者虚拟时钟的不确定性

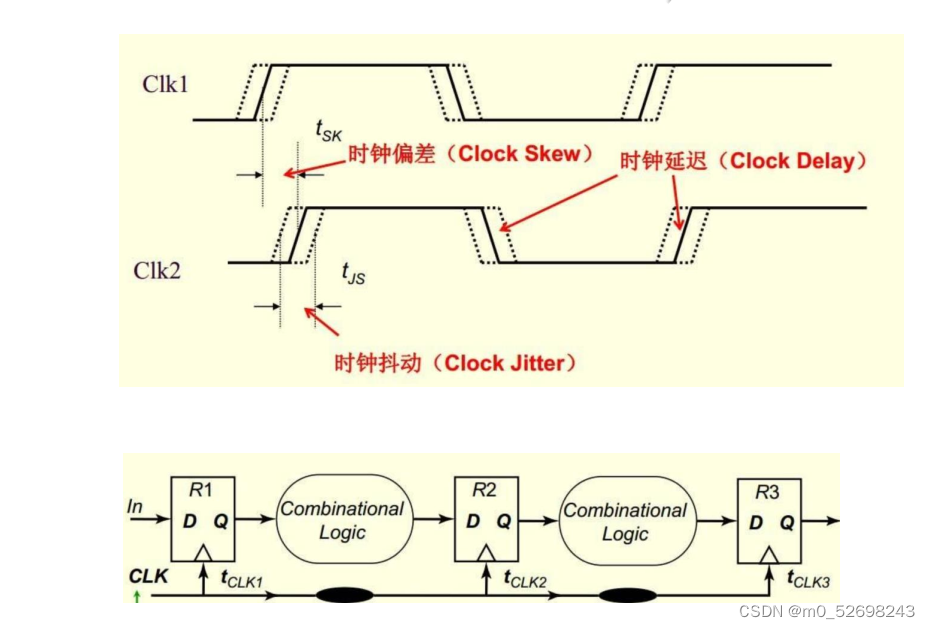

时钟不确定性的主要来由:

时钟偏差:时钟源到达不同触发器的时间偏差;

时钟抖动:时钟边沿的超前或滞后;

时钟延迟:网络延迟和源延迟

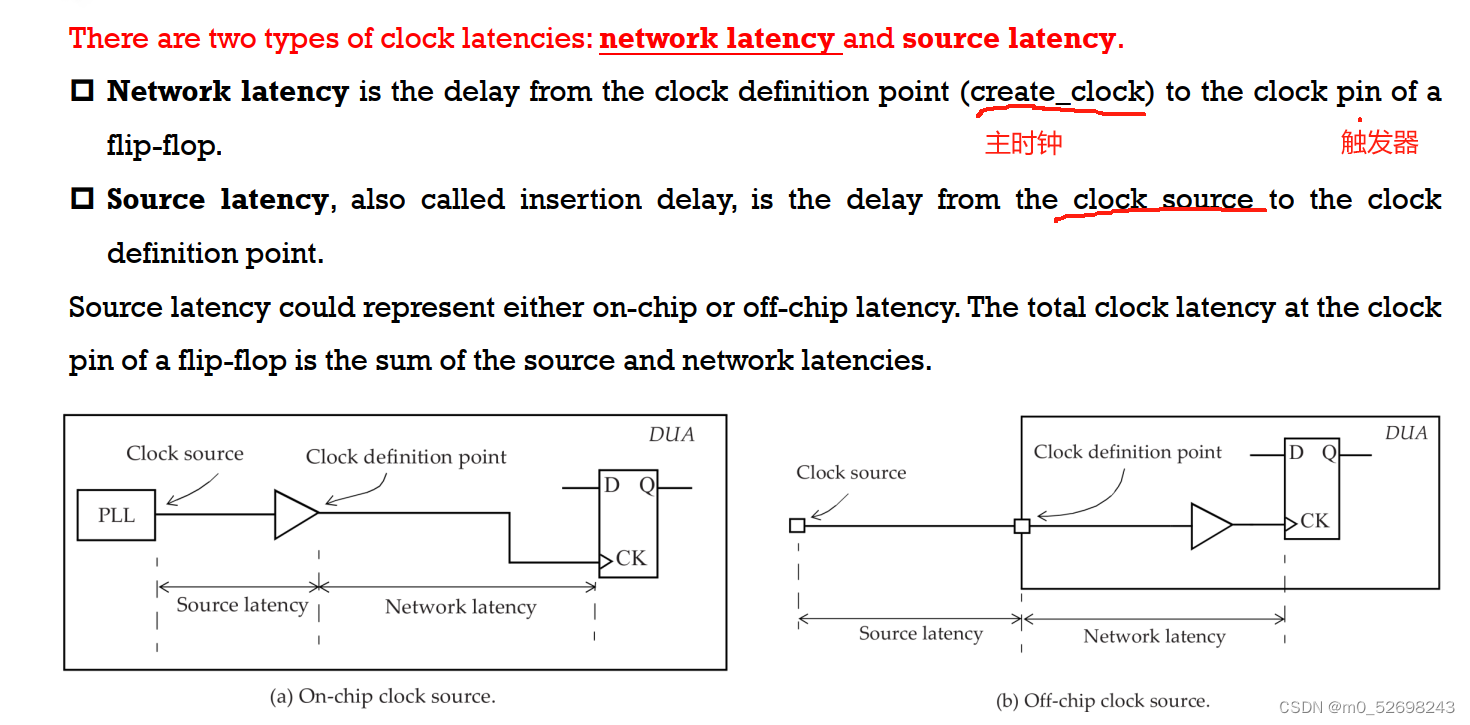

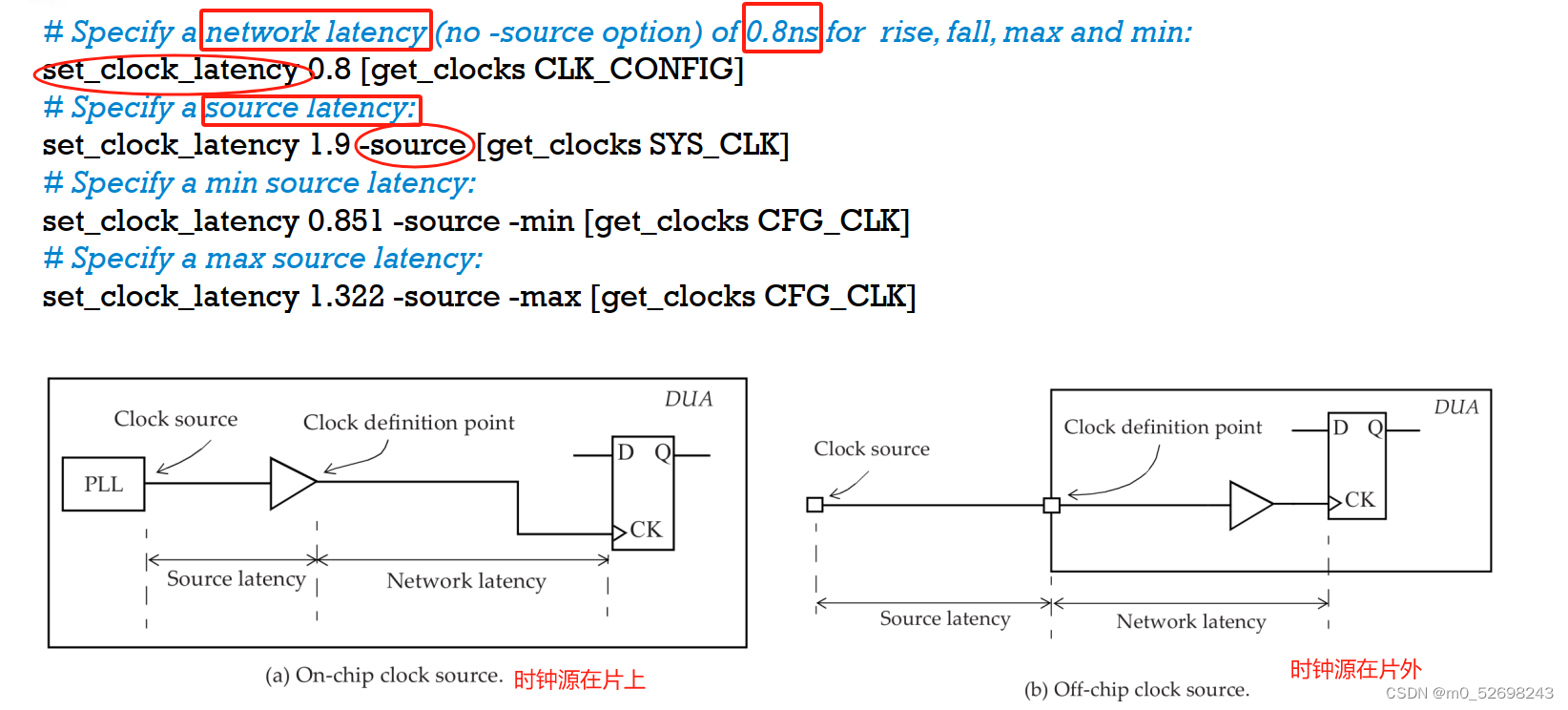

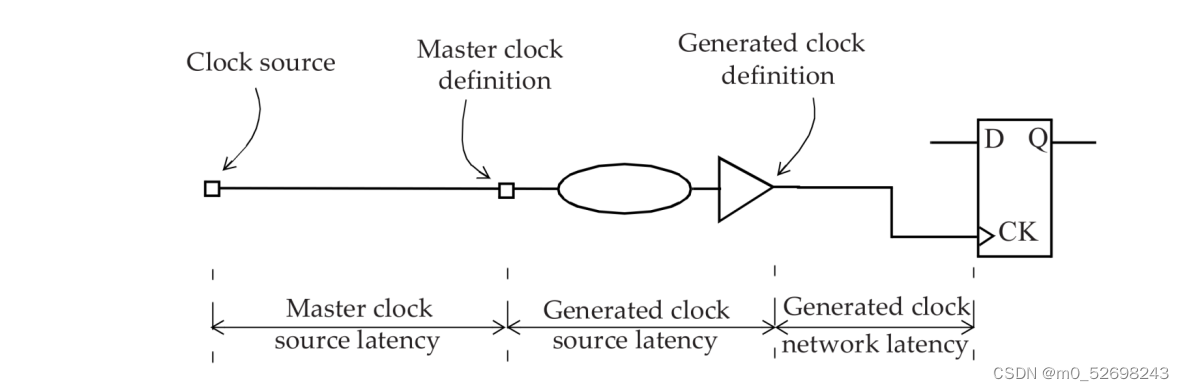

时钟延迟包含:网络延迟和源延迟。

网络延迟:时钟定义点到触发器时钟引脚的延迟。

源延迟:时钟源到时钟定义点的延迟。

需要注意的源延迟和网络延迟之间的一个重要区别是,一旦为设计构建了时钟树,就可以忽略网络延迟(假设指定了set_propagated_clock命令)。但是,即使在构建时钟树之后,源延迟仍然存在。网络延迟是在时钟树合成之前对时钟树延迟的估计。在时钟树合成之后,从时钟源到触发器的时钟引脚的总时钟延迟是源延迟加上时钟树从时钟定义点到触发器的实际延迟。

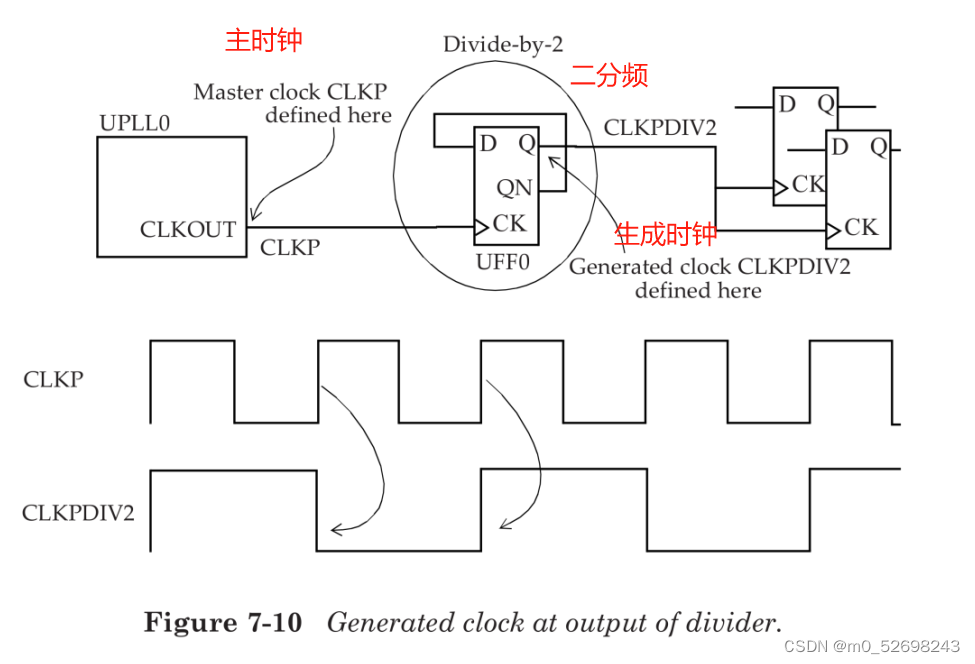

3.生成时钟(Generated Clocks)

生成时钟是从主时钟派生出来的时钟。主时钟是使用create_clock规范定义的时钟。

create_clock -name CLKP 10 [get_pins UPLL0/CLKOUT]

# 创建主时钟,周期10ns。引脚在CLKOUT

create_generated_clock -name CLKPDIV2 -source UPLL0/CLKOUT -divide_by 2 [get_pins UFF0/Q]

# 创建二分频逻辑输出的生成时钟【注意】:

生成时钟也可以声明为主时钟,而每个主时钟都代表一个时钟域。一般来说,实际电路中的生成时钟就应该声明为生成时钟,因为主时钟和生成时钟认为是同相位的。而如果将原本实际的生成时钟声明为主时钟,那么就会产生两个时钟域。影响静态时序分析。

4.时钟延迟

也可以为生成时钟指定时钟延迟。在生成时钟上指定的源延迟指定从主时钟定义到生成时钟定义的延迟。

如果时钟操作输出的时钟和源时钟没有太多关系(不是直接的倍频分频等),失去了相位和周期的继承性,那么此时输出的时钟就是可以定义为主时钟,而非生成时钟:

create_clock -name SYS_CLK -period 4 -waveform {0 2} [get_pins UFFSYS/Q]

create_clock -name CORE_CLK -period 12 -waveform {0 4} [get_pins UFFCORE/Q]

create_clock -name MAIN_CLK -period 12 -waveform {0 2} [get_pins UAND2/Z]

# 与单元输出的地方,建立主时钟,而非生成时钟。二 输入输出路径

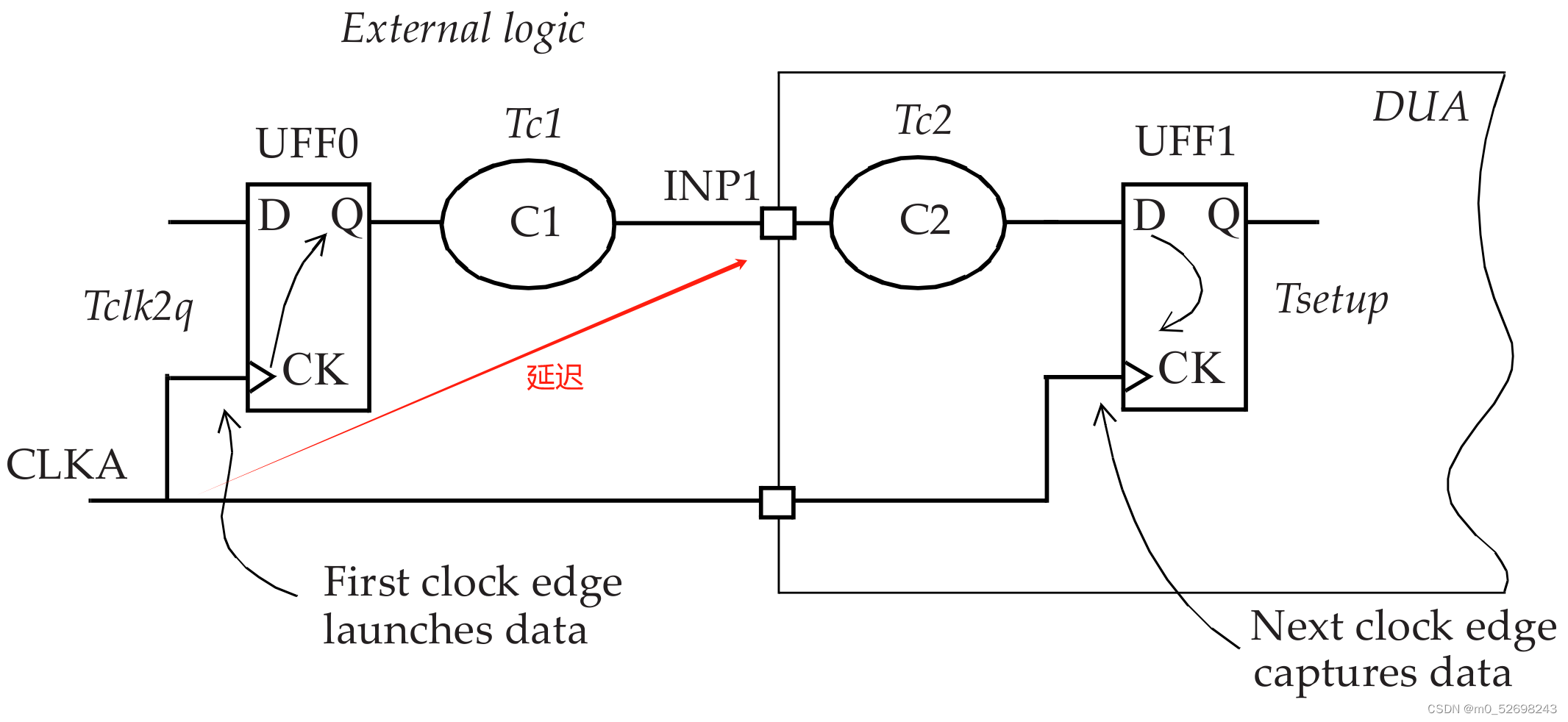

1.输入延迟

set Tclk2q 0.9

set Tc1 0.6

set_input_delay -clock CLKA -max [expr Tclk2q + Tc1] [get_ports INP1]

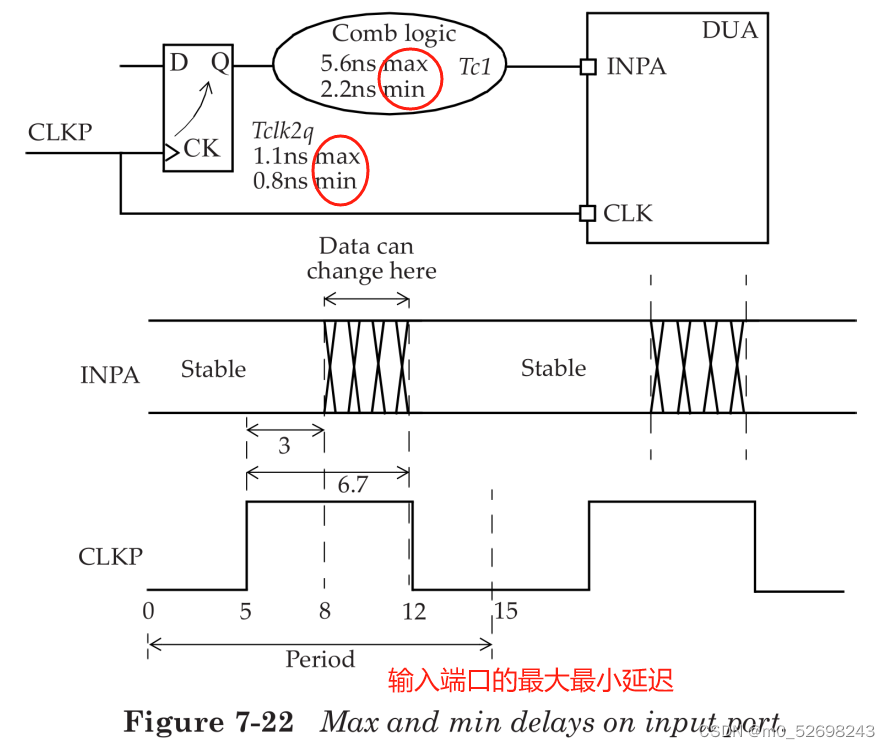

create_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]2.输出延迟

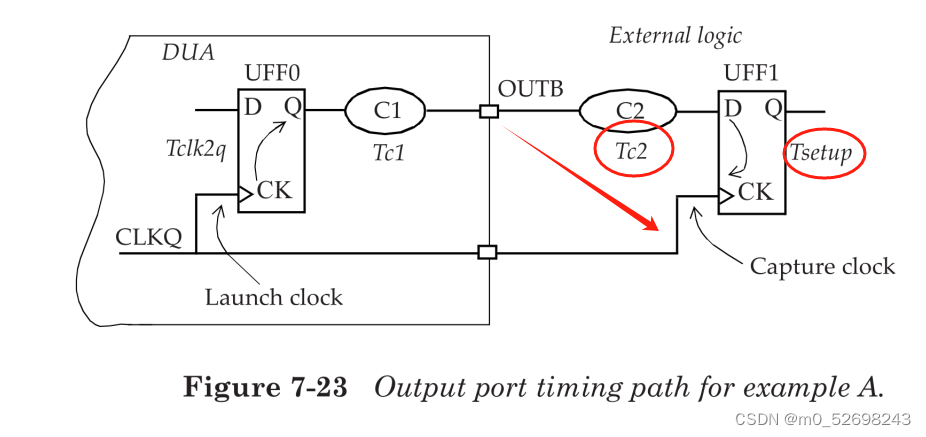

set Tc2 3.9

set Tsetup 1.1

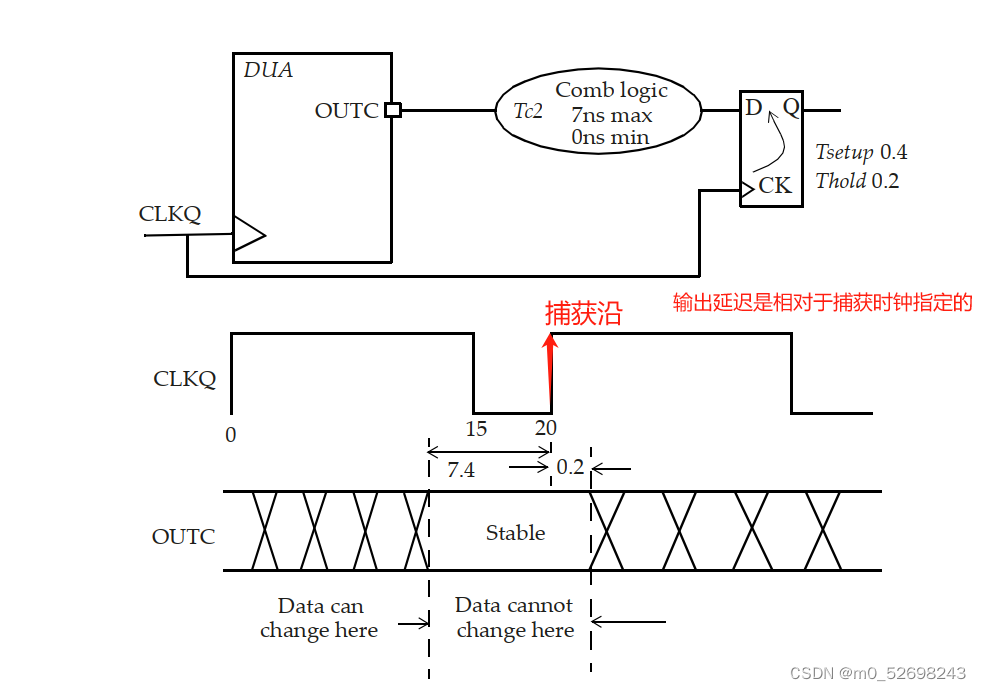

set_output_delay -clock CLKQ -max [expr Tc2 + Tsetup] [get_ports OUTB]最大路径延迟为7.4ns (= max Tc2 + Tsetup = 7 + 0.4)。

最小路径延迟为-0.2ns (= min Tc2减去hold = 0 -0.2)。

波形显示了OUTC必须稳定,以便外部触发器可靠地捕获。这说明在所需的稳定区域开始之前,数据必须在输出端口准备好,并且必须在稳定区域结束之前保持稳定。

create_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]同时存在输入和输出延迟声明:

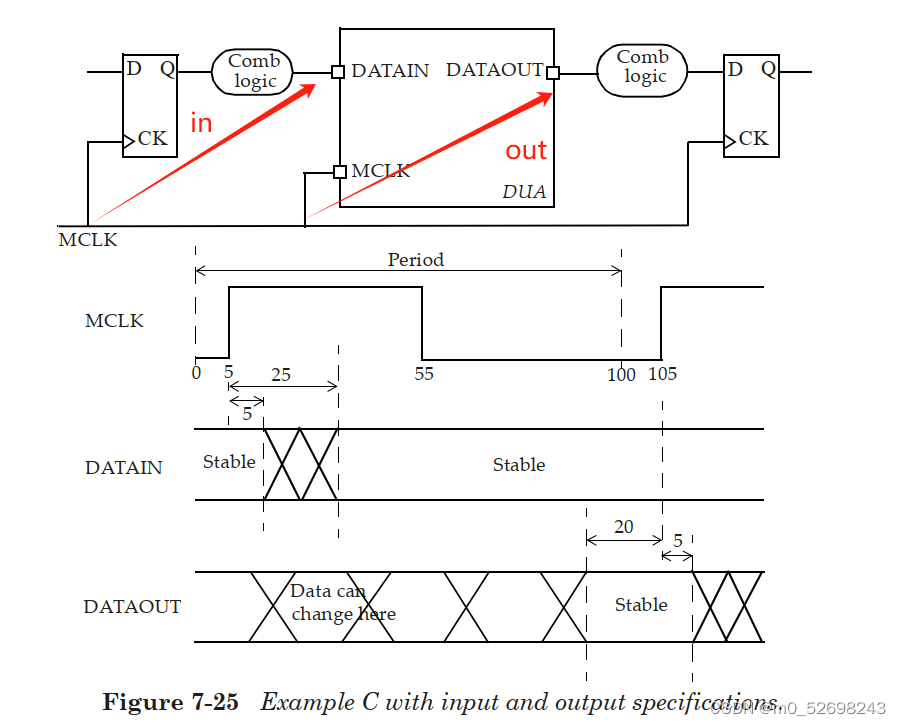

create_clock -period 100 -waveform {5 55} [get_ports MCLK]

set_input_delay 25 -max -clock MCLK [get_ports DATAIN]

set_input_delay 5 -min -clock MCLK [get_ports DATAIN]

set_output_delay 20 -max -clock MCLK [get_ports DATAOUT]

set_output_delay -5 -min -clock MCLK [get_ports DATAOUT]三 外部属性建模

1、输入

• set_drive

• set_driving_cell

• set_input_transition

第一种已经过时,不推荐。

第一种用来给输入端口设定驱动阻抗值;

第二种功能同第一种,用法更精准更方便;

第三种更为直接,直接指定输入端口的转换时间;

2、输出

• set_load 用来给容性负载建模。

四 设计规则检查(DRC)

最常用的两个命令:

• set_max_transition

• set_max_capacitance

主要用来检查设计中的所有端口和引脚都满足转换时间和电容的要求。

set_max_transition 0.6 IOBANK

# Sets a limit of 600ps on IOBANK.

set_max_capacitance 0.5 [current_design]

# Max capacitance is set to 0.5pf on all nets in current design.

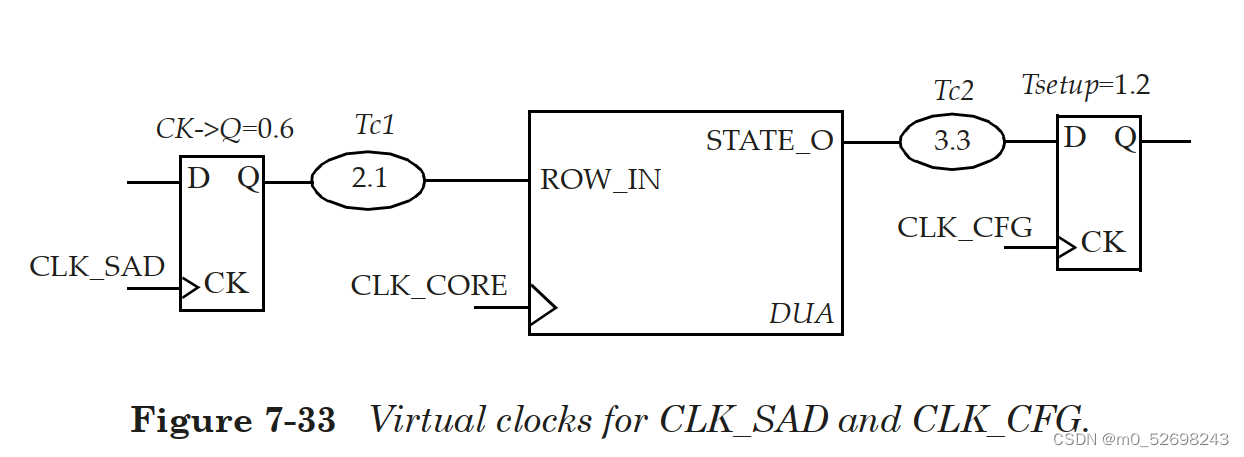

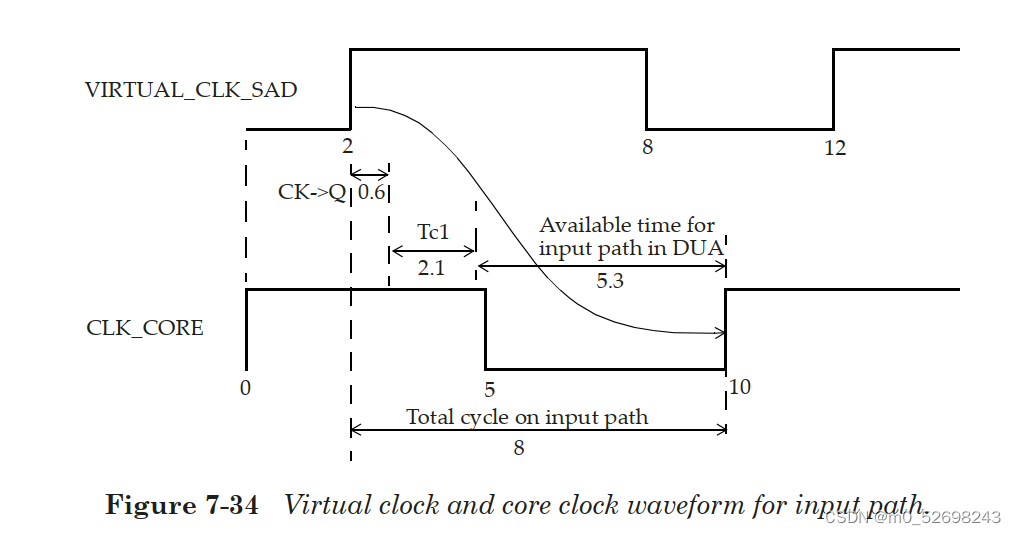

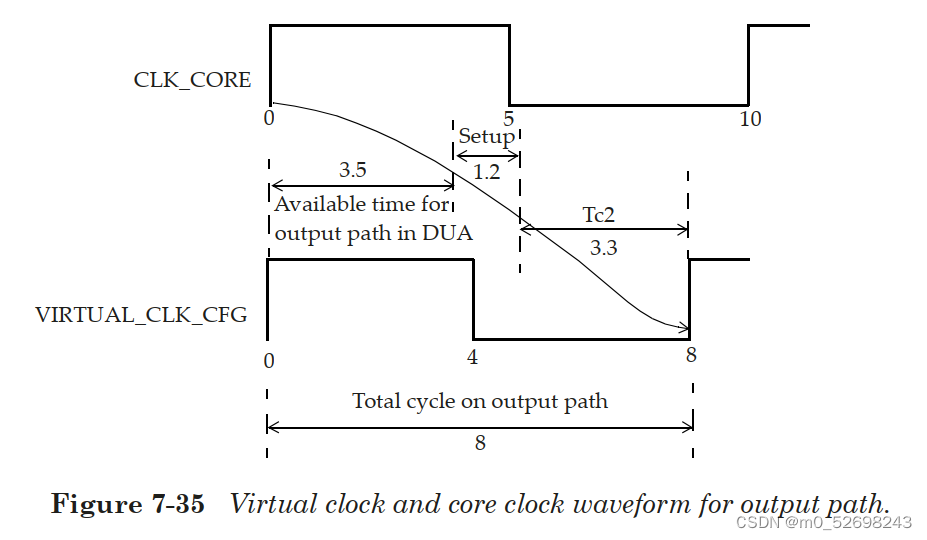

五 虚拟时钟

虚拟时钟存在但是不和设计中的端口和引脚相连接。它在STA分析中用作参考,以指定相对于时钟的输入和输出延迟。

create_clock -name VIRTUAL_CLK_SAD -period 10 -waveform {2 8}

create_clock -name VIRTUAL_CLK_CFG -period 8 -waveform {0 4}

create_clock -period 10 [get_ports CLK_CORE]

set_input_delay -clock VIRTUAL_CLK_SAD -max 2.7 [get_ports ROW_IN]

set_output_delay -clock VIRTUAL_CLK_CFG -max 4.5 [get_ports STATE_O]

六完善时间分析

主要使用如下命令:

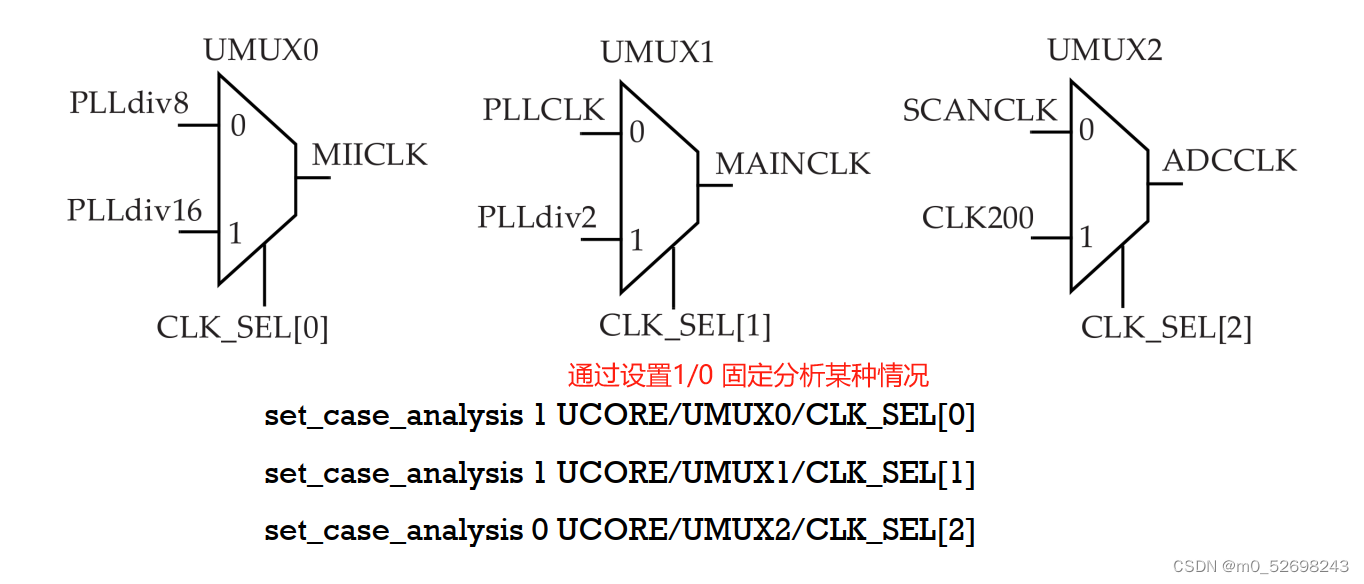

set_case_analysis:声明单元引脚上的固定值,或者输入端口的固定值;

set_disable_timing:断开单元时序弧;

set_false_path:STA不需要进行分析检查的路径。

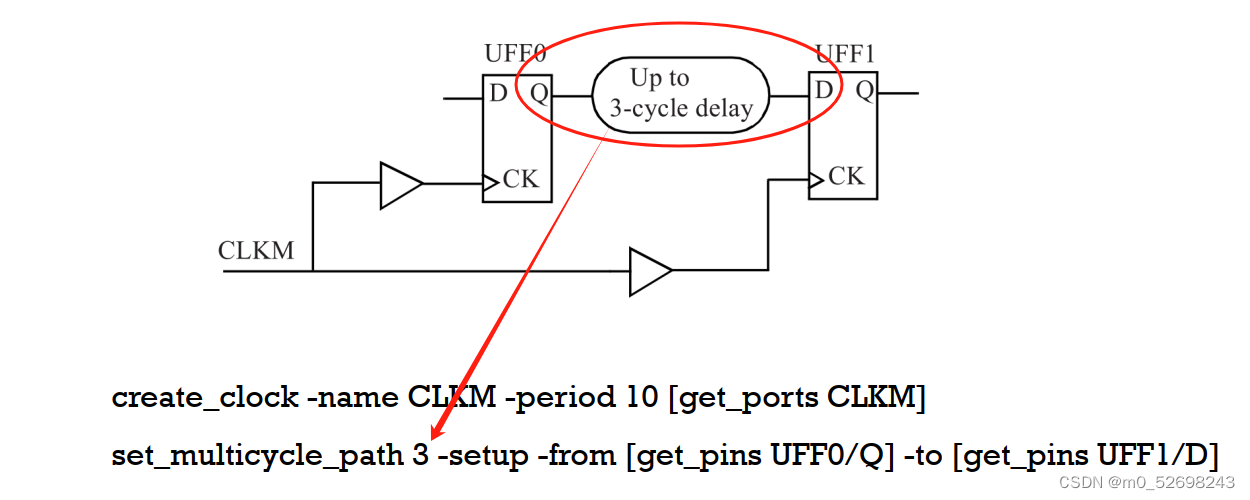

set_multicycle_path:声明可能耗费超过一个周期的路径。

1 set_case_analysis

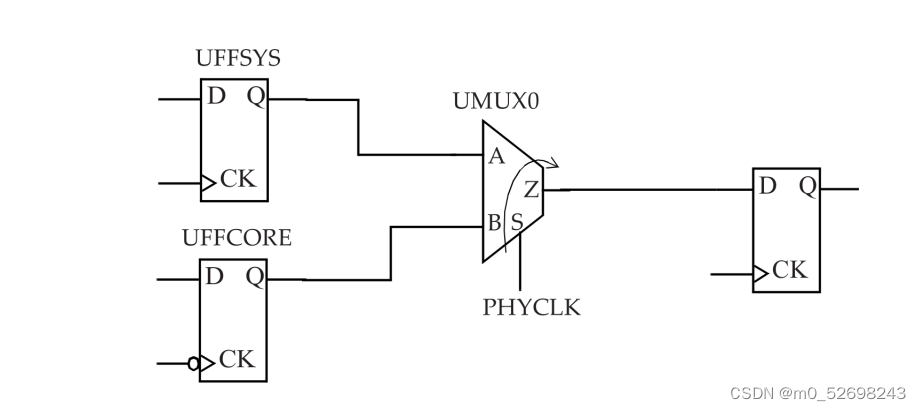

2 set_disable_timing

由选择器控制端S到输出端Z的路径也算是数据路径的一部分,但是没有分析的必要。因为我们关心的是数据传输的时序情况。

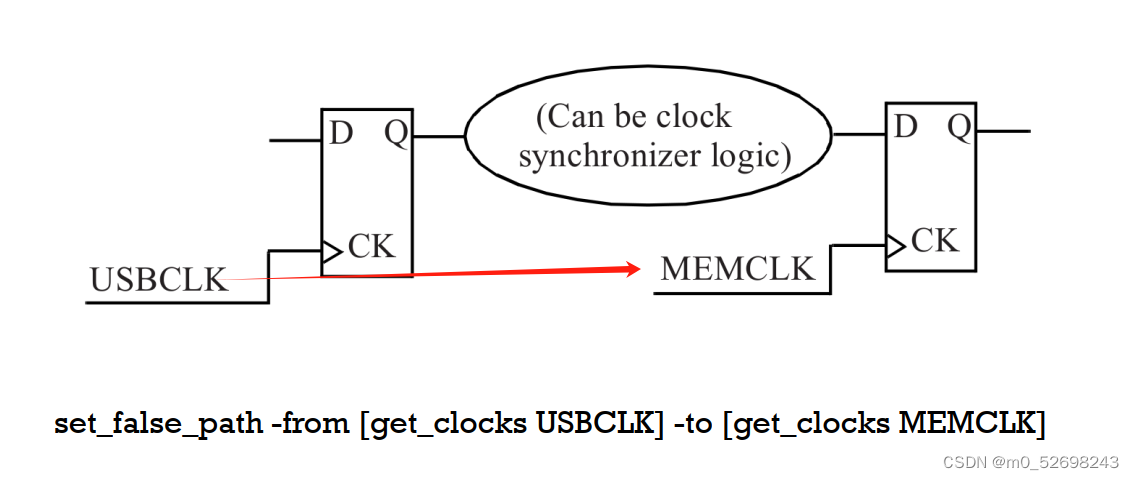

set_disable_timing -from S -to Z [get_cells UMUX0]3 set_false_path

伪路径约束(对于跨时钟域的模块之间的路径)不予分析.

4 set_multicycle_path

输入到输出的延迟跨越了多个时钟周期

6032

6032

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?