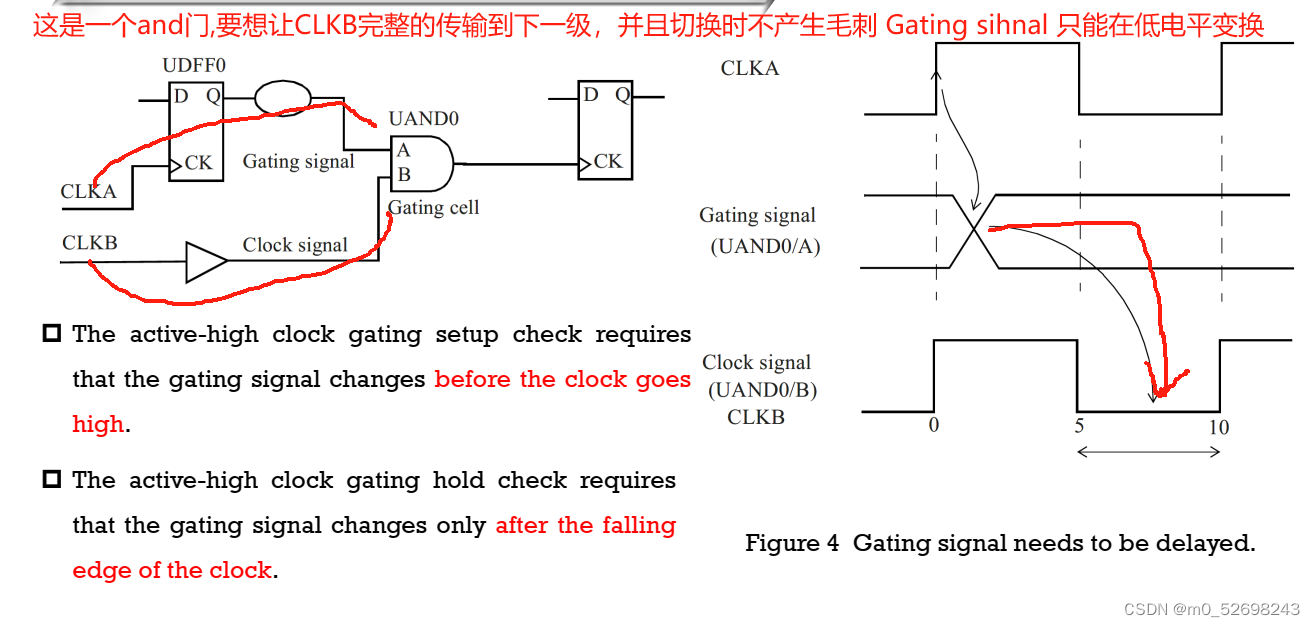

latch和与门间隔不能太远

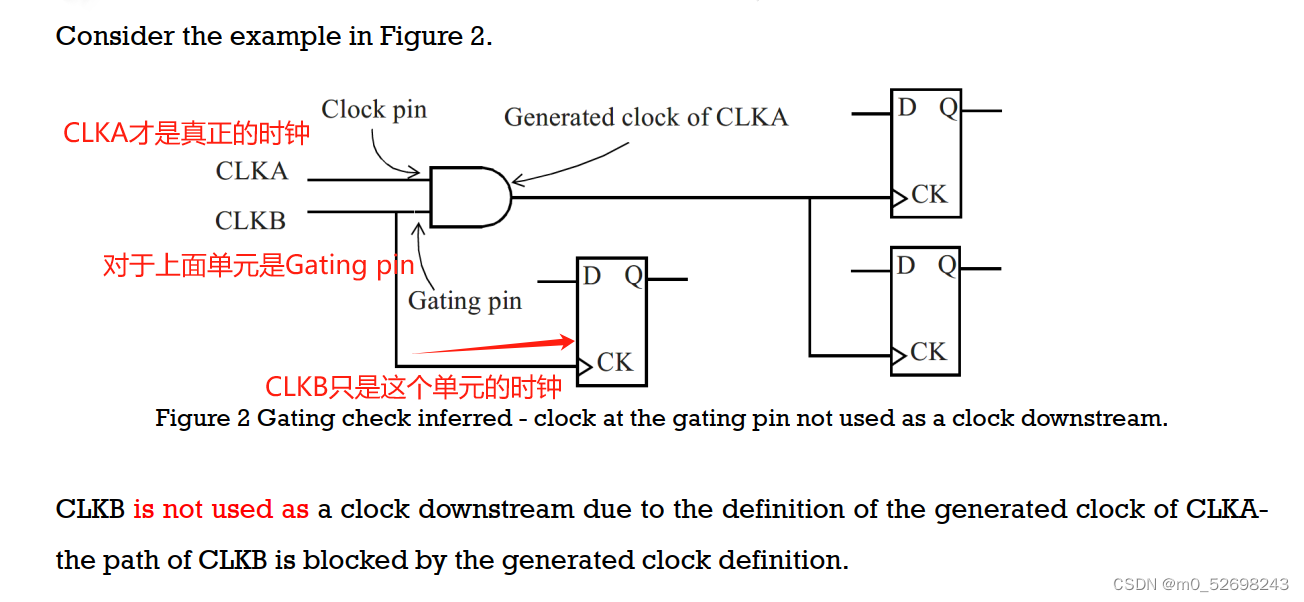

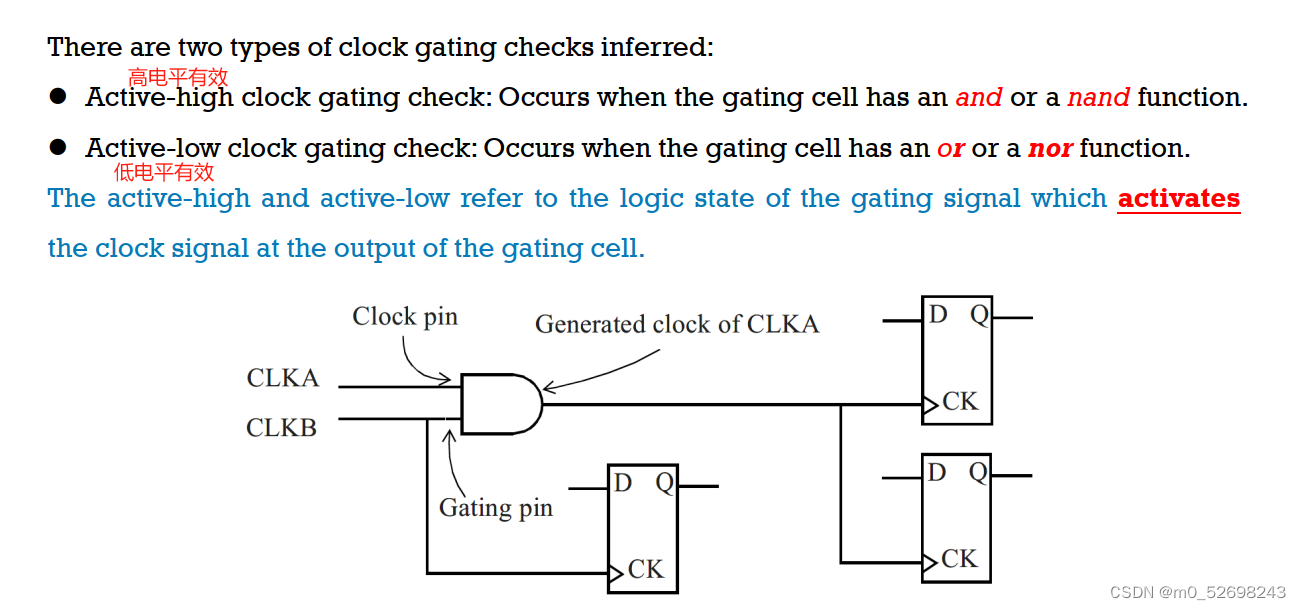

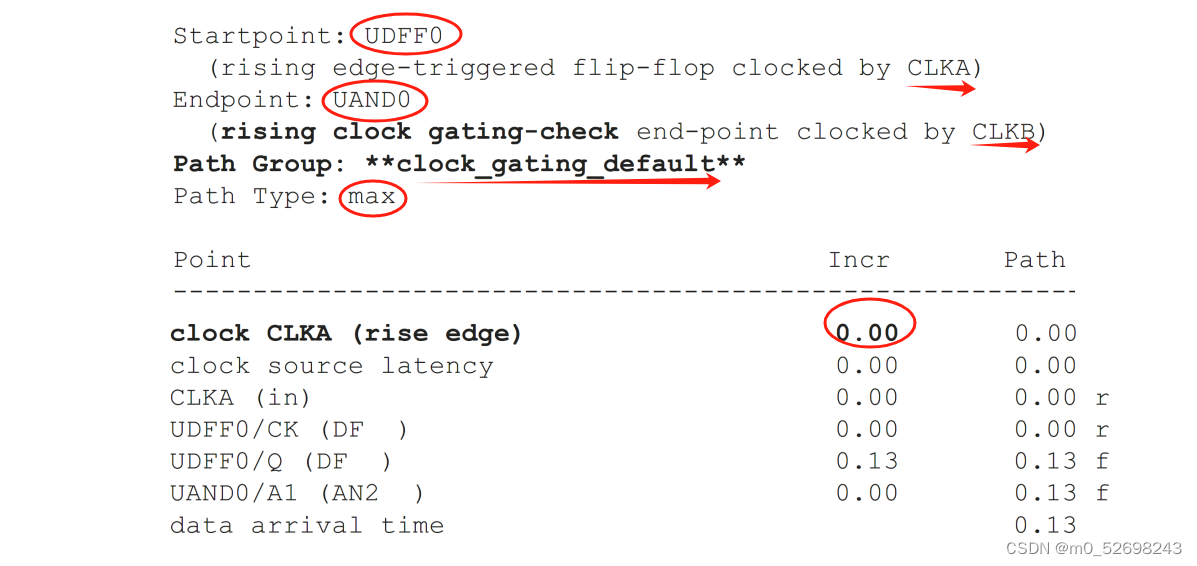

Clock Gating Checks发生:当一个门控信号(Gating signal)能够控制逻辑单元中时钟信号(Clock signal)的路径时。

穿过cell的时钟必须被用作下游的时钟。如果在门控单元之后没有将时钟用作时钟,则不会推断出时钟门控检查。

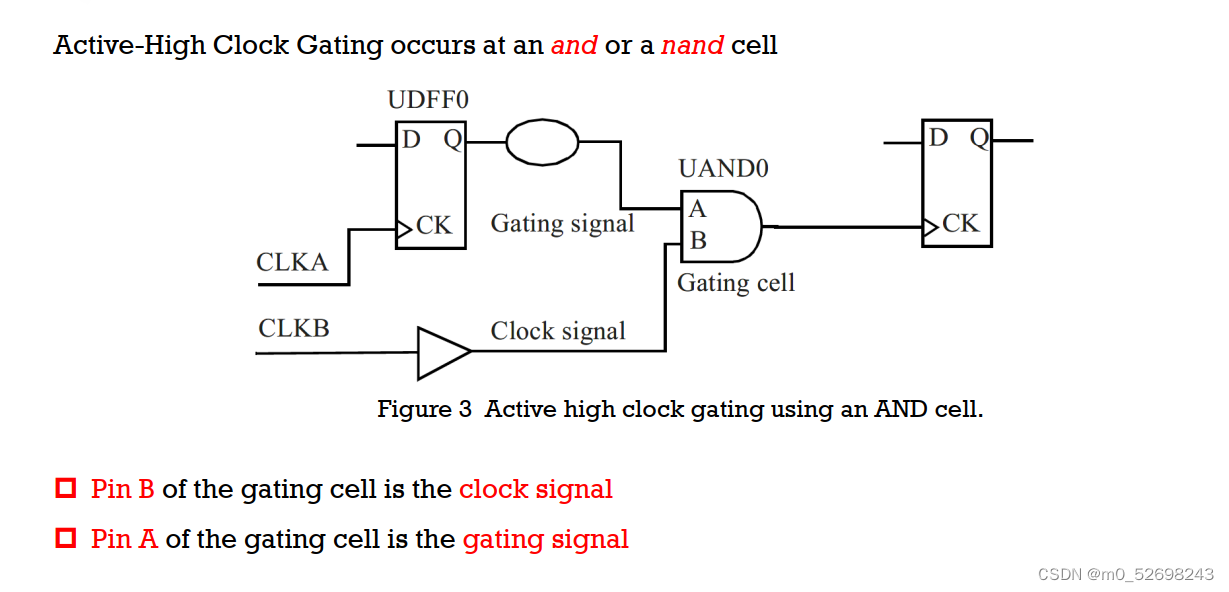

1"and"门

时钟定义:

时钟定义:

create_clock -name CLKA -period 10 -waveform {0 5} [get_ports CLKA]

create_clock -name CLKB -period 10 -waveform {0 5} [get_ports CLKB]

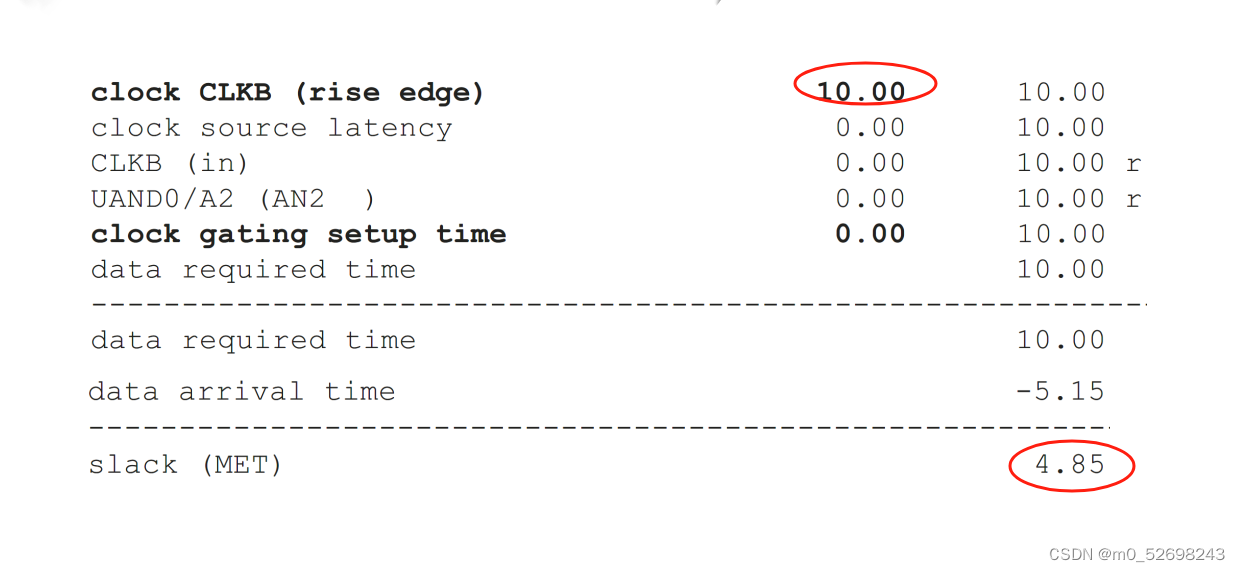

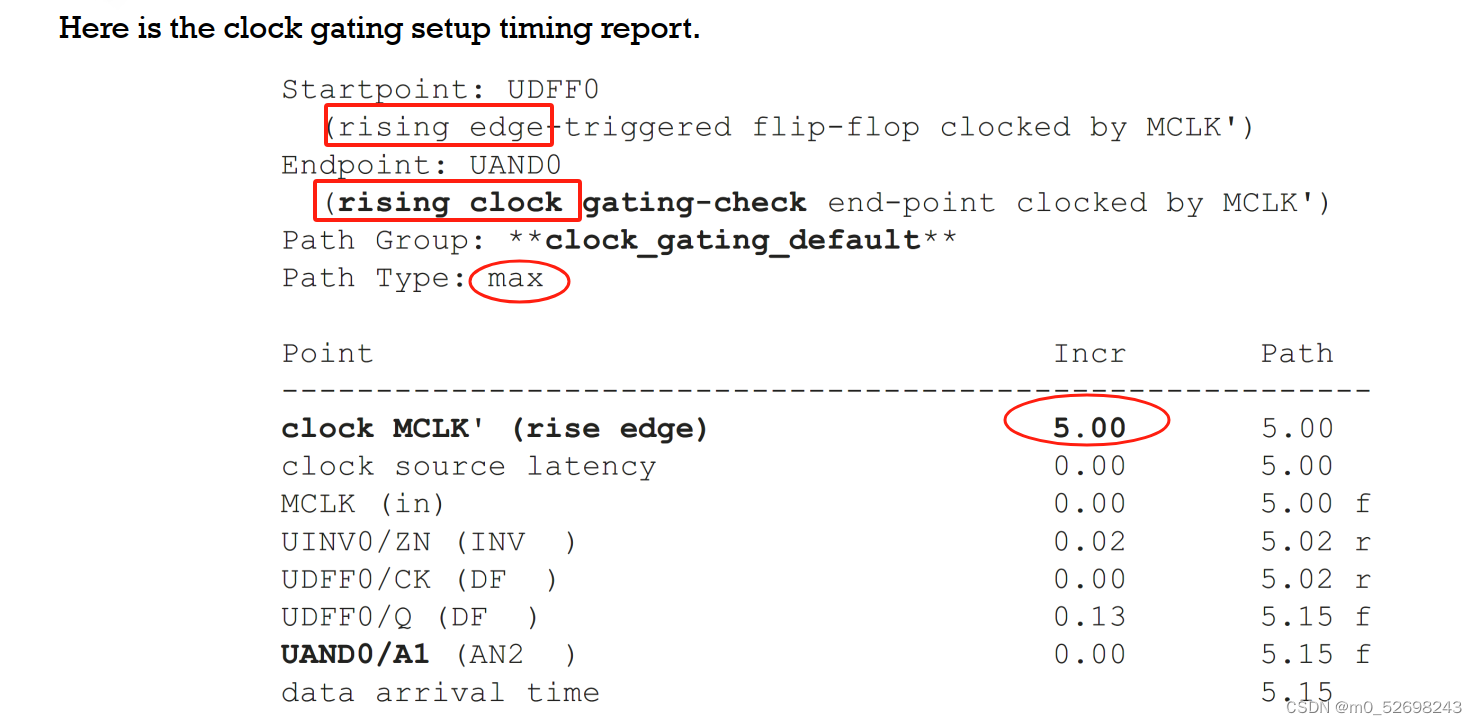

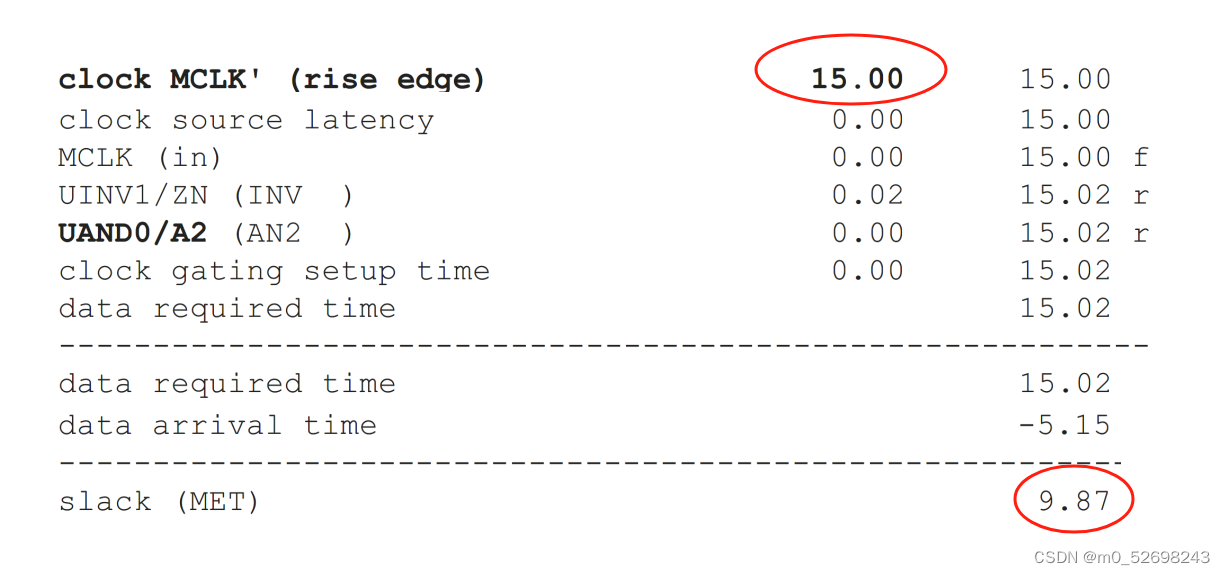

Setup Clock

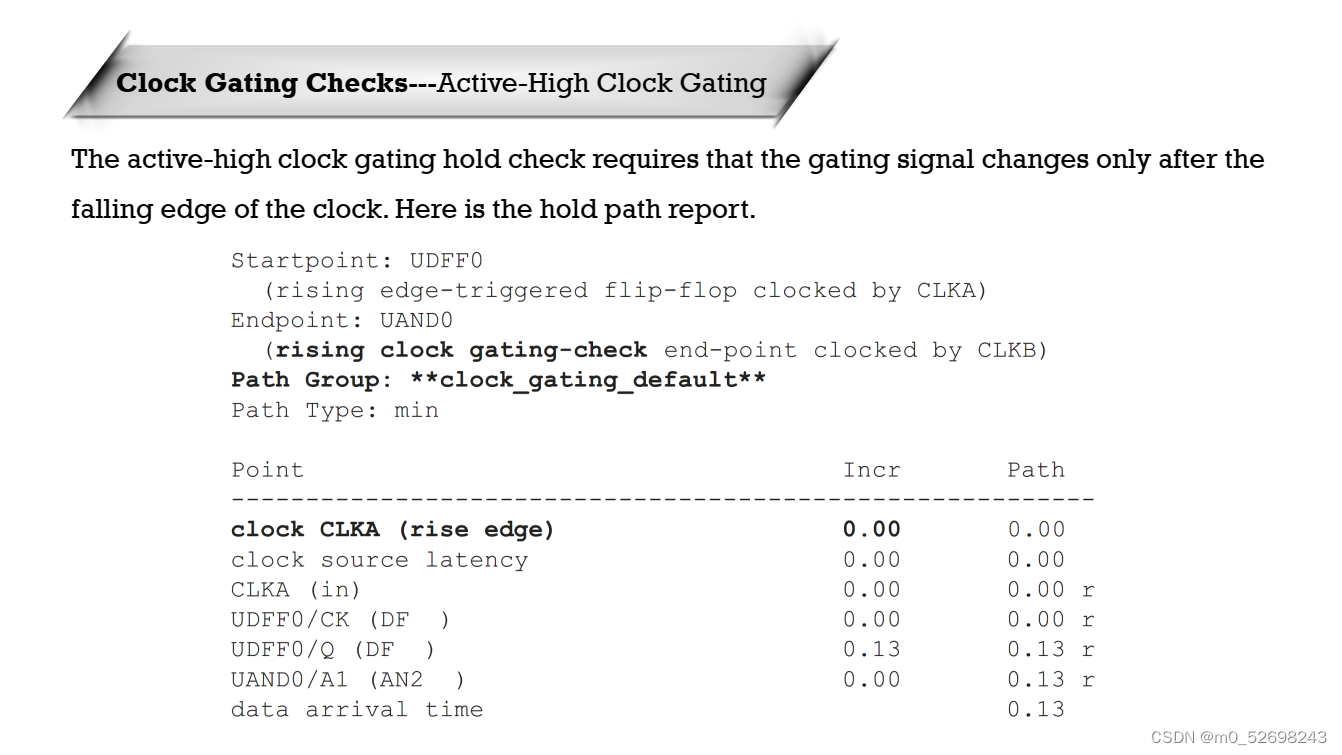

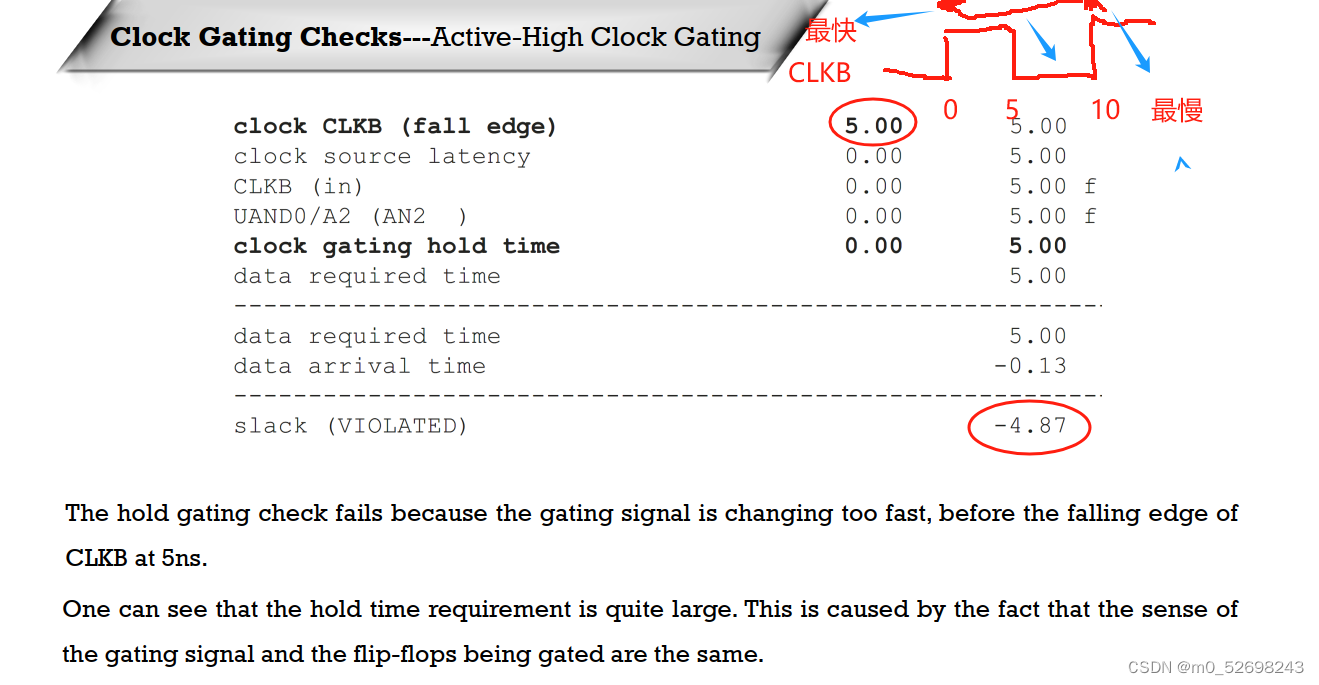

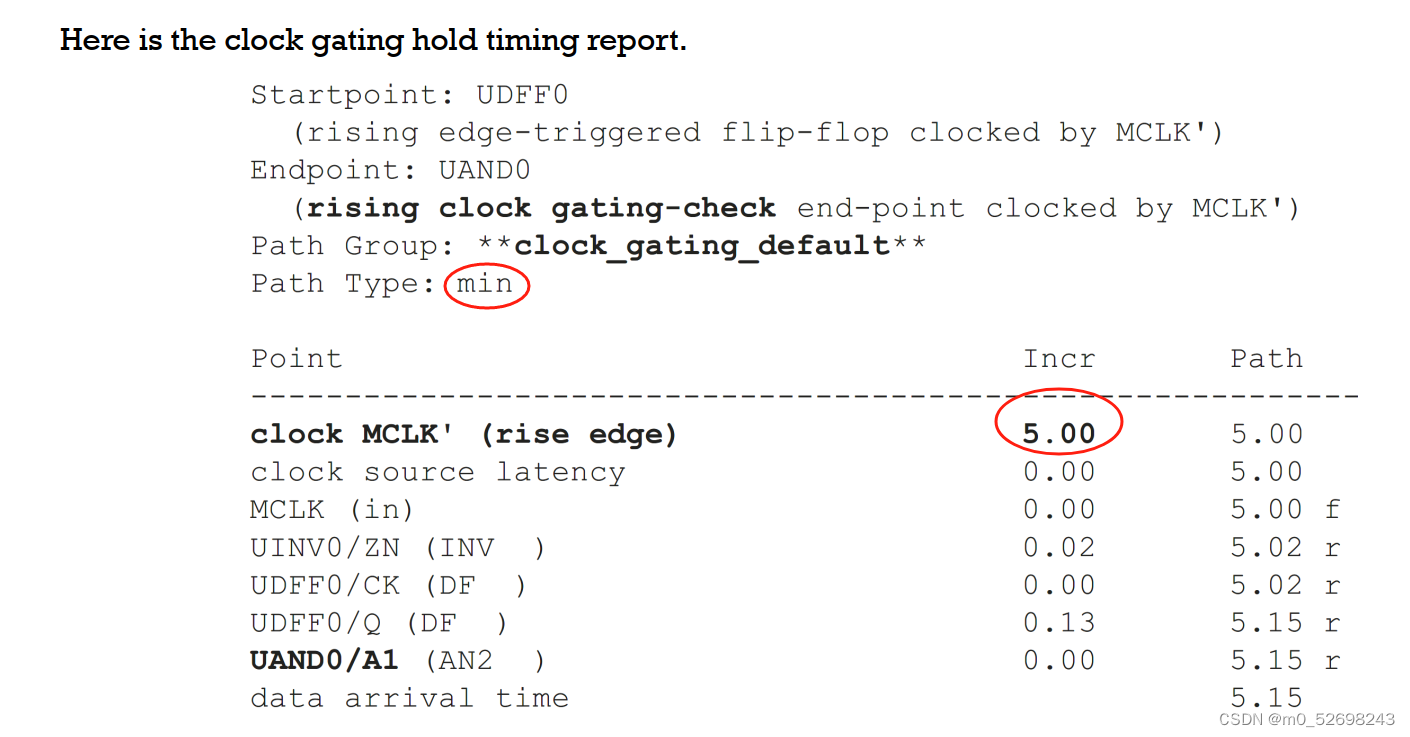

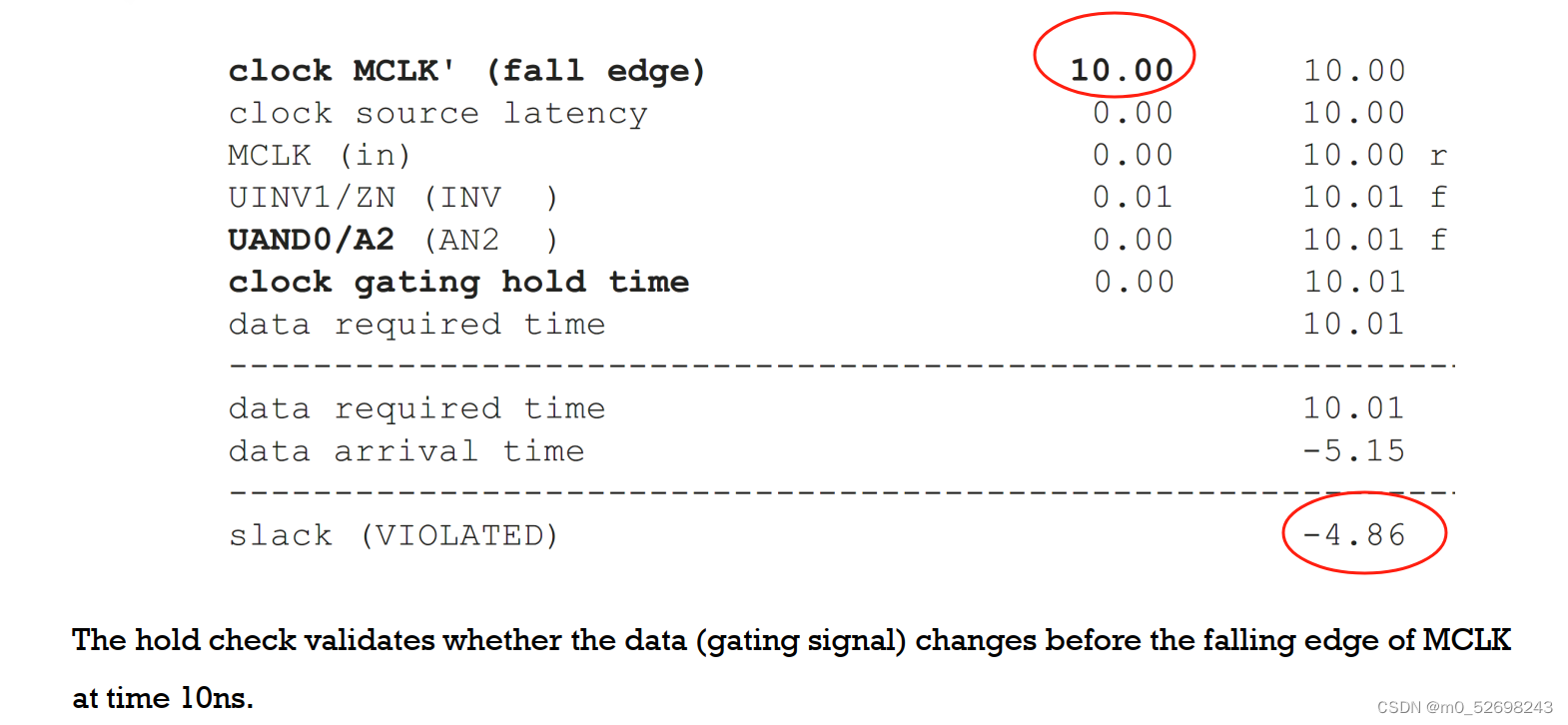

保持时间检查报告

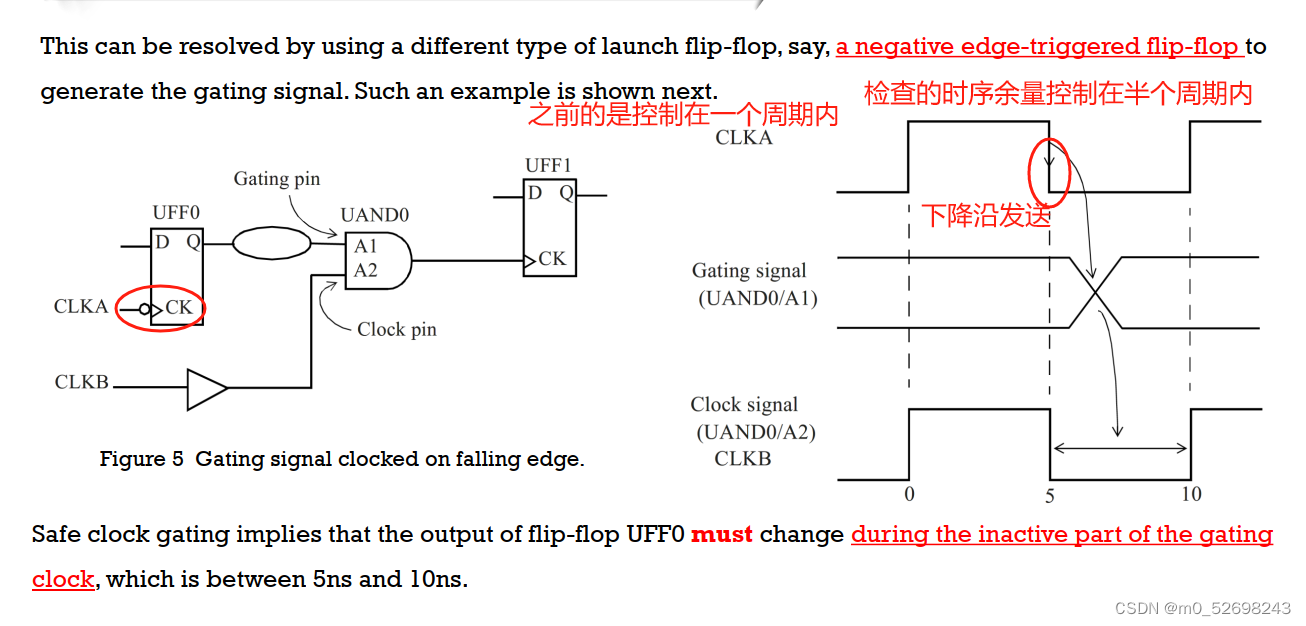

利用半周期进行约束(采用下降沿)

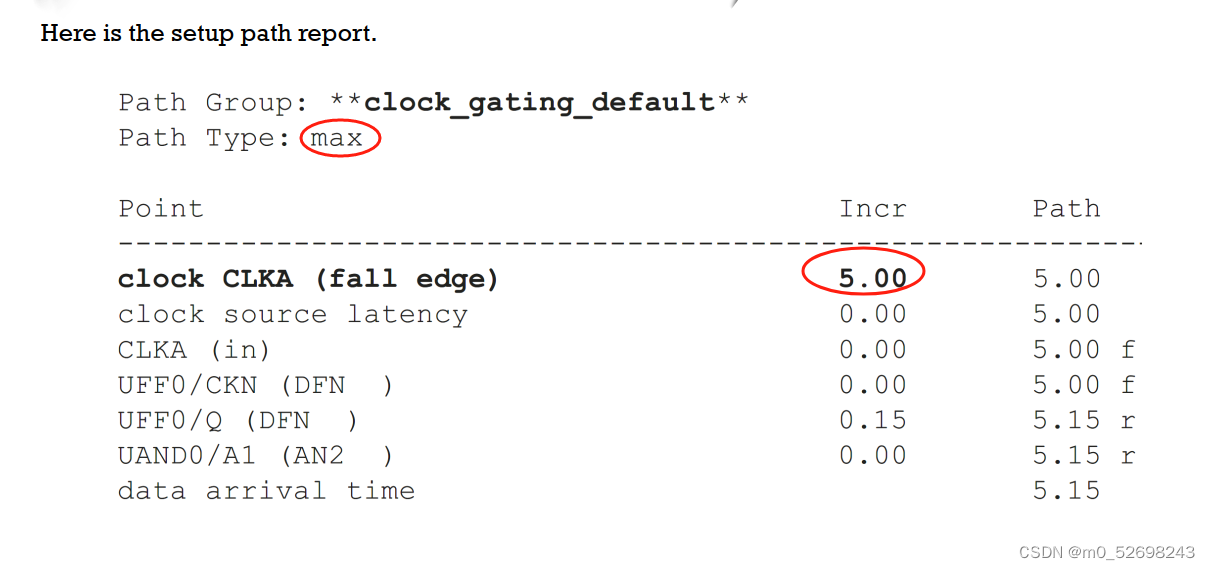

时序报告:

Setup Check

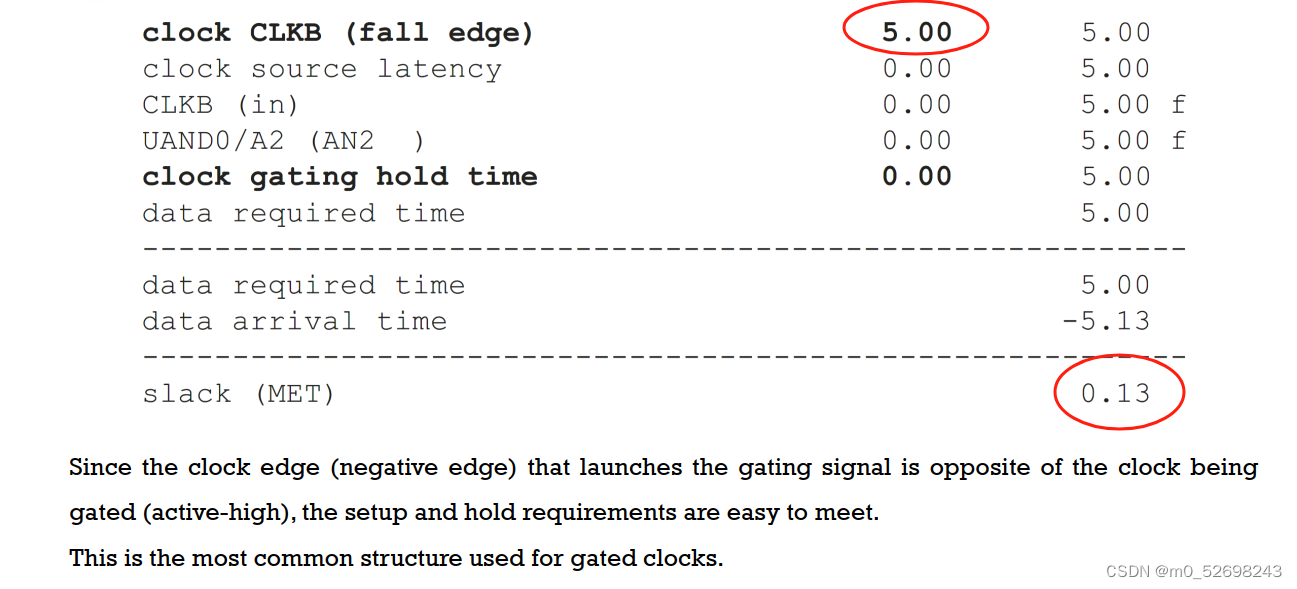

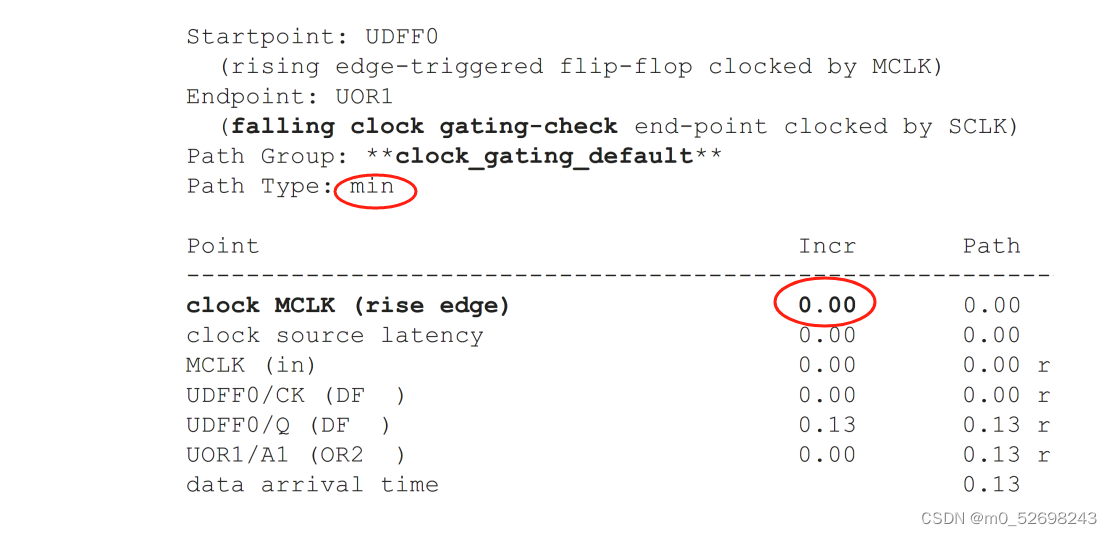

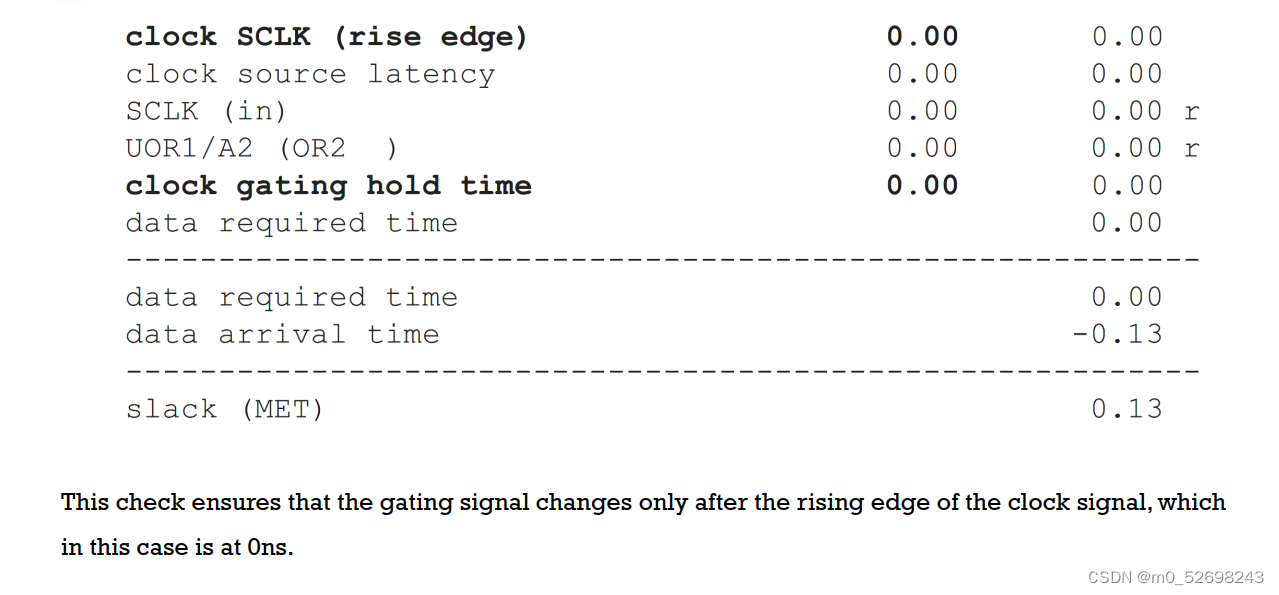

Hold Check

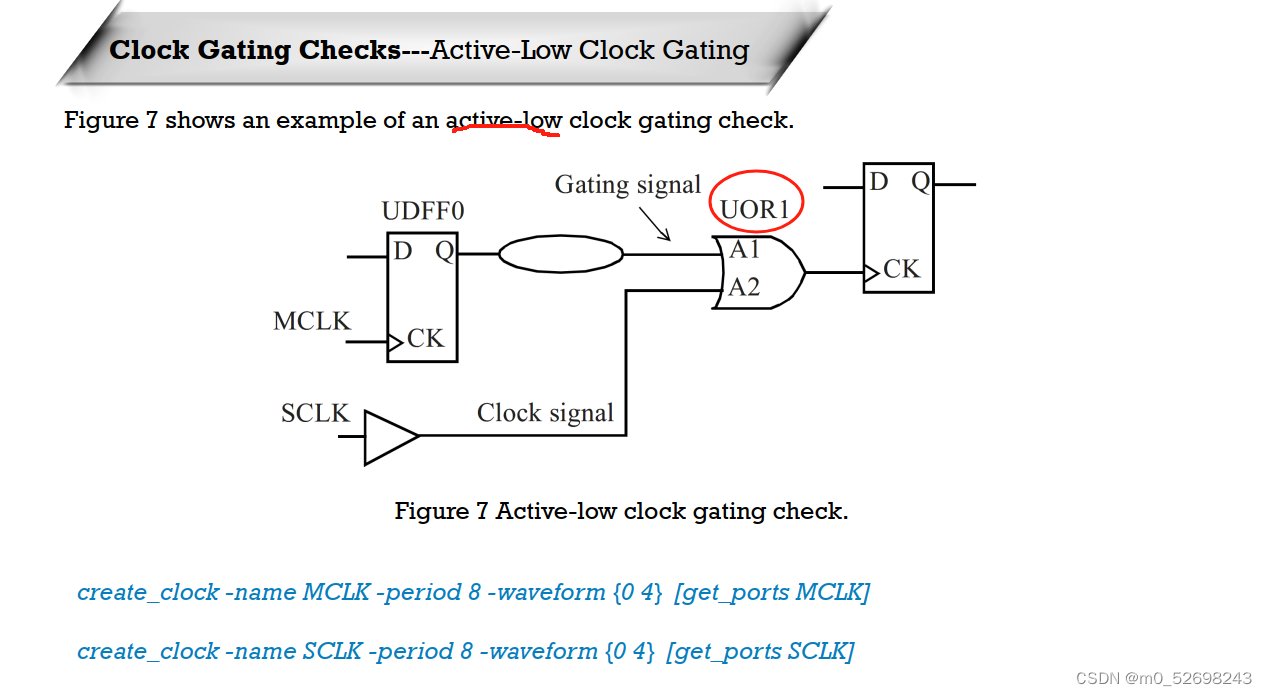

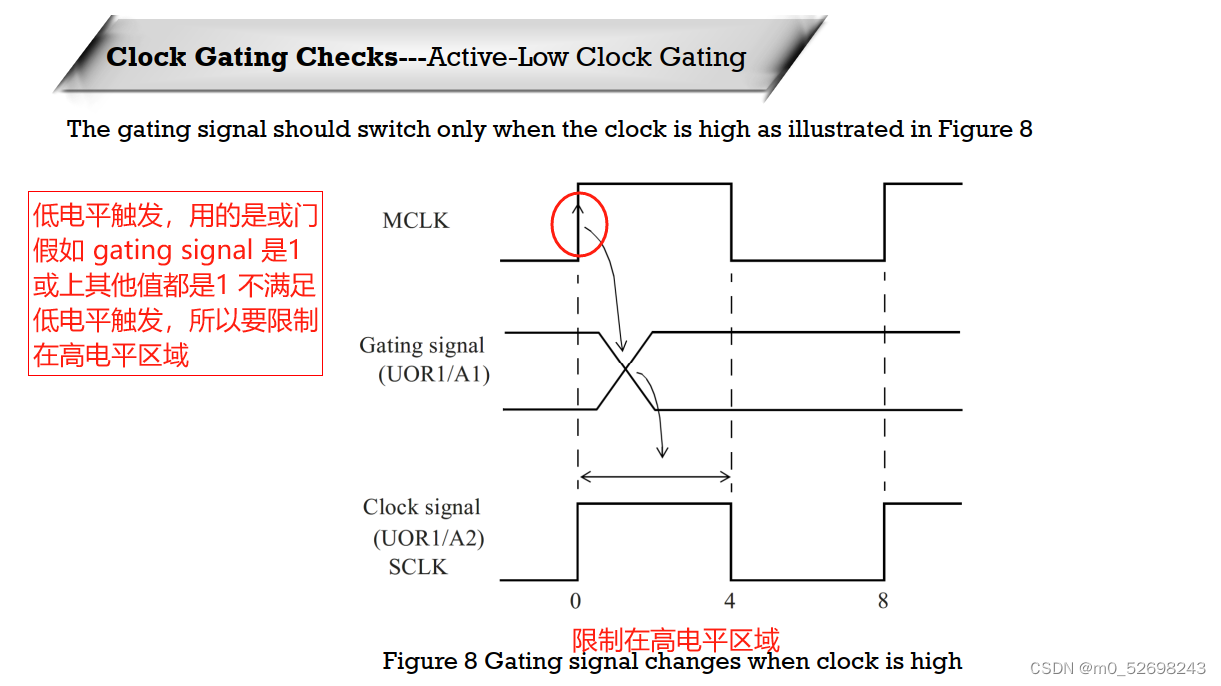

2低电平触发(用"or"门)

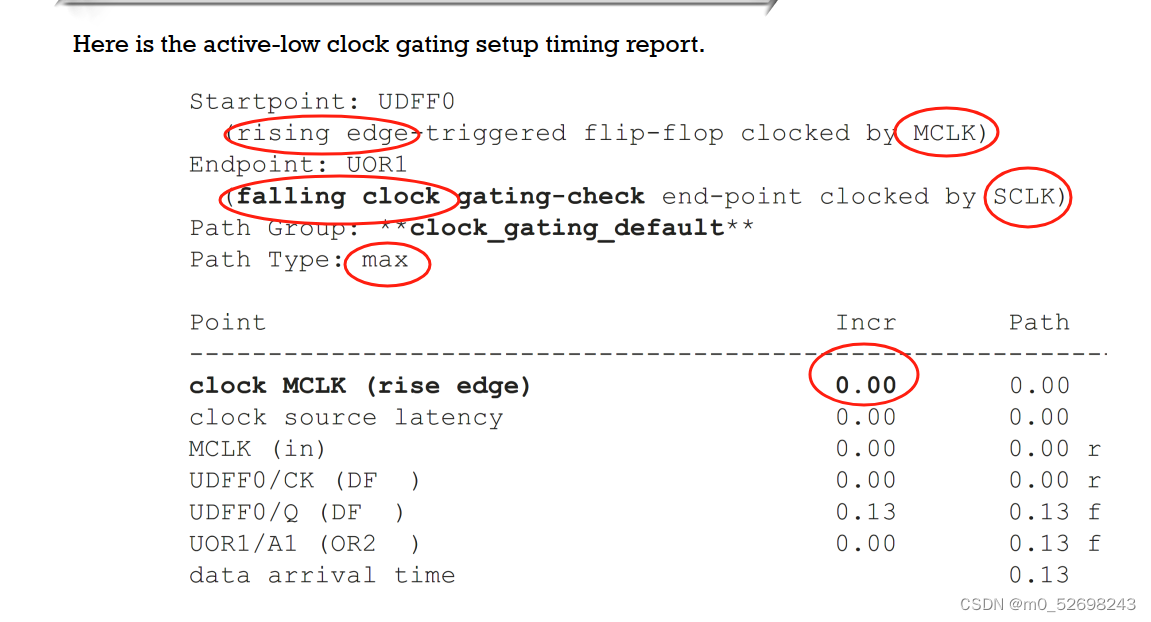

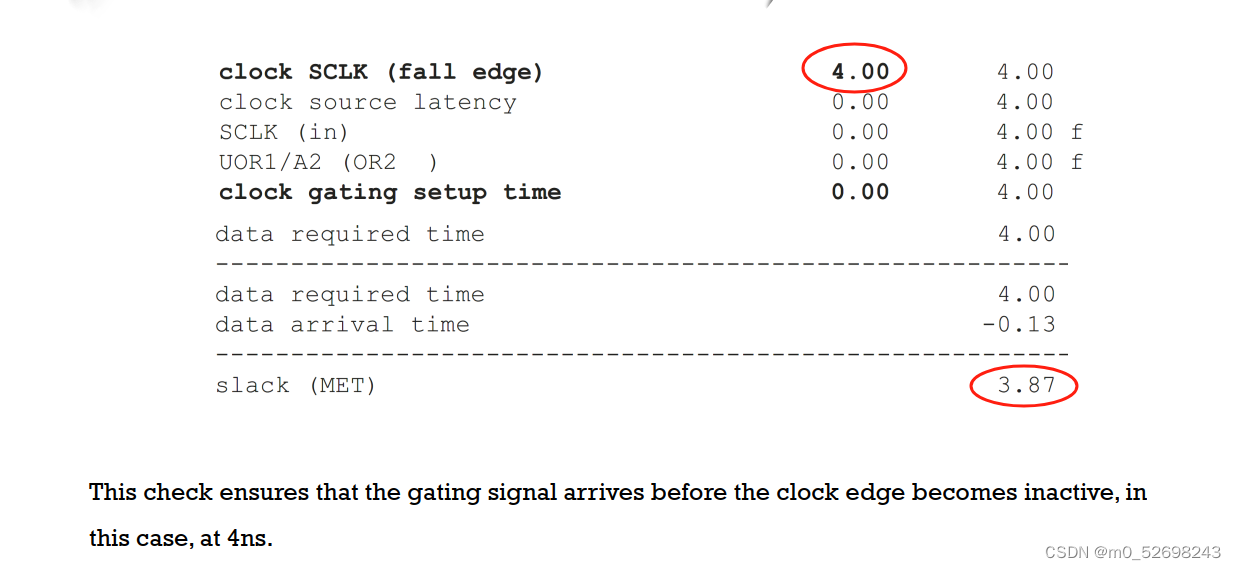

时序报告

Setup Check

Hold Check

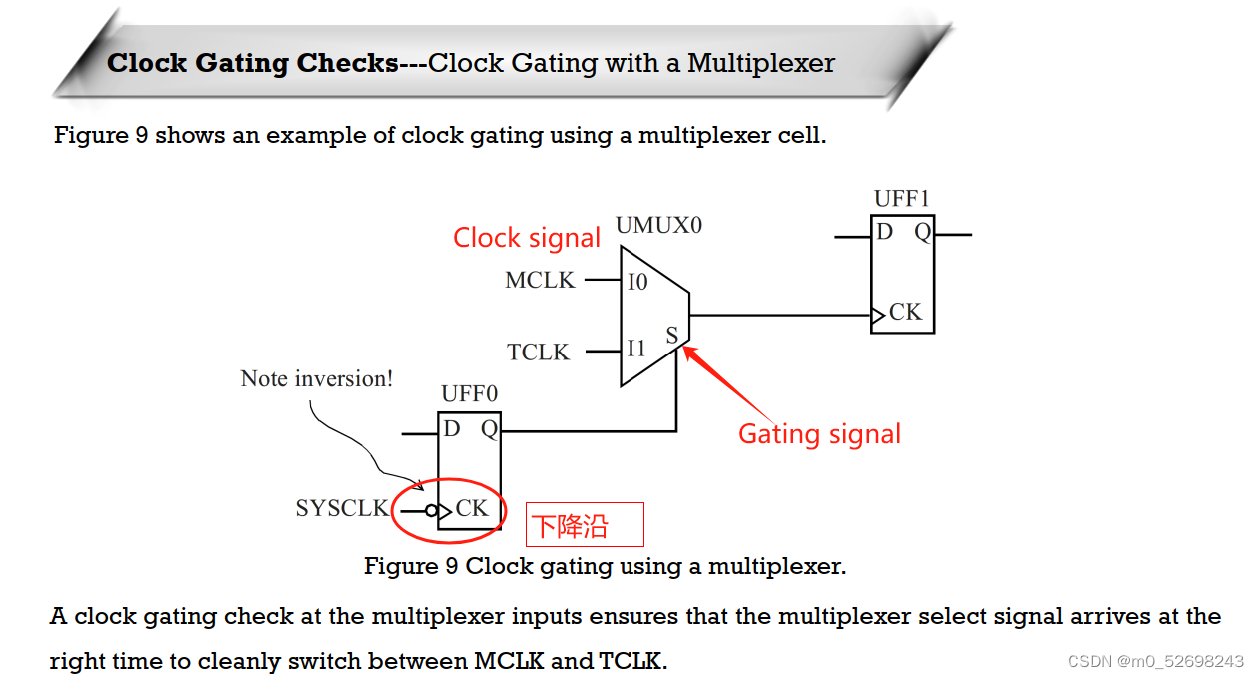

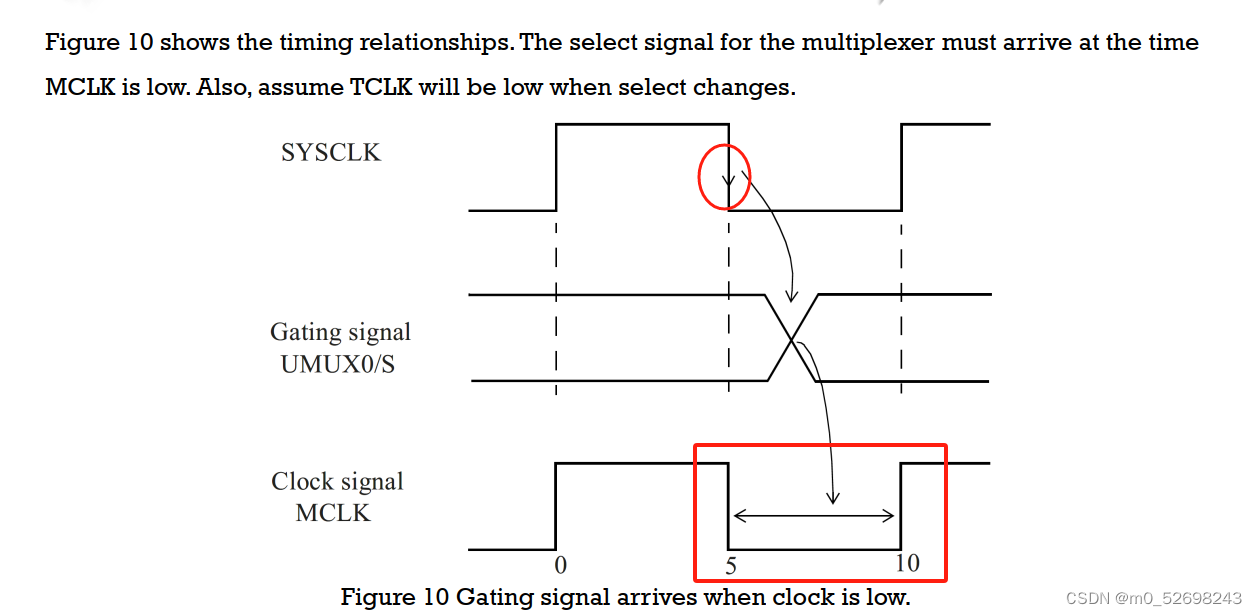

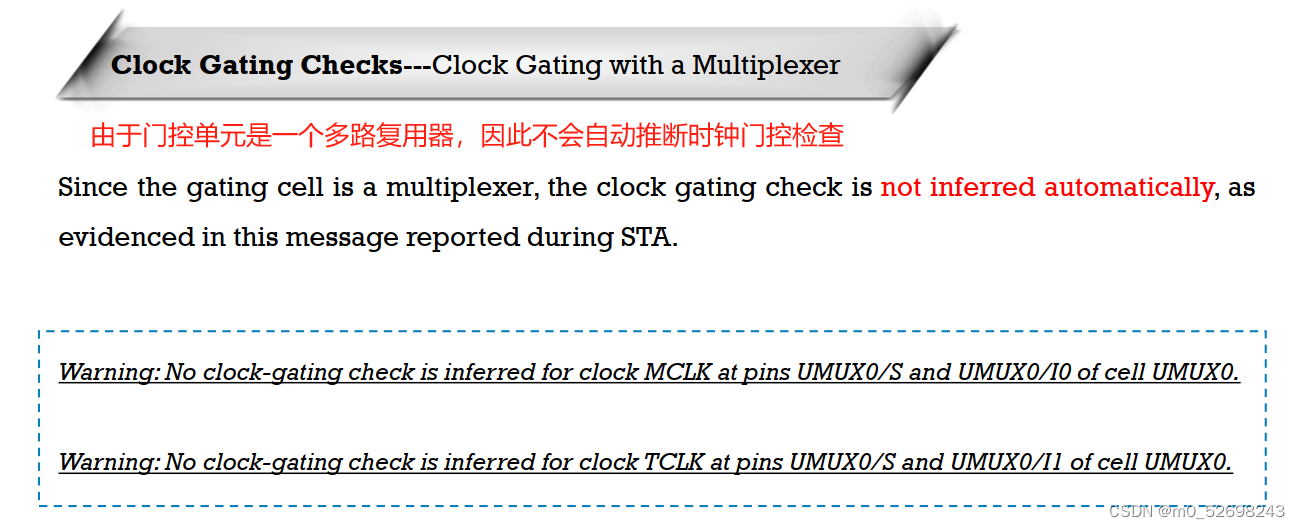

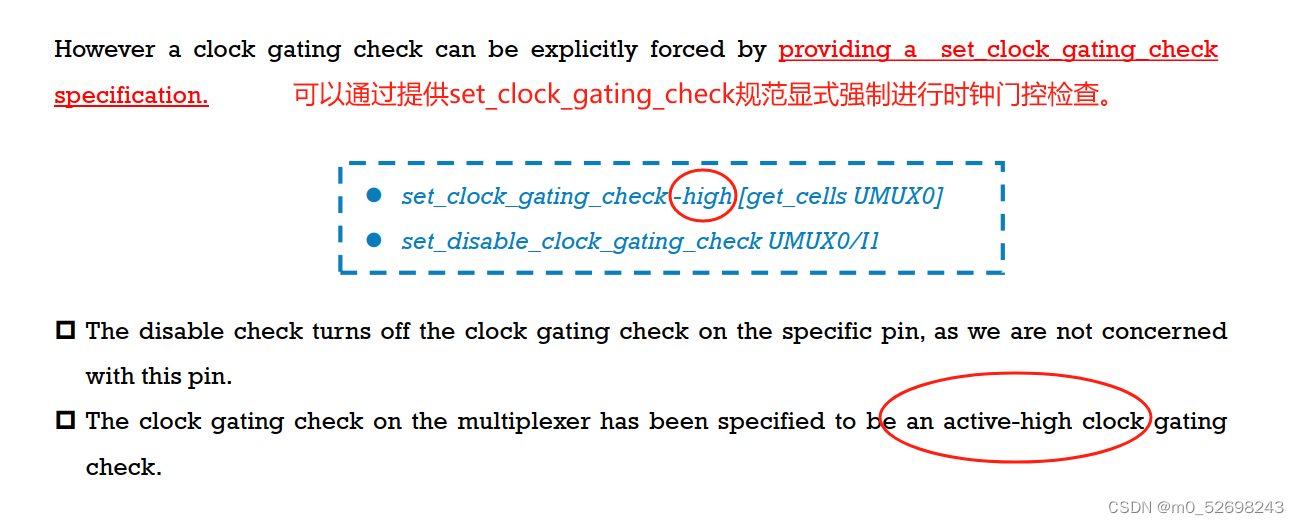

3MUX(选择器)

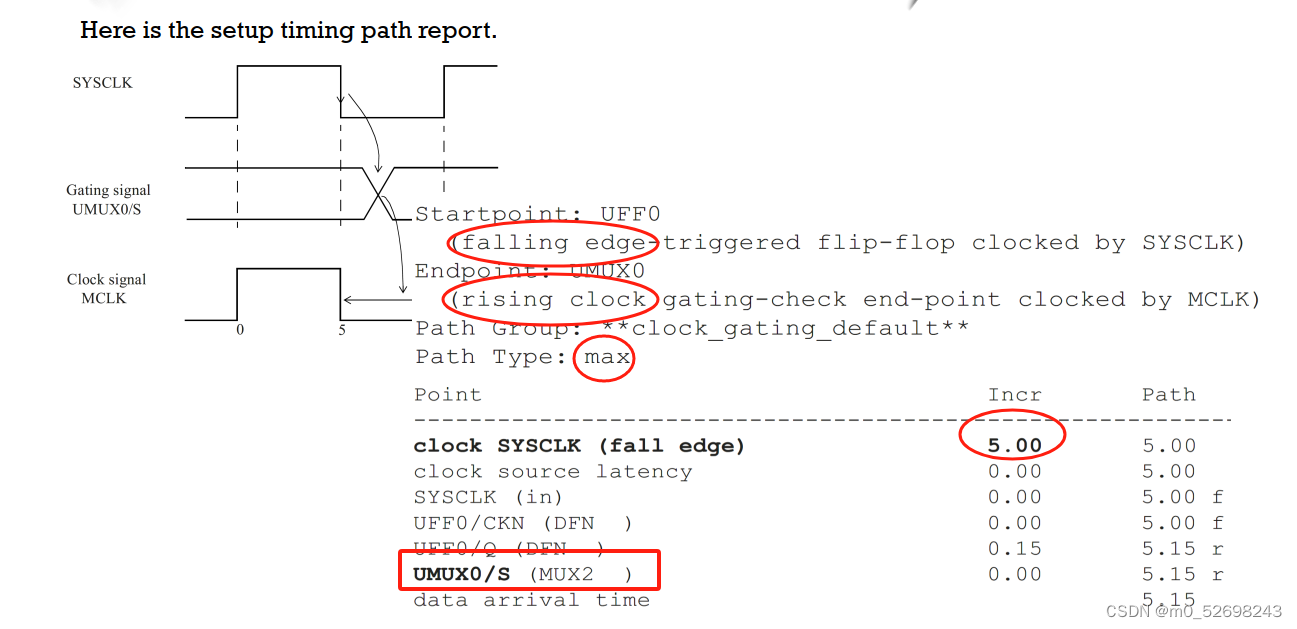

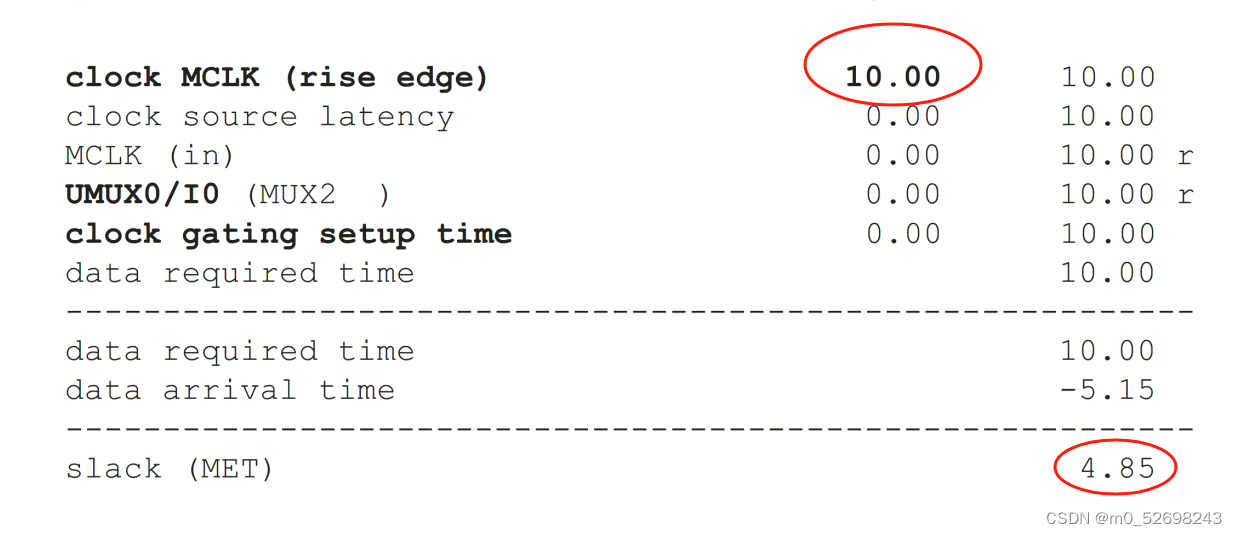

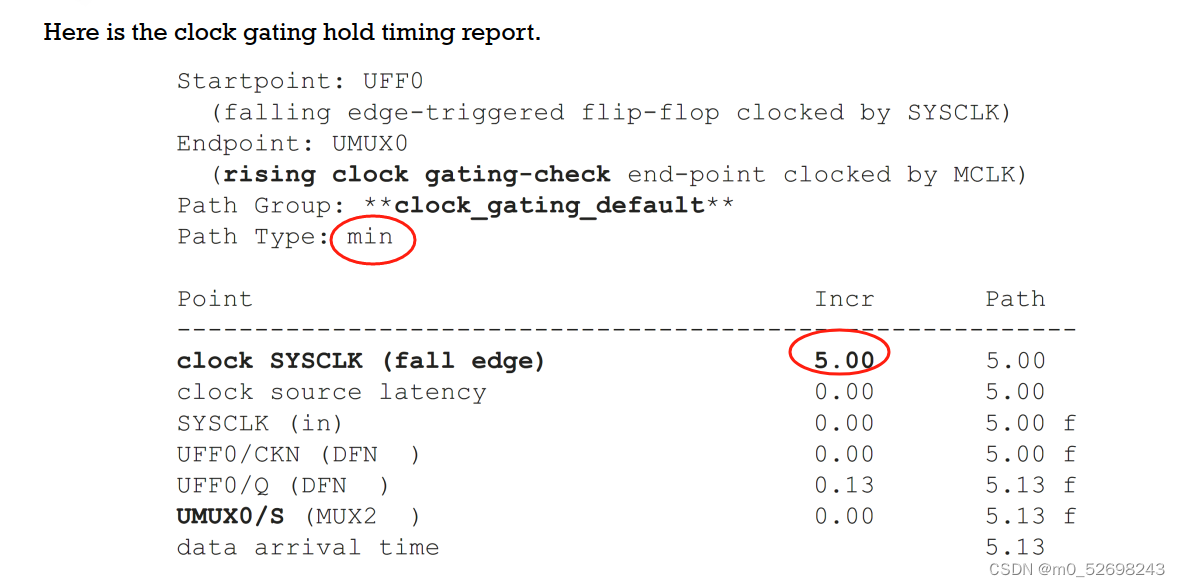

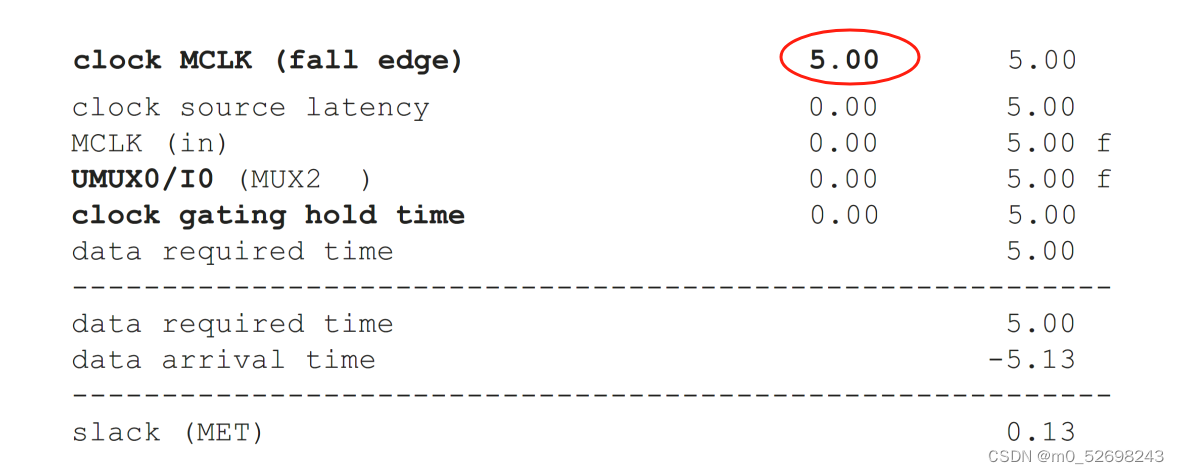

时序报告

Setup Check

Hold Check

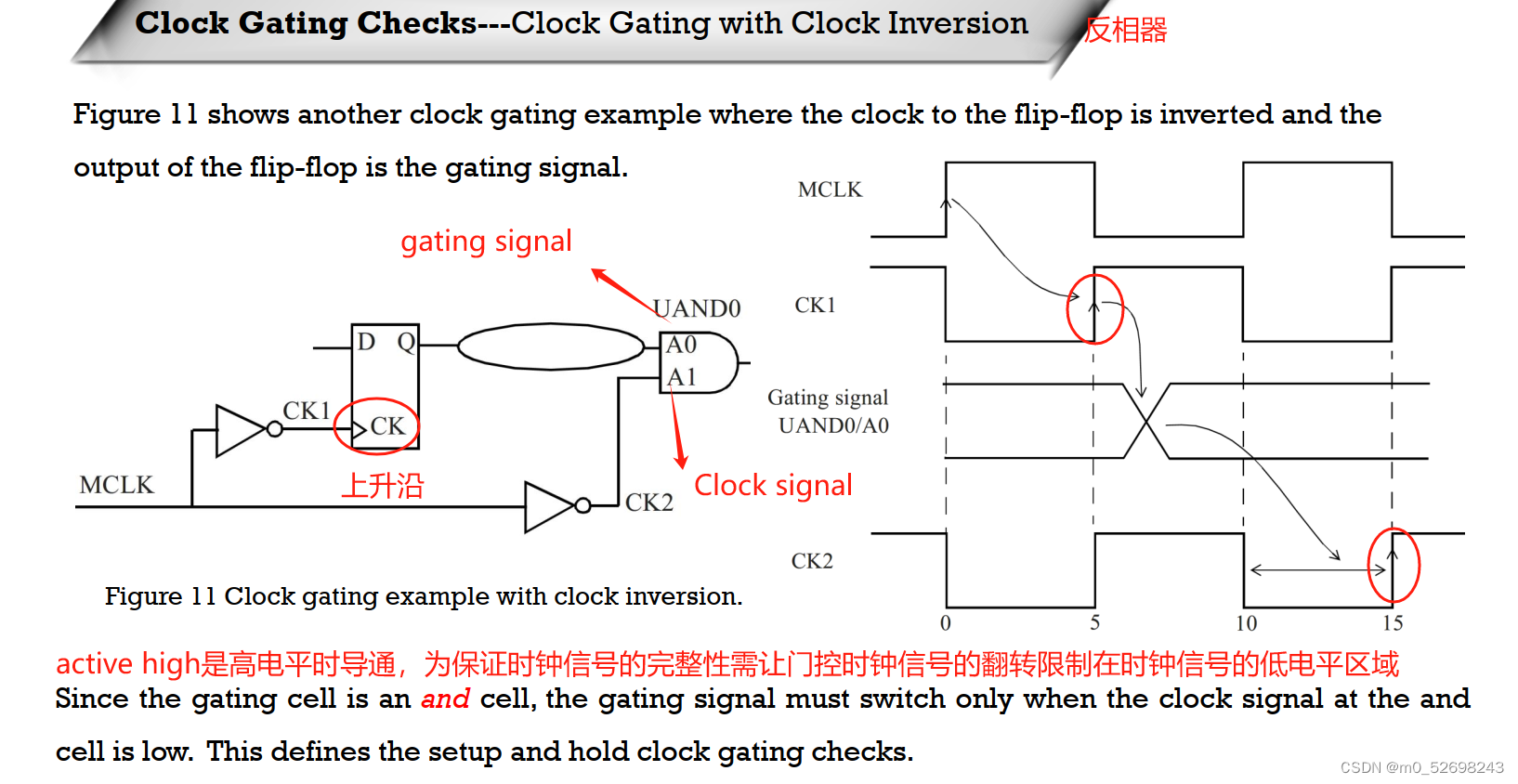

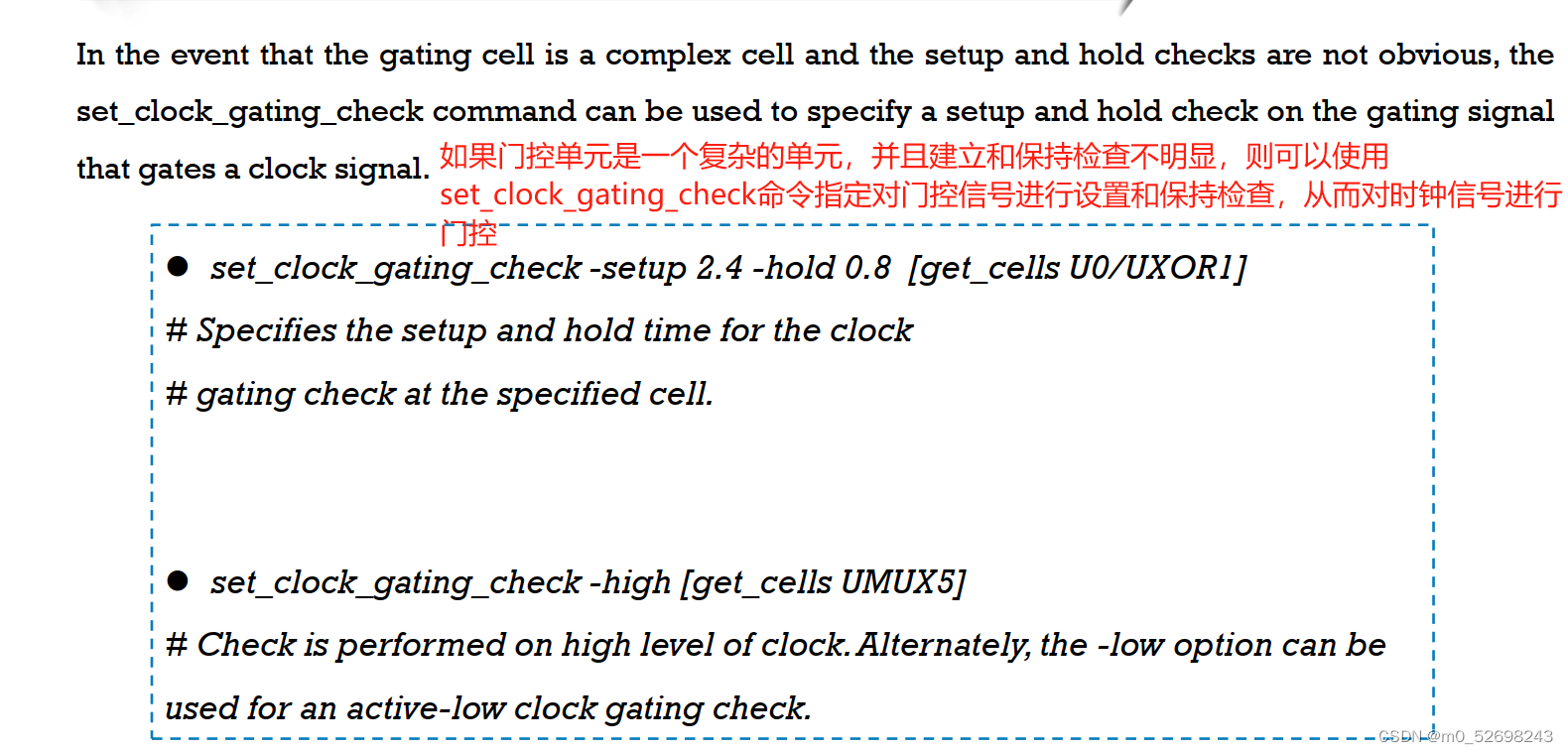

4反相器

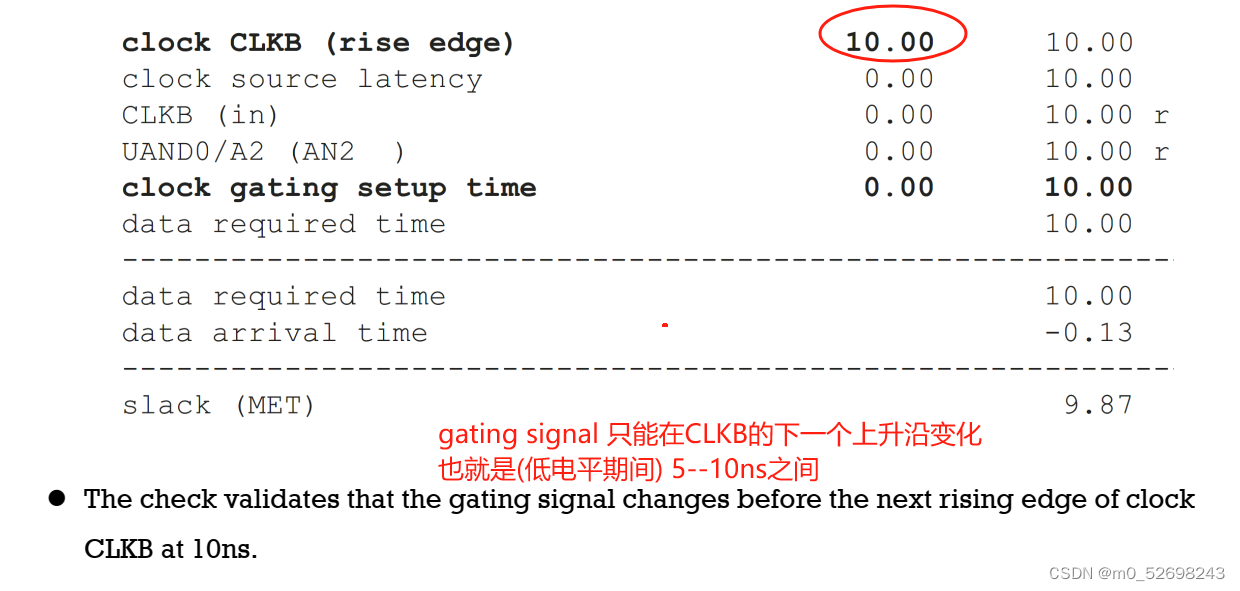

时序报告:

Setup check

Hold check

总结

active-high 高电平导通,为保障时钟能够有效的传输到下一级中,需要让门控信号的翻转限制在时钟信号的低电平区域。

active -low 与此相反

6633

6633

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?