DVT工具适用于仿真代码的Build阶段,因为相比较于Questasim,DVT可以提供更加详细的error信息,便于快速通过编译阶段。但是DVT不适于用于Simulation!

此外,DVT可以帮助新人学习SV以及UVM语法。

Tips: 基于Linux操作系统,大多数公司都采用VCS。VCS是整套仿真工具,DVE是VCS的一个前端界面。

1. channel通道的物理实现是怎样的?

MCDF中并没有实现channel,而是把通道的信号直送到slv_FIFO。

2. FIFO是一个32位宽深度32的存储器

3. 有符号数用补码形式表示,无符号数用原码表示(0或正数)。比如,8位有符号数表示范围-128~127,而无符号数可以表示0~255。因此,在SV中首先要区分操作数是有符号还是无符号数,然后才能知道它的数值具体是怎样的!

原码、反码、补码补充:

原码的符号位不变,其余各位翻转->反码;反码加‘1’->补码,需要注意的是加'1'的过程中符号位始终不变,即使最高位有进位产生也不会变化。如下例子:

[+1]: 0000_0000 -> 反码: 0111_1111 -> 补码: 0000_0000;

由此我们也可以计算:

[-1] + [-127] = 1000_0001[原] + 1111_1111[原] = 1111_1111[补] + 1000_0001[补] = 1000_0000[补] = -128, 即-128对应的补码是 1000_0000;

4. 波形中mcdt为何晚了三拍才开始发送数据?

原因如下:slv0_req_s在第一拍后拉高,表明slv0_FIFO中有数据并请求输出; a2s0_ack_s是arbiter返回给slv0_FIFO,表示允许slv_FIFO输出数据; 等到第三拍时,从slv_FIFO中直接输出到arbiter的输出端,即mcdt_data_o。

Reference:原码, 反码, 补码 详解 - ziqiu.zhang - 博客园 (cnblogs.com)

5. 接口interface

接口可以简单的理解为两个modul之间连线的集合。它可以用于设计,也可以用于验证。当用于设计时,常常会用到modport,以减少因为信号/连线的方向错误带来的问题。在验证中使用接口,可以使连接变得简洁而不易出错。另外,interface可以在硬件环境和软件环境中传递,例如作为module的端口列表,也可以作为软件方法的形式参数(virtual interface,此时interface不能例化,详情见绿皮书第十章)。

5.1 Interface与Module

相同点:interface可以在module中声明参数、输入输出端口、函数和任务、过程语句块等,基本上与Module别无二致。

不同点: Interface中可以例化interface,但是不能在interface中例化module。但是Module可以例化二者。

5.2 Interface与Struct

相同点: 都可以作为变量\信号的组合

不同点:struct中不能声明过程语句块,函数和任务,只能存储数据\变量。

6.竞争问题

简单的讲,因为时钟与被采样信号之间存在若干个delta-cycle,造成仿真波形上的结果与log信息不一致,当然log给出的信息是可靠的。

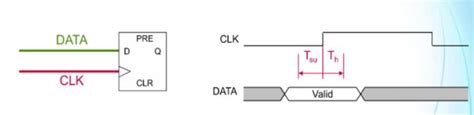

6.1设计问题:建立时间(Setup Time)和保持时间(Hold Time)

Setup Time: 数据必须在时钟上升沿之前的这一时间段之前到达D端,这样才能保证该数据存储在寄存器中。

Hold Time: 在D端,数据必须在时钟上升沿之后的这一段时间之内保持不变,这样才能保证触发器正确翻转。这也是SV时钟块中驱动输出数据要在时钟沿之后添加延时的意义。

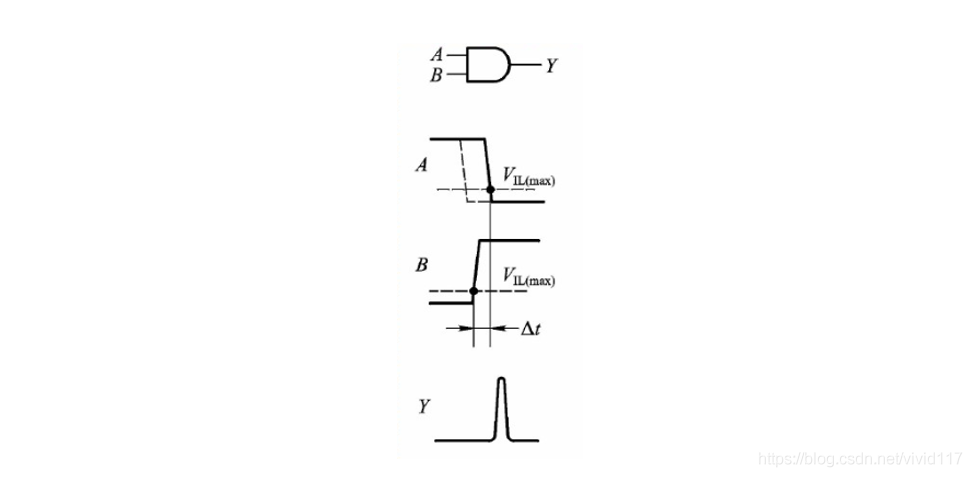

6.2 组合逻辑电路的竞争冒险

如下图所示,Y本应一直保持低电平,但是A与B端信号到达端口的时间不一致,有先有后,造成在某一个很短暂的时间上,出现了尖峰脉冲,这种现象就称为竞争冒险!

6.3竞争问题的解决方法:接口中clocking!

以下是interface或者module或者program中的一个clocking示例:

clocking bus @(posedge clock1);

default input #10ns output #2ns; //模拟建立和保持时间

input data, ready, enable; //clock1的前10ns处采样

output negedge ack; //negedge限定在时钟下降沿驱动数据

input #1step addr; //#1step一个时间片,可以理解为无数个delta-cycle

endclocking

另外,如果没有default这一行定义,那么默认会在clock1的前一个step(时间片)对输入采样,在clock1后的一个#0(时间片)对输出进行驱动。

7. Windows QuestaSim加载已创建的工程

选择“File” -> 找到对应路径下的*.mpf文件并打开即可!

8. 编译顺序

对于硬件模块而言,底层模块率先编译,顶层模块最后再编译!对于测试软件而言,先编译package(如果有),然后再??

6332

6332

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?