一、引言

在模拟集成电路设计中,gm/id设计方法是一种基于晶体管跨导(gm)与漏极电流(id)比值的参数化设计方法。该方法通过利用工艺库的仿真数据,结合图表化工具,克服了传统平方律模型在短沟道器件和复杂工作区域中的局限性,成为现代低功耗、高性能电路设计的核心方法之一。而本文是我在阅读《A Basic Introduction to the gm/ID-Based Design Methodology》后写的阅读记录。

二、设计理论总结

1、gm/id与Vov比较

Vov和gm/id都是能反映晶体管偏置点信息的量。那么,两种方法有何不同呢?

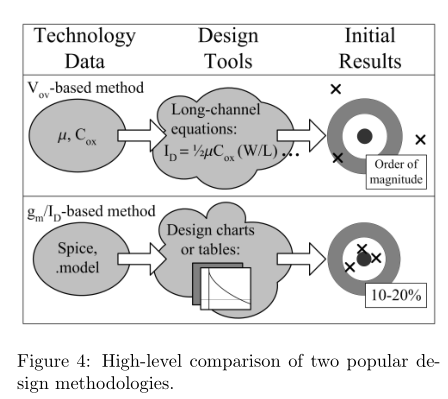

采用基于Vov的设计策略时,隐含地接受了长沟道模型的有效性。但是,使这个模型如此简洁的大多数假设对于当今的小尺寸几何结构而言,几乎是不成立的。因此,基于Vov的方法使得设计出来的电路偏离我们的预期太多太多。

基于gm/id的设计,不依赖长沟道模型的有效性。事实上,它除了仿真之外,不依赖任何东西的有效性。这种方法基于查找表。其基本理念是,支配 MOSFET 的方程非常复杂,我们必须舍弃它们,转而使用一些表格或图表。由于这些图表是使用 Spice 中的器件仿真生成的,所以比长沟道模型要准确得多。

Vov的设计方法步骤:

1、选择一个可用的电路拓扑结构;

2、选择恰当的W和L值;

3、利用仿真工具进行仿真验证;

4、查看设计是否满足所有规格;

5、如果不满足,修改W、L的值,然后返回步骤 3。

有时候,完全不知道往哪个方向调参数,即使最后调出来的参数能满足要求也要迭代很多次而花费太多的时间,变成“spice monkey”。

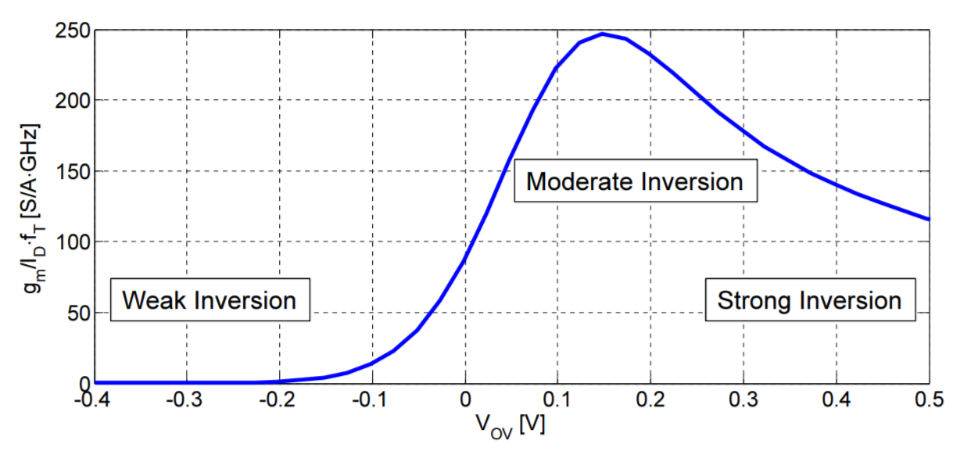

事实上,Vov表示反型程度。例如下图所示,当Vov<0,表示弱反型区;当0<Vov<0.3时,表示中等反型区;当Vov>0.3时,表示强反型区。

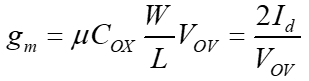

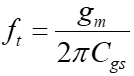

我们知道,关于gm的等式可表示为:

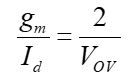

那么,gm/id就可以表示为:

我们可以定义gm/id为跨导效率。跨导效率告诉我们,当投入一定的id,能得到多少gm。这在设计电路时很有用,当功耗一定时,即电流固定,跨导效率高的管子能产生更大的跨导gm。换句话说,增益一定时,若要降低电流(功耗),则要选择高跨导效率的管子。

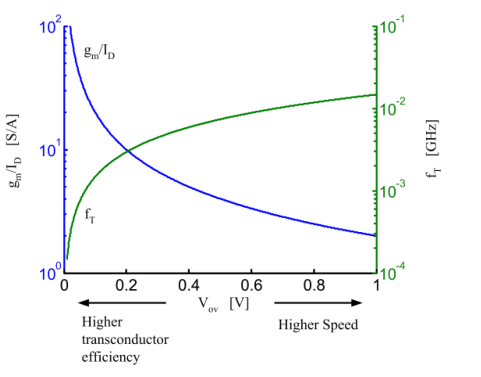

但这同样带来新的问题,若Vov接近零,跨导效率几乎为无穷大,但这显示是不可能的!原因在于晶体管的速度限制了它。晶体管的截止频率为ft:

而Cgs=2/3WLCox,因此截止频率为ft:

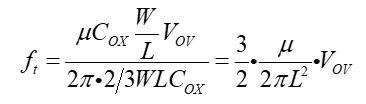

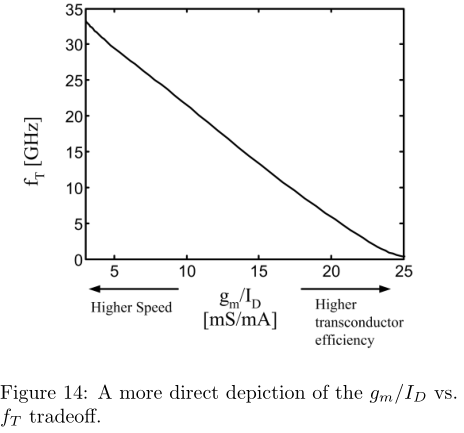

因此,Vov影响着晶体管的速度。很明显gm与ft之间对于Vov的选取是矛盾的,在设计电路是需要折中考虑。如果我们能接受一个速度较慢的设计,那么我们可以使用较低的Vov,这将产生较高的跨导效率(即低功耗);如果电路需要快速运行,我们就必须使用较高的Vov,并接受较低的跨导效率(即高功耗)。

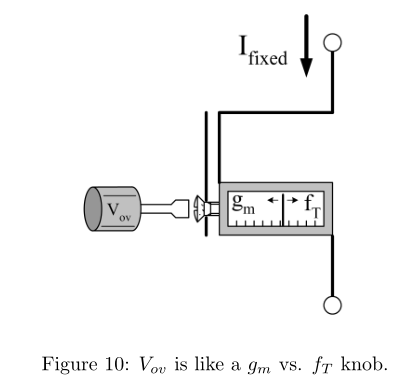

Vov在设计过程中的意义在于,它让我们能够在模拟设计中最需要关注的两个指标(增益和带宽)之间进行权衡。对于固定的电流id,我们可以使用Vov来决定是把电流 “花” 在提高gm(以获得更高的增益)上,还是花在提高ft(以获得更大的带宽)上。

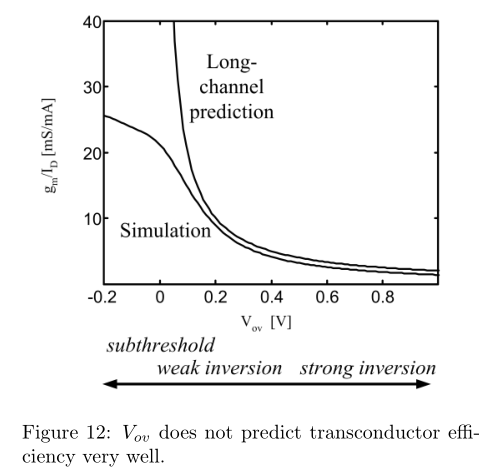

那么,ov设计的局限性在哪?我们从下图可以看出,长沟道模型在理论上,Vov与gm/id是反比关系,但是实际得到的仿真数据与理论值在低Vov值时偏离太大。

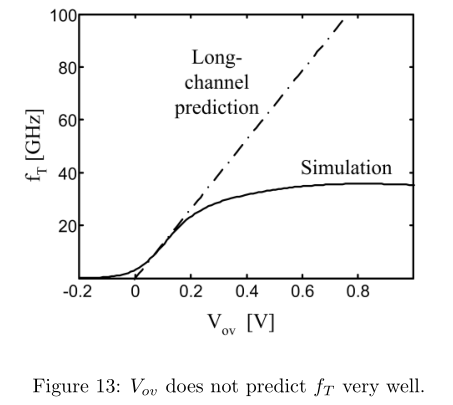

对于ft而言, 理论值与仿真值在大Vov存在大的偏差。

此外,还有一个问题。上面两个图中都显示,Vov在小于0时,仍存在工作点。而长沟道模型预测在Vov小于0时,晶体管关断,电流为0。事实上,Vov<0的工作区域为亚阈值区,在区域在低功耗设计中显得尤为重要。从图中可以看出,在亚阈值区域,工作速度较慢(ft很低)。事实上,论文中提到,在较新的技术中,它们并没有那么慢。实际上,它们通常比我们需要的速度快得多,这使得设计者可以用一部分速度来换取低功耗(对应大的跨导效率)。

因此,我们可以换一个偏置量,也就是gm/id,来简单概括上面两个重要的信息(gm/id和ft)。最简单的就是直接绘制fT与gm/id的关系图,将中间量“Vov”省去,一个图就包含两种重要设计信息。

甚至于,除了防止晶体管工作在线性区,我们根本不用考虑管子是工作在亚阈值区还是在反型区,都能用gm/id这个量去设计对应的指标。

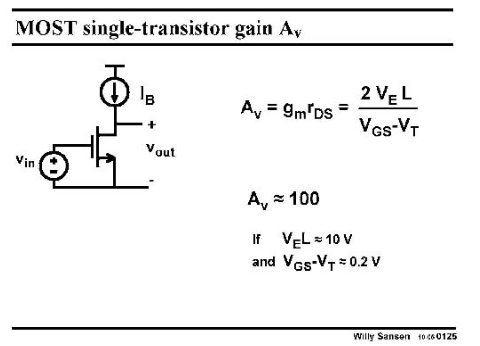

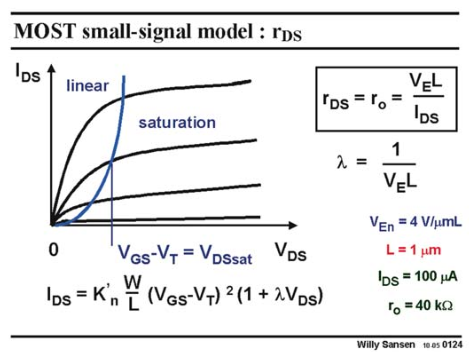

对于本征增益,Sansen在书中表示为:

其中,VE为Early Voltage,是个与工艺相关的参数:

因此,本征增益Av与L成正比,与Vov成反比。在设计放大器时,对于增益的需求,如何判断该工艺下需要选择何种结构才能实现呢?需要单晶体管型还是需要增益提升型?通常的做法是观察晶体管的本征增益,从而判断所需要的结构。

2、 gm/id设计步骤

1)选择有用的电路结构;

2)根据spec确定gm/id值和L;

3)根据gm与gm/id确定电流值id;

4)根据id与id/w值确定w值;

5)手动微调参数以满足spec;

二、gm/id的晶体管仿真

采用TSMC65nm工艺,管子选择nch_25和pch_25。本文以nmos晶体管为例详细详解仿真思路和过程,pmos晶体管的仿真过程与nmos一样,只是仿真电路的设置稍微有所区别。

1、仿真过程

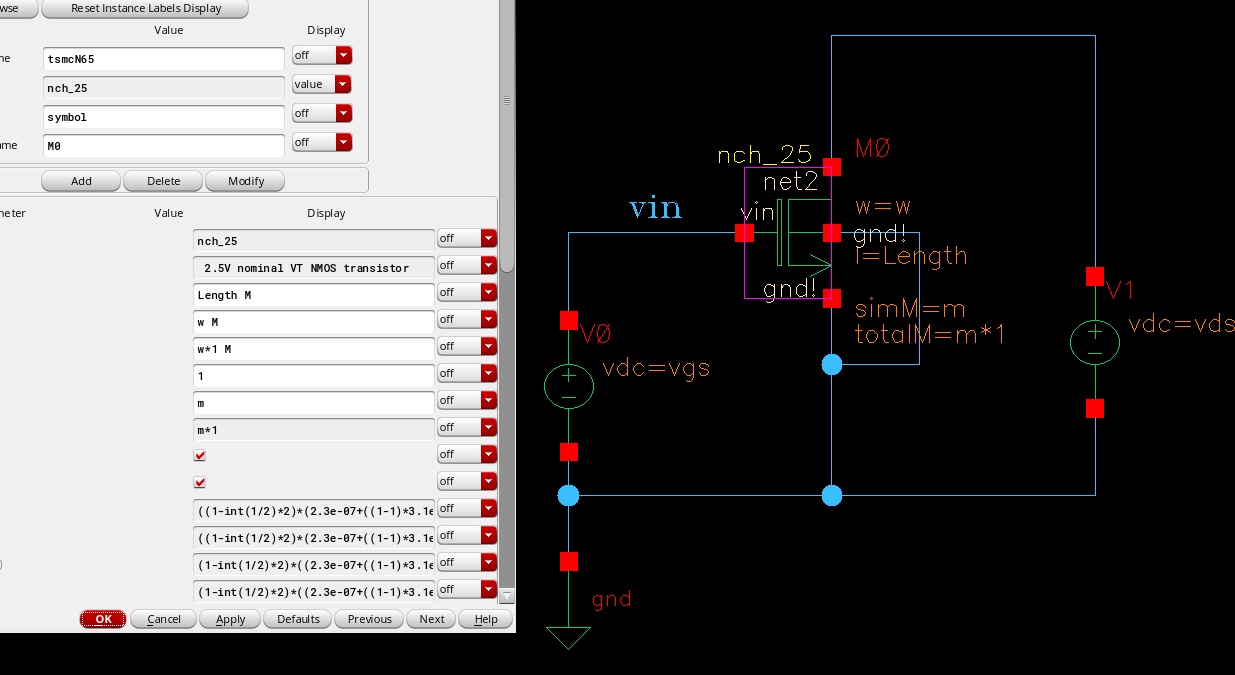

nmos的gm/id仿真示意图如下,其中栅源电压设置为vgs,漏源电源设置为vds=Vdd/2。将nmos管的L设置为length,w设置为w,multiplier设置为m。

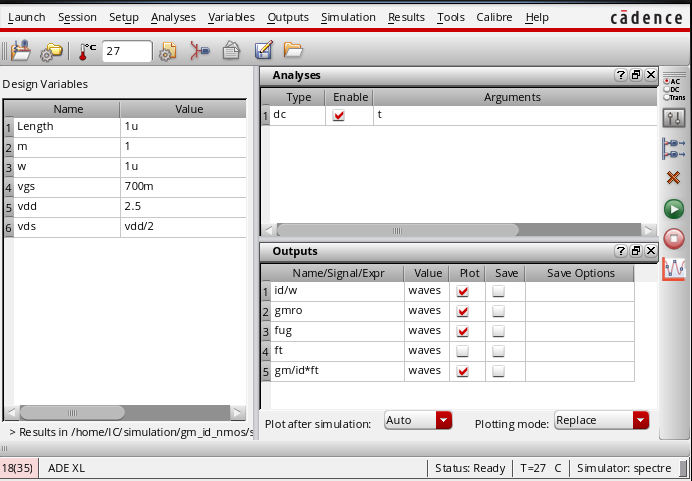

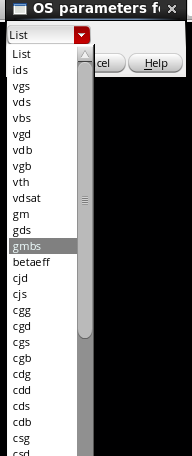

仿真环境选择ADE L,设置参数如图所示,并选择dc仿真保存工作点,点击netlist and run。(必须进行这一步,否则后面点击os没有参数)

在ADE中依次点击Tools-->Calculator-->os,将我们需要的参数:跨导gm,漏极电流id,本征增益selfgain,本征频率ft等参数送入Calculator中。

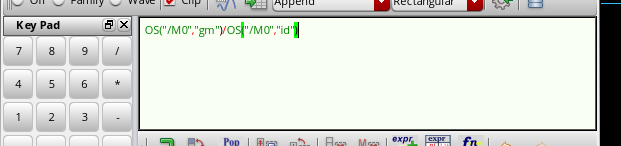

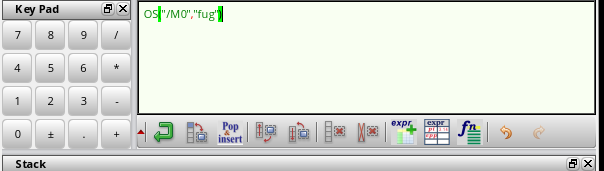

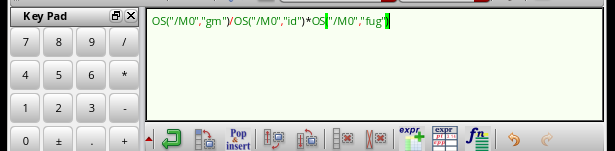

我们需要以gm/id为横坐标,因此按照要求将gm/id表达出来,如图所示。点击enter送入到stack中。此外,os参数中的gmoverid也代表gm/id,两种方式皆可。

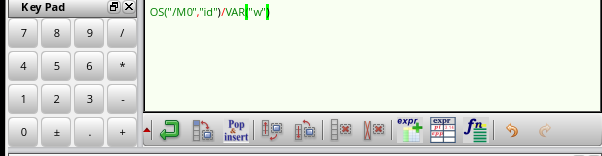

接着将id送入进来,然后除以参数w。这里需要用VAR("w")表示我们自己设置的宽度参数w,同样点击enter送入到stack中。

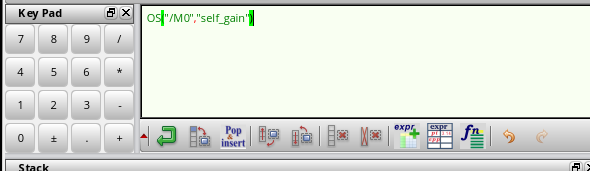

然后是本征增益gmro,点击os发现该工艺下有参数selfgain(有些工艺并没有),从名字可以看出表示“本身的增益”,或者叫“本征增益”。如果其他工艺没有这个参数,需要自己用gm/gds来表示本征增益。即:

OS("/M0","gm")/OS("/M0","gds")

再将本征频率fug送入进来,或者也可以用ft=gm/(2pi*Cgs)来表示。

最后设计电路时往往需要在带宽和增益之间折中,于是用gm/id*ft表示此“品质因数”。

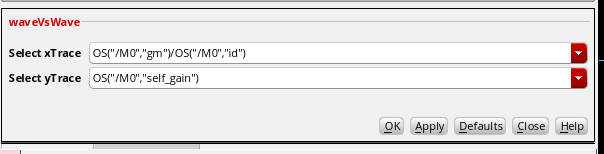

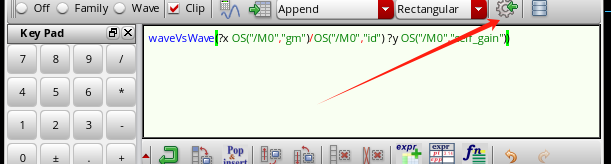

到此,所有的参数都表达完毕。利用waveVswave函数依次将gmro-gm/id,id/w-gm/id,ft-gm/id,gm/id*ft-gm/id表示出来,并点击齿轮符号将表达式送到ADE L中的输出中。

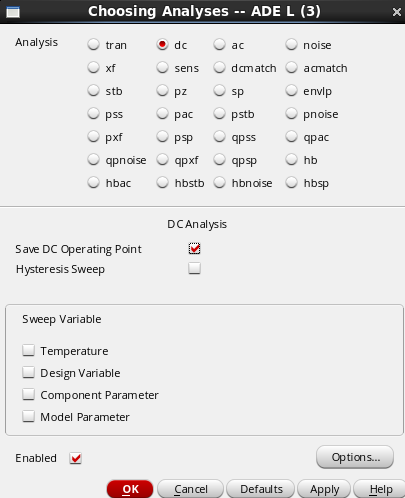

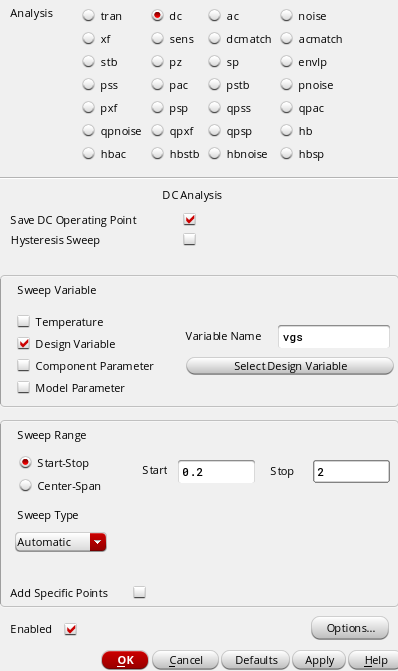

改变dc仿真设置,选择Sweep Variable中的Design Variable,选择vgs,扫描范围为0.2到2之间,点击ok,如图所示。

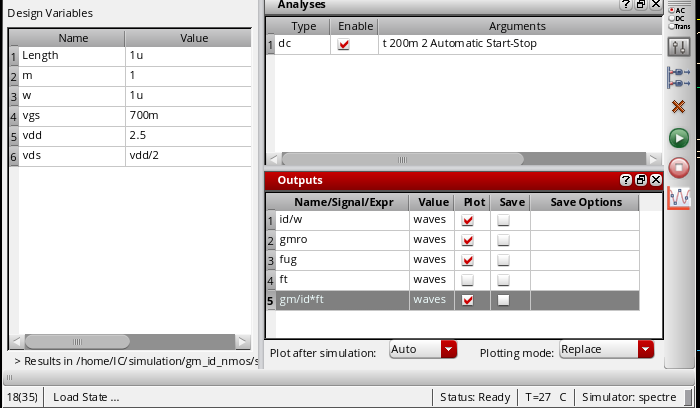

现在ADE L设置如图所示:

可将送入outputs中的表达式重新命名,这样方便查看,如上图所示。

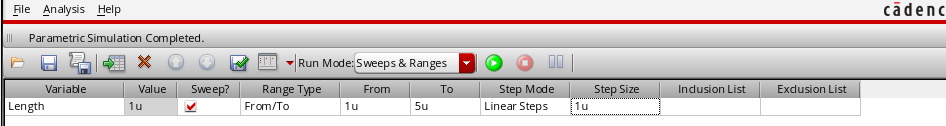

选择ADE-->Tools-->Parametric Analysis,选择参数Length,扫描范围为1u到5u,点击run。

2、仿真结果

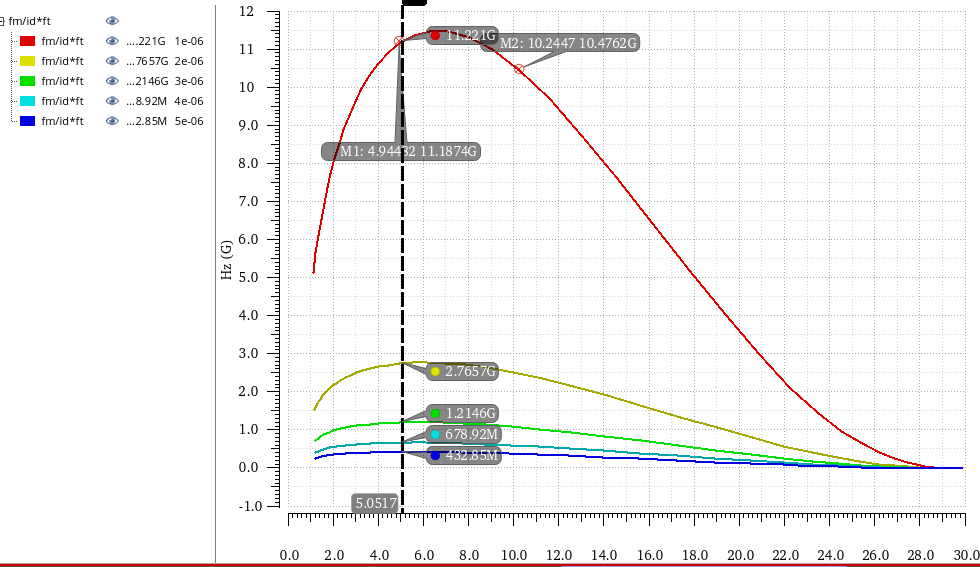

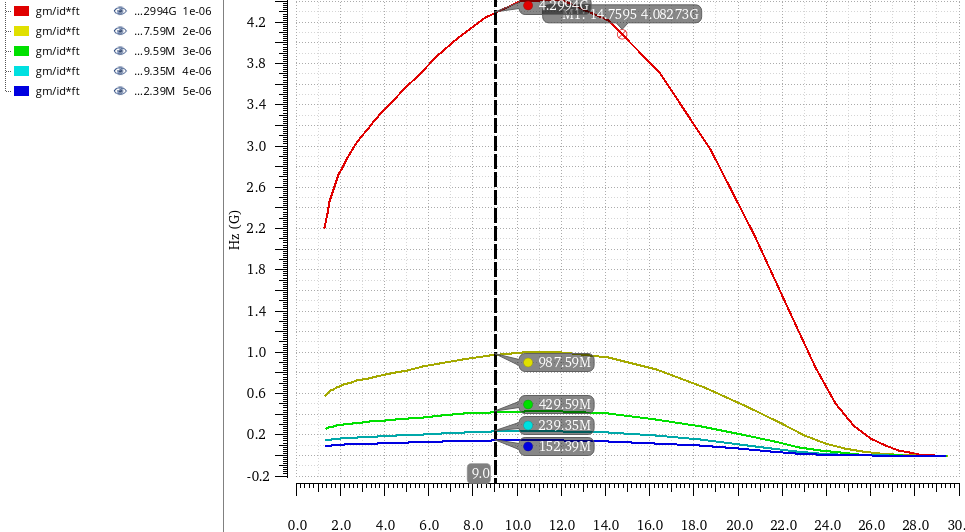

(1)gm/id*ft

从图中看出,nmos管子的gm/id值最好在5~10之间。

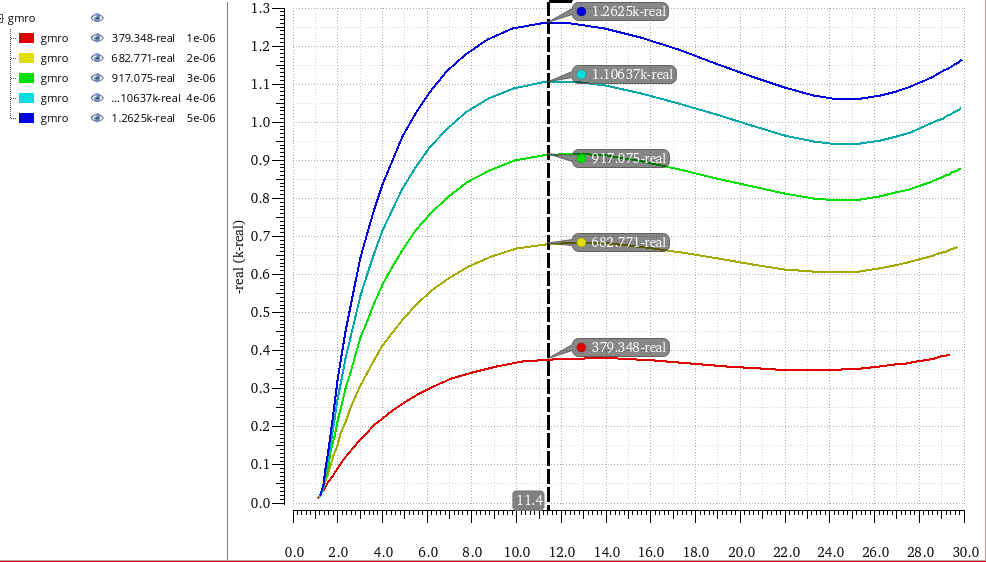

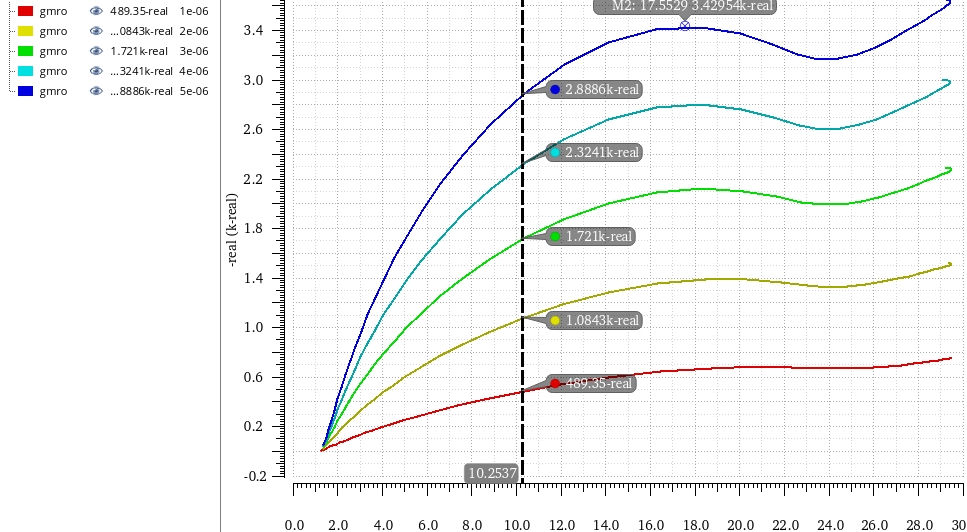

(2)gmro

从图中可以看出,在相同的gm/id处,随着L增大,本征增益增大。当gm/id=10,L=1um时,本征增益大约为370,本征增益较大。

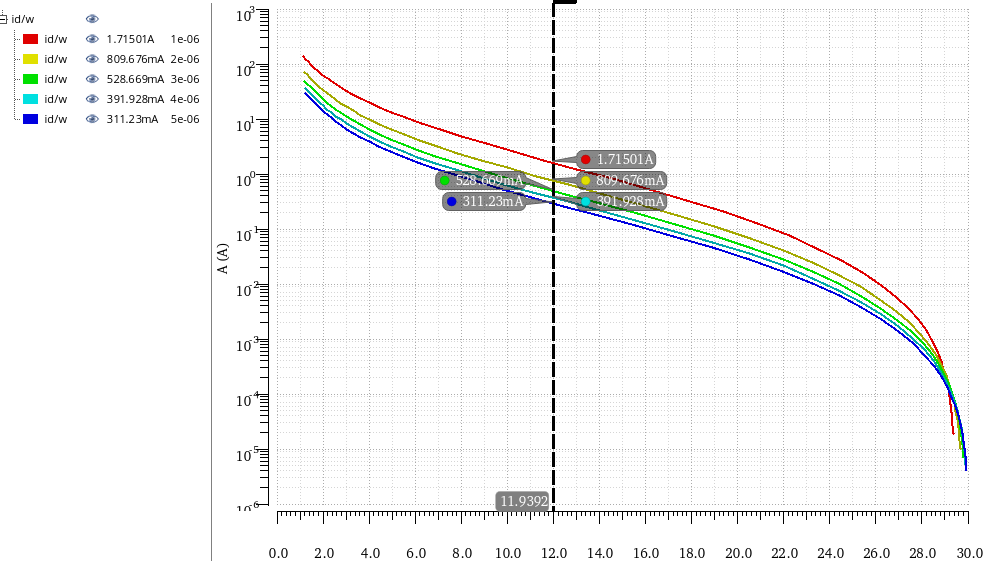

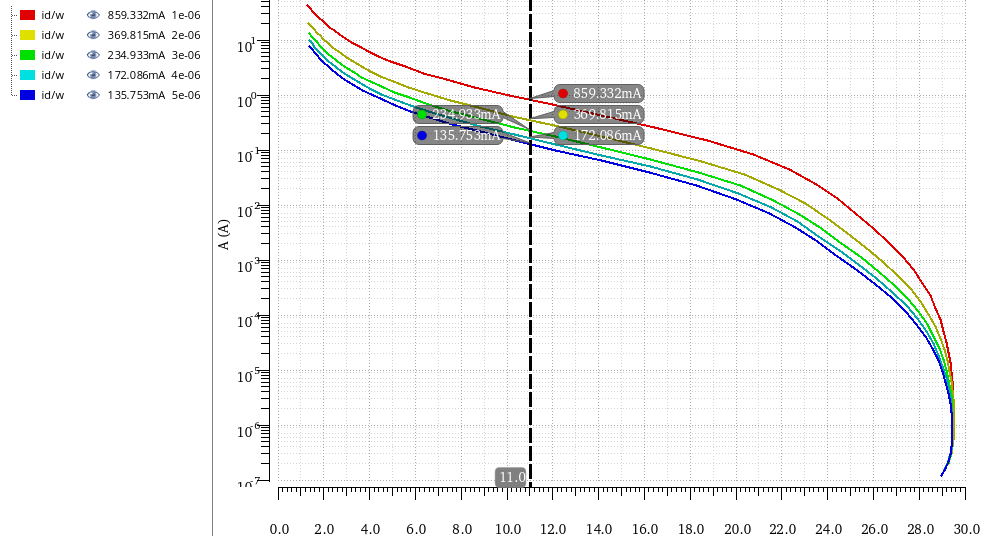

(3)id/w

右键点击纵轴,选择Log Scale,方便查看结果。下图同理。

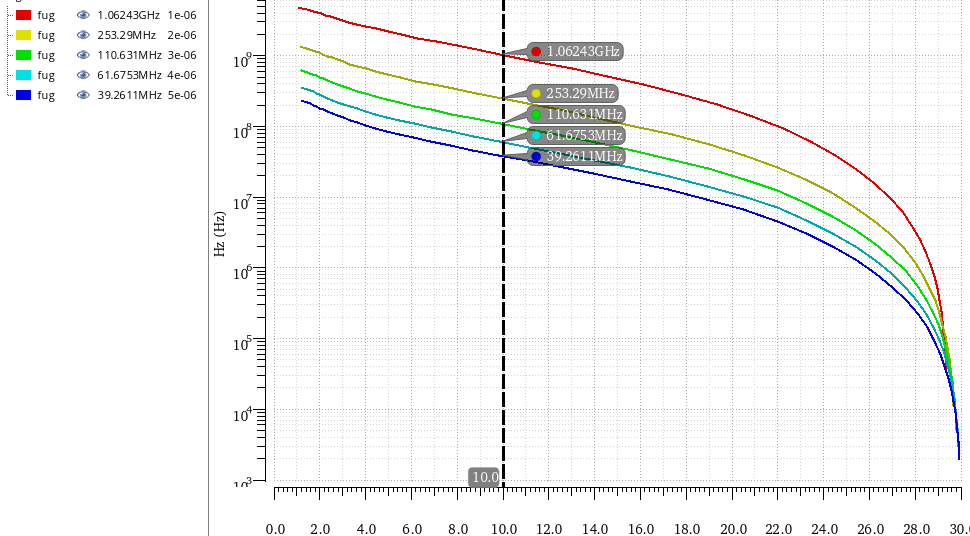

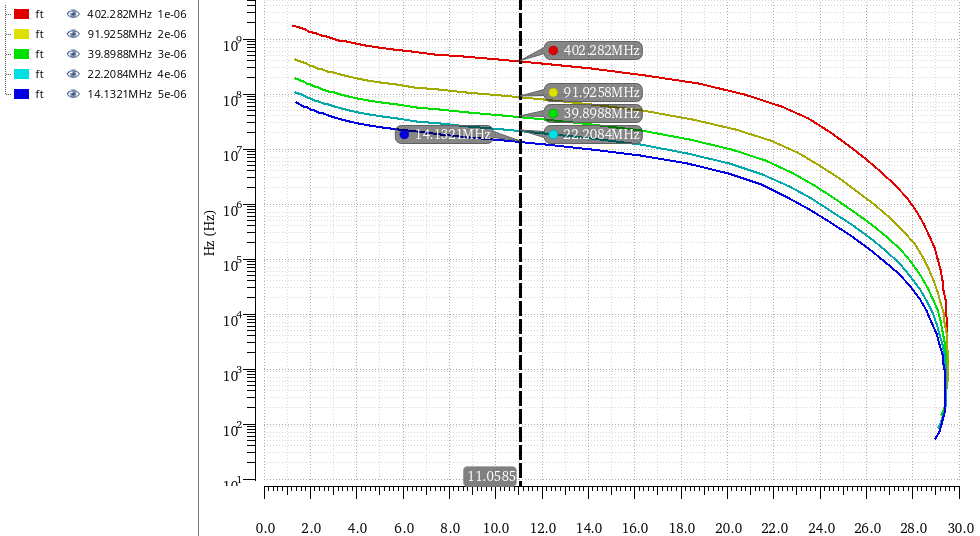

(4)ft

从图中看出,本征频率与L成反比,且随着Vgs-vth的下降而增大。

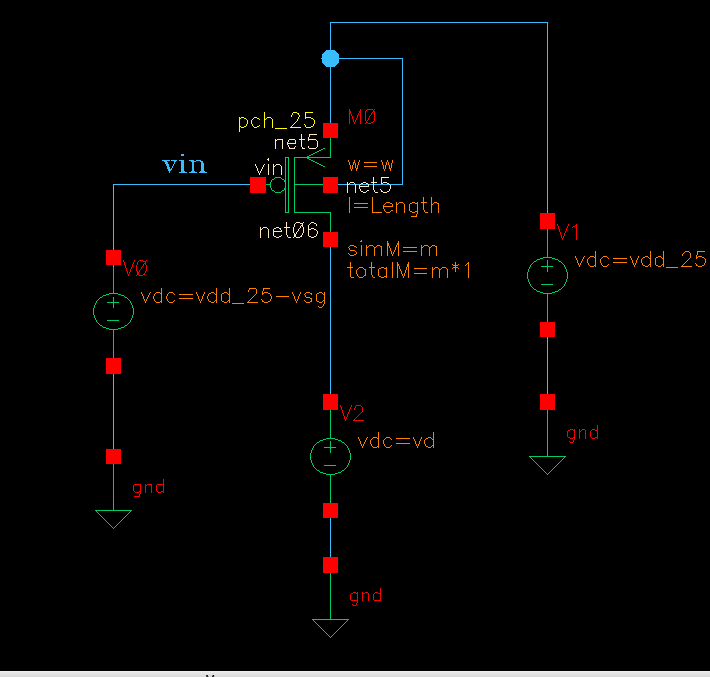

pmos仿真设置与nmos一样,只不过电压偏置因管子类型不同而有所变化,如图所示。

仿真过程与nmos一样,这里略过,直接看结果。

(1)gm/id*ft

从图中看出,pmos管子的gm/id值最好在8~14之间。

(2)gmro

从图中可以看出,在相同的gm/id处,随着L增大,本征增益增大。当m/id=10且L=1um时,本征增益大约为478,本征增益较大。

(3)id/w

(4)ft

从图中看出,本征频率与L成反比,且随着Vgs-vth的下降而增大。

最后,将ADE L保存,将仿真结果保存,方便后续查看。

1179

1179

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?