⏰诗赋清音:云生高巅梦远游, 星光点缀碧海愁。 山川深邃情难晤, 剑气凌云志自修。

概述

华中科大计算机学院最受欢迎的实践课,大萝卜老师将带领大家硬件吃鸡通关,从逻辑门开始一步步构造你自己的 CPU 。

实验传送门:

《计算机硬件系统设计》---自己动手画CPU(计算机组成原理实验) (educoder.net)

配套慕课:计算机硬件系统设计_华中科技大学_中国大学MOOC(慕课)

已解决全套源码下载:关注公众号【科创视野】回复 头歌计组

目录

🌷1. 闯关目的

🌼第1关:8位可控加减法电路设计

(1) 掌握一位全加器的实现逻辑和多位可控加减法电路的实现逻辑;

(2) 熟悉 Logisim 平台基本功能,能在 logisim 中实现多位可控加减法电路。

🌼第2关:CLA182四位先行进位电路设计

(1) 掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路;

(2) 利用设计的4位先行进位电路构造4位快速加法器,分析对应电路的时间延迟。

🌼第3关:4位快速加法器设计

(1) 掌握快速加法器中先行进位的原理,能利用相关知识设计4位先行进位电路;

(2) 利用设计的4位先行进位电路构造4位快速加法器,分析对应电路的时间延迟。

🌼第4关:16位快速加法器设计

(1) 理解成组进位产生函数,成组进位传递函数的概念,熟悉 Logisim 平台子电路的概念;

(2) 利用前述实验封装好的4位先行进位子电路以及4位快速加法器子电路构建16位、32位、64位快速加法器,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。

🌼第5关:32位快速加法器设计

(1) 理解成组进位产生函数,成组进位传递函数的概念,熟悉 Logisim 平台子电路的概念;

(2) 利用前述实验封装好的4位先行进位子电路以及4位快速加法器子电路构建16位、32位、64位快速加法器,并能利用相关知识分析对应电路的时间延迟,理解电路并行的概念。

🌼第6关:5位无符号阵列乘法器设计

(1) 掌握阵列乘法器的实现原理;

(2) 分析5位阵列乘法器的性能,能在 Logisim 中绘制阵列乘法器电路。

🌼第7关:6位有符号补码阵列乘法器

(1) 掌握补码阵列乘法器的实现原理;

(2) 分析6位阵列乘法器的性能,能在 Logisim 中绘制阵列乘法器电路。

🌼第8关:乘法流水线设计

(1) 掌握运算流水线基本概念,理解将复杂运算步骤细分成子过程的思想;

(2) 实现简单的乘法运算流水线。

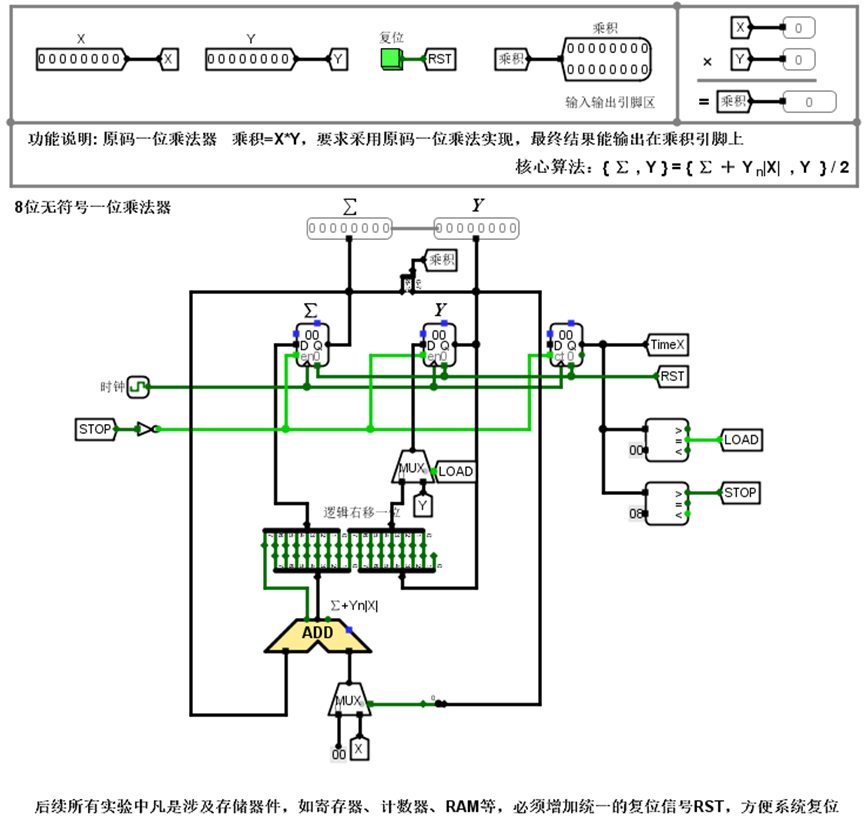

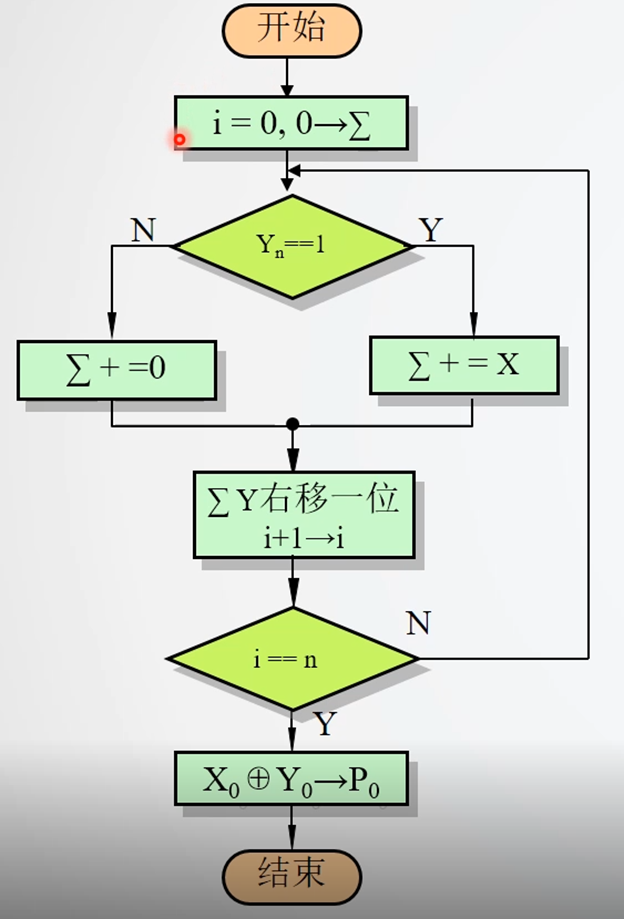

🌼第9关:原码一位乘法器设计

(1) 掌握原码一位乘法运算的基本原理;

(2) 熟练掌握 Logisim 寄存器电路的使用,能在 Logisim 平台中设计实现一个 8*8位的无符号数乘法器。

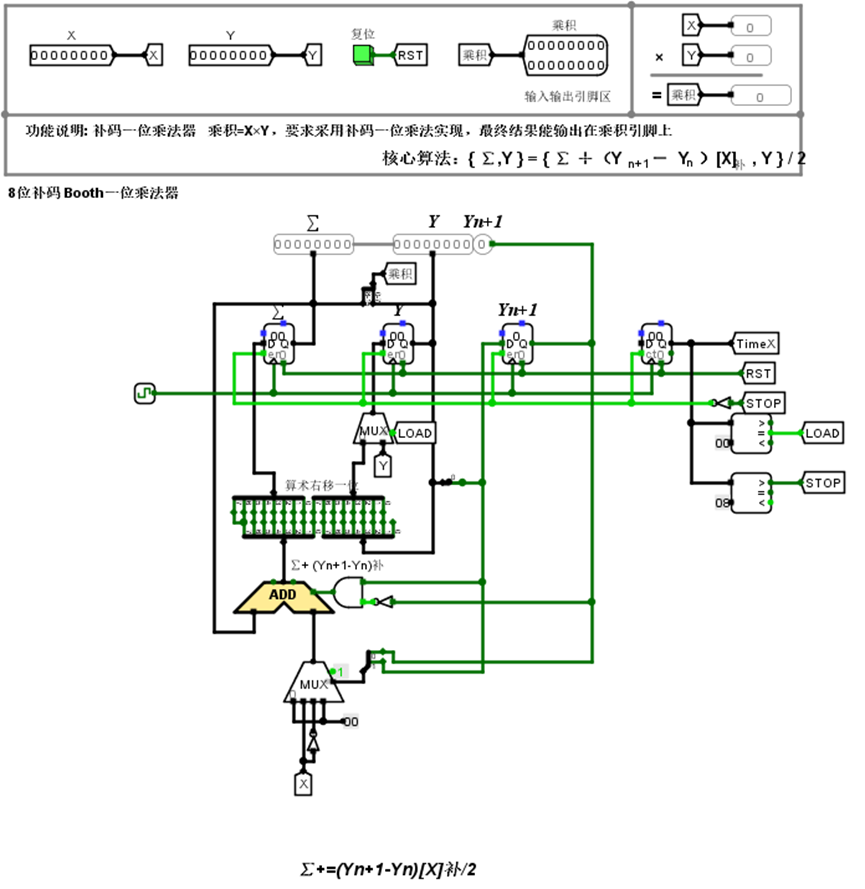

🌼第10关:补码一位乘法器设计

(1) 掌握补码一位乘法运算的基本原理;

(2) 熟练掌握 Logisim 寄存器电路的使用,能在 Logisim 平台中设计实现一个8*8 位的补码 Booth一位乘法器。

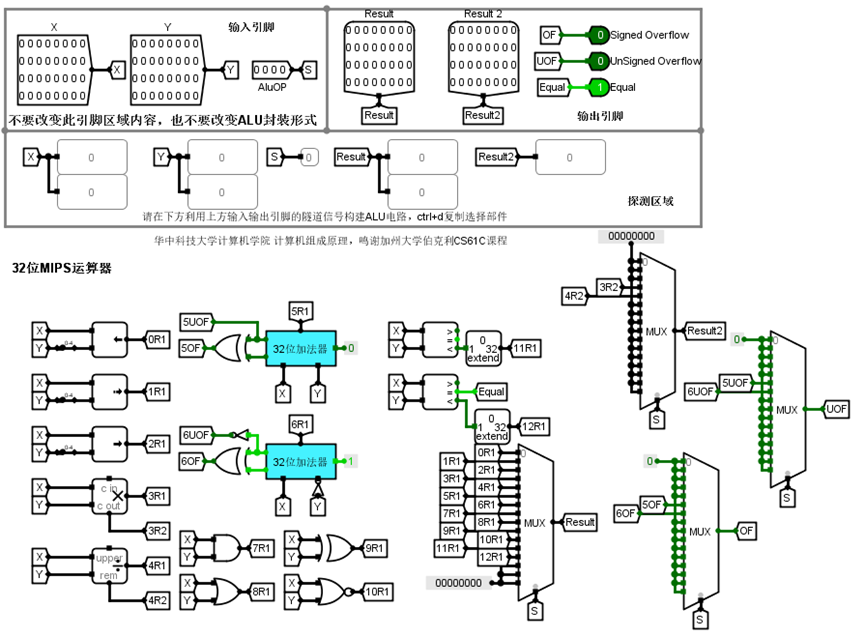

🌼第11关:MIPS运算器设计

(1) 理解算术逻辑运算单元(ALU)的基本构成,掌握 Logisim 中各种运算组件的使用方法;

(2) 熟悉多路选择器的使用,能利用前述实验完成的32位加法器、 Logisim 中的运算组件构造指定规格的 ALU 单元。

🌷2. 闯关内容

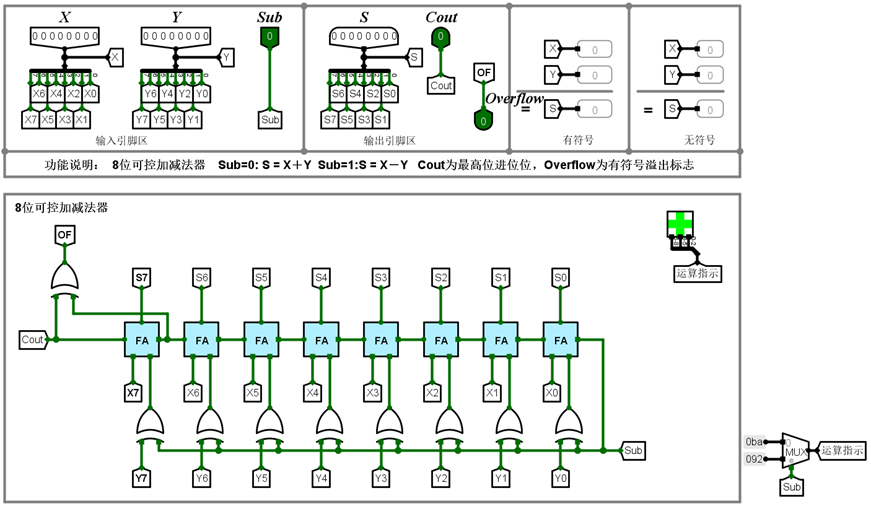

🌼第1关:8位可控加减法电路设计

在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,用户可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF 为有符号运算溢出位。

🌼第2关:CLA182四位先行进位电路设计

在 Logisim 中打开 alu.circ 文件,在对应子电路中实现可级联的4位先行进位电路。其中 Gi,Pi 为进位生成函数和传递函数,Cin 为进位输入,C1~C4 为进位输出,G,P 为成组进位生成函数和成组进位传递函数。

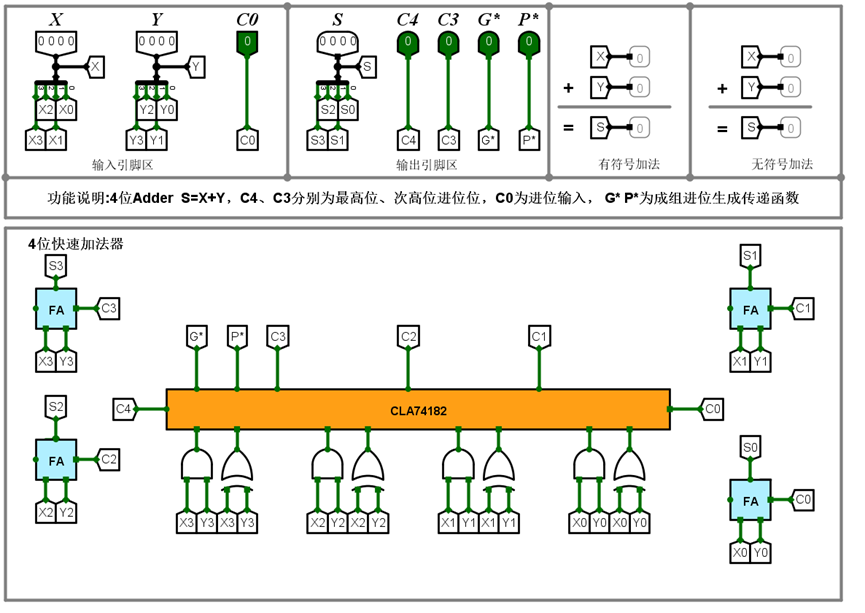

🌼第3关:4位快速加法器设计

利用前一步设计好的四位先行进位电路构造四位快速加法器,其中 X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。

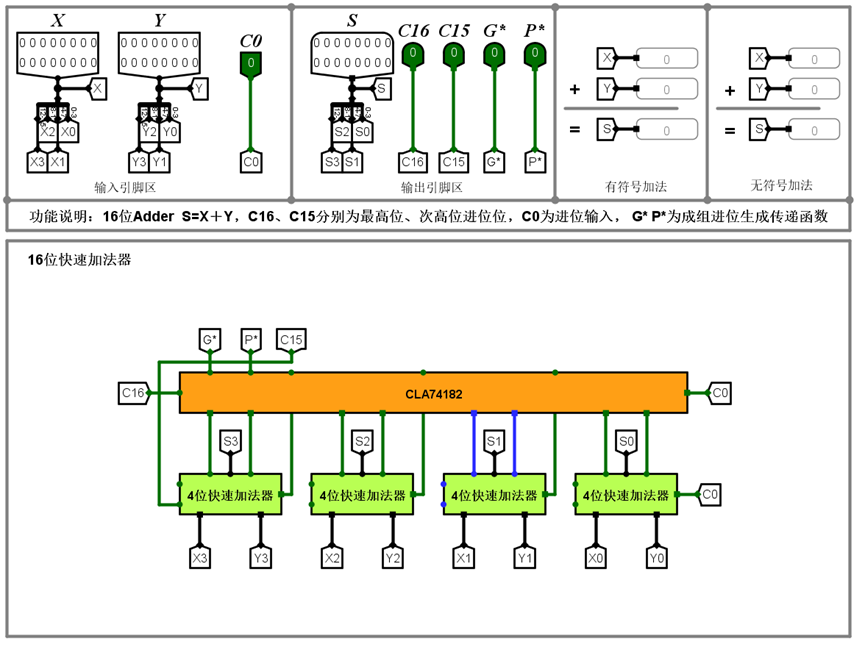

🌼第4关:16位快速加法器设计

在 Logisim 中打开 alu.circ 文件,在对应的子电路中利用四位先行进位电路和四位快速加法器构造十六位组间先行进位,组内先行进位快速加法器,并验证其功能是否正常。其中 X,Y 为16位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为16位成组进位生成函数和成组进位传递函数。

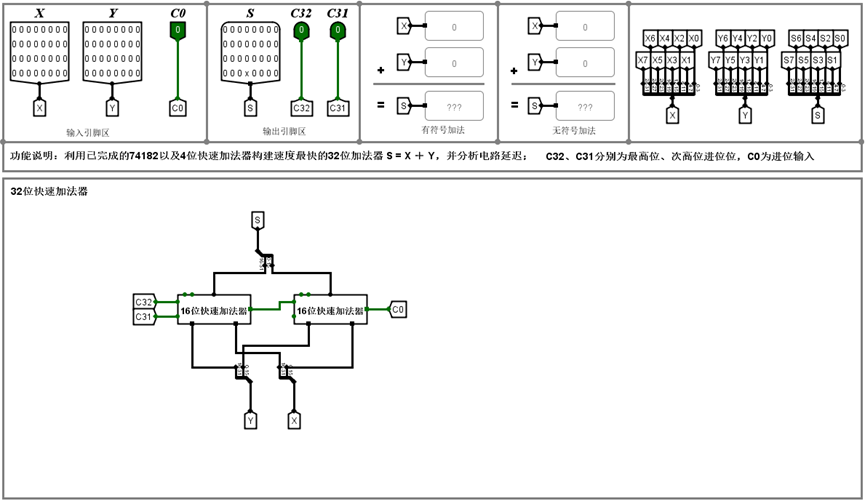

🌼第5关:32位快速加法器设计

利用16位快速加法器以及先行进位电路构建32位快速加法器,并探讨其时间延迟。可能方案:

(1)2个16位加法器直接串联,C16 信号采用下层的进位输出;

(2)2个16位加法器直接串联,C16 进位输入采用上层的进位输出;

(3)在16位快速加法器的基础上再增加一级组间先行进位电路,类似64位快速加法器的方法;分别分析3种不同方案可能的总延迟,选择速度最快的方案实现32位快速加法器,并分析其时间延迟。其中 X,Y 为32位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,Overflow 为有符号加法运算溢出信号。

🌼第6关:5位无符号阵列乘法器设计

在 Logisim 中打开 alu.circ 文件,在5位阵列乘法器中实现斜向进位的阵列乘法器,其中 X,Y 为5位被乘数和乘数,P 为乘积输出,阵列乘法所需的25按位与的乘积项已经通过辅助电路生成,所有乘积项均通过隧道标签给出,用户只需要在已给出的电路框架中进行简单连线即可完成5位阵列乘法器。

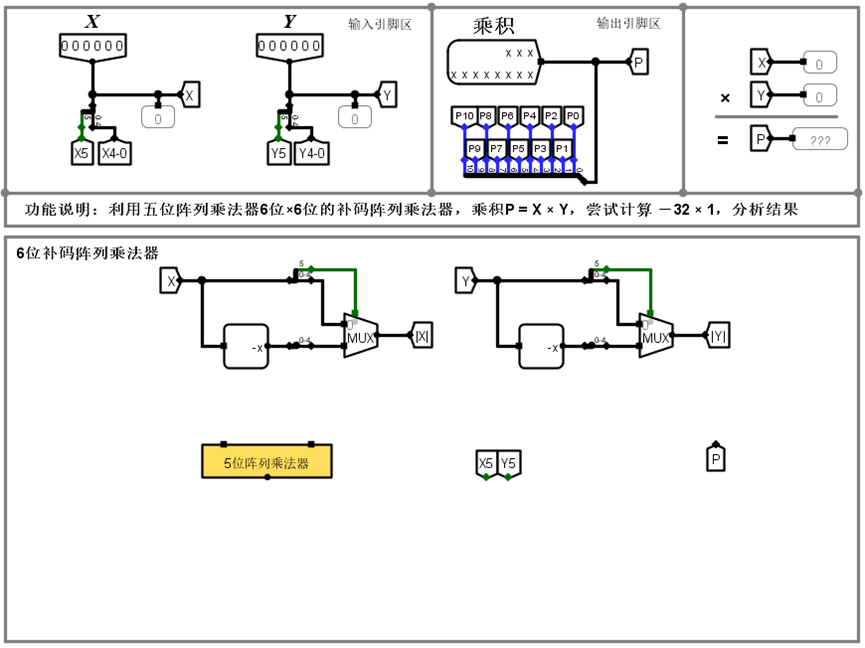

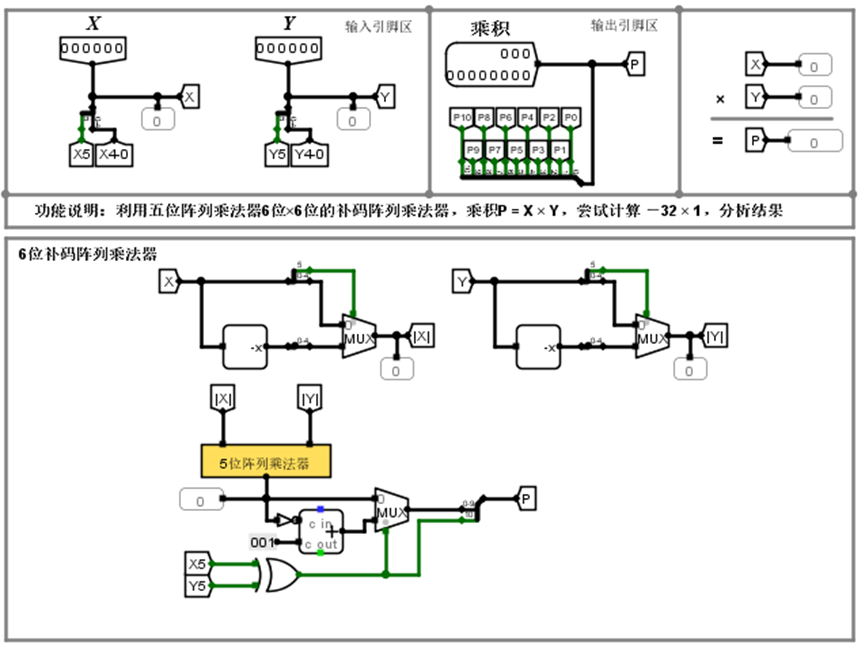

🌼第7关:6位有符号补码阵列乘法器

在 Logisim 中打开 alu.circ 文件,在6位补码阵列乘法器中利用5位阵列乘法器以及求补器等部件实现补码阵列乘法器,实验框架如图2-1所示:

图2-1

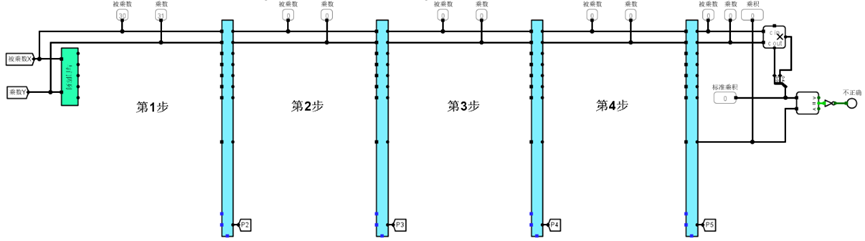

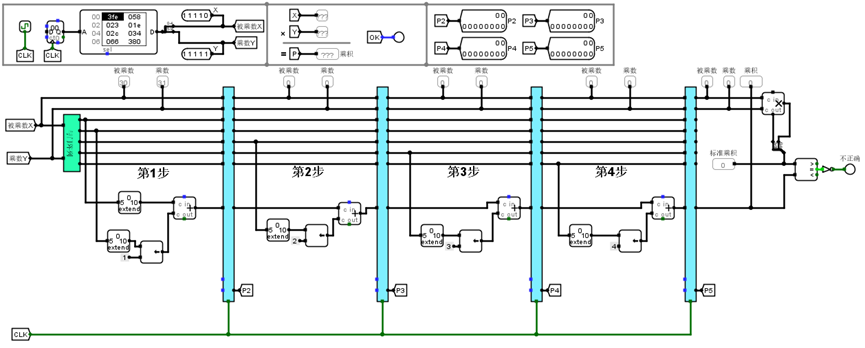

🌼第8关:乘法流水线设计

在 Logisim 中打开 alu.circ 文件,在6位补码阵列乘法器中利用5位阵列乘法器以及求补器等部件实现补码阵列乘法器,实验框架如图2-2所示:

图2-2

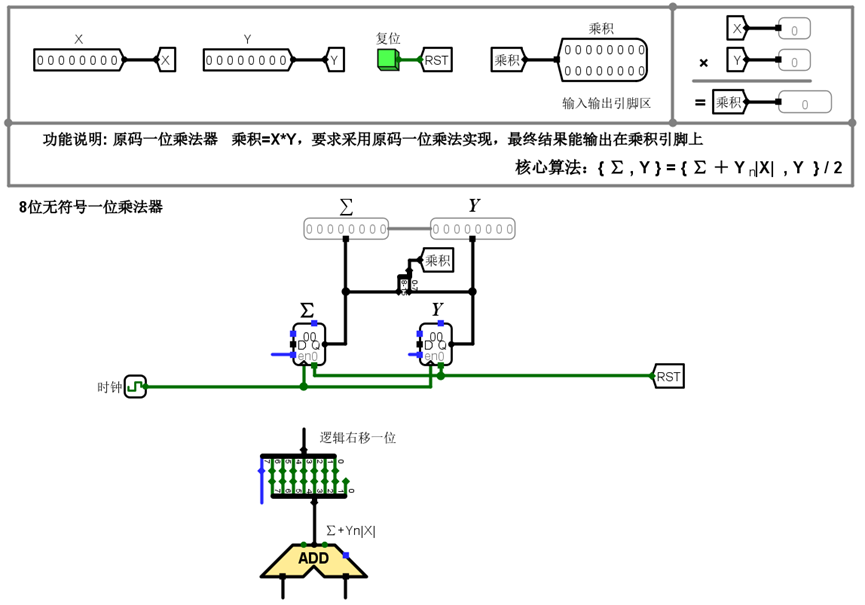

🌼第9关:原码一位乘法器设计

在 alu.circ 文件中的原码一位乘法器子电路中,增加控制电路和数据通路,使得该电路能自动完成8位无符号数的一位乘法运算。再设置引脚初始值,然后驱动时钟自动仿真,电路可自动完成运算。运算结束,结果传输到输出引脚。运算结束时,实验框架如图2-3所示:

图2-3

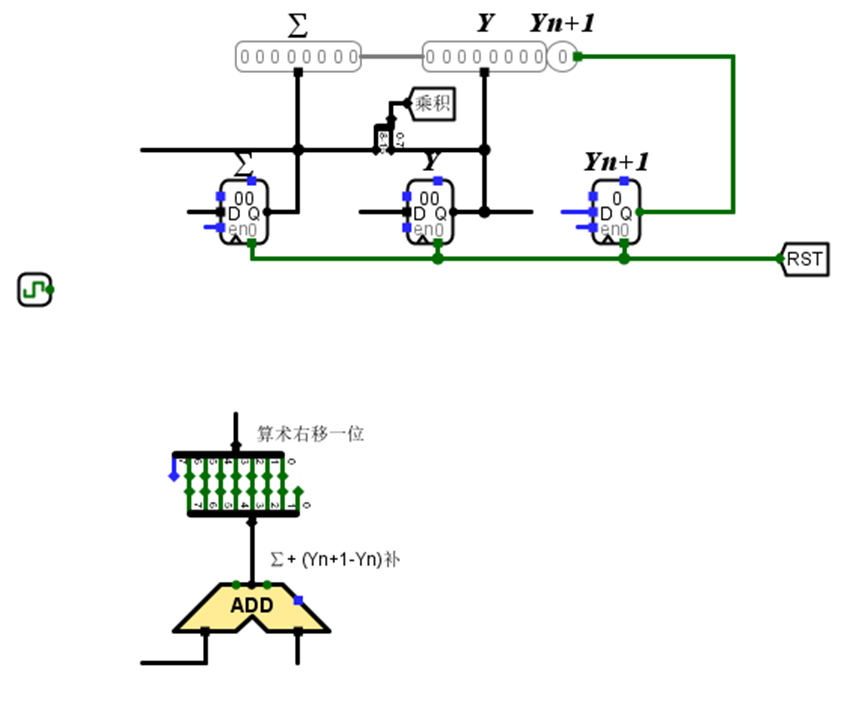

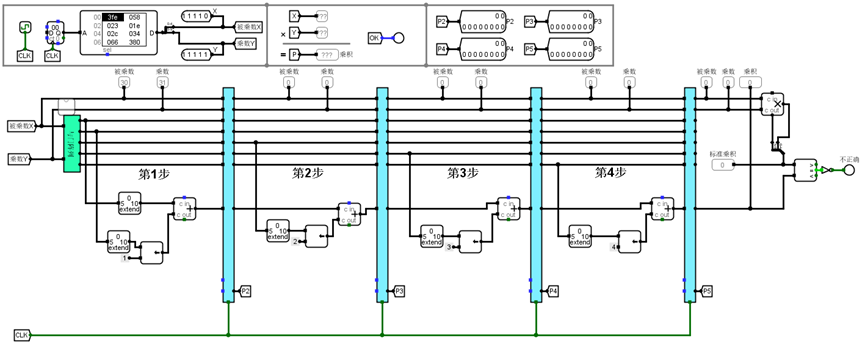

🌼第10关:补码一位乘法器设计

在 alu.circ 文件中的补码一位乘法器子电路中,增加控制电路和数据通路,使得该电路能自动完成8位补码一位乘法运算。再设置引脚初始值,然后驱动时钟自动仿真,电路可自动完成运算。运算结束,结果传输到输出引脚。运算结束时,电路应该自动停止,实验框架如图2-4所示:

图2-4

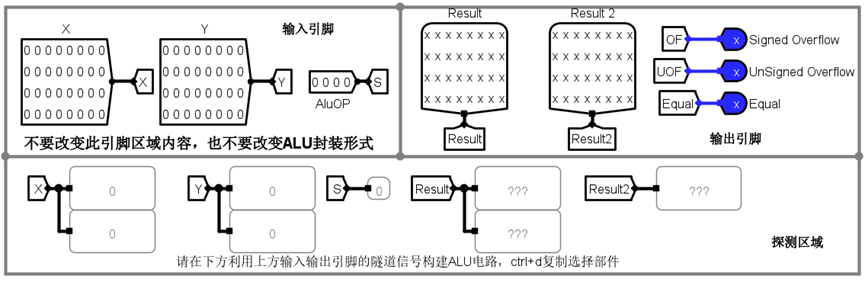

🌼第11关:MIPS运算器设计

利用前面实验封装好的32位加法器以及 Logisim 平台中现有运算部件,构建一个32位算术逻辑运算单元(禁用 Logisim 系统自带的加法器,减法器),可支持算术加、减、乘、除,逻辑与、或、非、异或运算、逻辑左移、逻辑右移、算术右移运算,支持常用程序状态标志(有符号溢出 OF 、无符号溢出 UOF ,结果相等 Equal ),ALU 功能以及输入输出引脚见后表,在主电路中详细测试自己封装的 ALU ,并分析该运算器的优缺点,实验框架如图2-所示:

图2-5

🌷3. 闯关步骤

🌼第1关:8位可控加减法电路设计

图2-6

🌼第2关:CLA182四位先行进位电路设计

图2-7

🌼第3关:4位快速加法器设计

图2-8

🌼第4关:16位快速加法器设计

图2-9

🌼第5关:32位快速加法器设计

图2-10

🌼第6关:5位无符号阵列乘法器设计

图2-11

🌼第7关:6位有符号补码阵列乘法器

图2-12

🌼第8关:乘法流水线设计

图2-13

🌼第9关:原码一位乘法器设计

图2-14

🌼第10关:补码一位乘法器设计

图2-15

🌼第11关:MIPS运算器设计

图2-16

🌷4. 闯关总结

🌼第1关:8位可控加减法电路设计

1. 并行加法器:进位输出仅与最低位进位输入C0有关(Cn=Gn+PnGn-1+PnPn-1Gn-2+PnPn-1Pn-2Gn-3 …+PnPn-1…P1C0),而不是依赖于低位进位(Cn= Gn + Pn Cn-1)。

2. 硬件实现:可控反相异或门。配合异或门,Sub通过置0置1,既能实现Y和非Y,同时还能作为Cin的0、1信号输入;OF为溢出标志位,溢出输出1(这里1为高电平)。判断有符号数加减运算是否溢出的硬件实现:最高有效位的进位⊕符号位的进位,1表示溢出。

🌼第2关:CLA182四位先行进位电路设计

实验原理:在 Logisim 模拟器中打开 alu.circ 文件,在对应子电路中利用已经封装好的全加器设计8位串行可控加减法电路,可以直接使用在电路中使用对应的隧道标签,其中 X,Y 为两输入数,Sub 为加减控制信号,S 为运算结果输出,Cout 为进位输出,OF为有符号运算溢出。

🌼第3关:4位快速加法器设计

解题思路:利用第2关设计好的四位先行进位电路构造四位快速加法器, X,Y 为四位相加数,Cin 为进位输入,S 为和数输出,Cout 为进位输出,G,P 为 4 位成组进位生成函数和成组进位传递函数。

🌼第4关:16位快速加法器设计

1. 全加器的原理:全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.

2. 实验原理:将4个四位全加器对两个多位二进制数进行加法运算,同时产生进位。当两个二进制数相加时,较高位相加时必须加入较低位的进位项。

🌼第5关:32位快速加法器设计

实验原理:将2个16位全加器对两个多位二进制数进行加法运算,同时产生进位。当两个二进制数相加时,较高位相加时必须加入较低位的进位项。

🌼第6关:5位无符号阵列乘法器设计

实验原理:数字逻辑是现场可编程门阵列,它在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点,用乘数的每一位去乘被乘数,然后将每一位权值直接去乘被乘数得到部分积,并按位列为一行每一行部分积末位与对应的乘数数位对齐,体现对应数位的权值,将各次部分积求和得到最终的对应数位的权值。

🌼第7关:6位有符号补码阵列乘法器

实验原理:对于输入的X、Y,若都是正数则把符号位去了,把绝对值输入进5位阵列乘法器。都是负数就先把XY送进求补器,得到的就是X和Y的绝对值,然后输入进5位阵列乘法器。

🌼第8关:乘法流水线设计

此次试验较为简单,其流程如图2-17所示

图2-17

🌼第9关:原码一位乘法器设计

1. 位移次数控制:采用计数器+比较器的硬件实现,控制右移9次即可(题目中有提示),LOAD在=0时,给到1信号;将b送入右侧寄存器中,其他时候都=0就按照位移情况对右侧寄存器开展更新

2. 位移的实现:采用上下四组8位宽分离器实现,左边高位右边低位,乘积右移,最高位有八位加法器的进位输入得到,右移弹出的数据用于数据选择器部署下次是+0还是+a。

🌼第10关:补码一位乘法器设计

1. 选择器进行实现判断Yn+1Yn的数据,从而判断在所求和的基础上加0、[x]补还是[-x]补:选择器的选择输入端为Yn+1Yn,在该选择器的第0和第3位都连接0,而第一位输入对应的是[x]反,在ADD这个加法器中当Yn+1Yn=01时,进位输入为1,此时实现加[-x]补,在选择器的第2位输入的是x。

2. 移位控制:此时得到算数右移,去掉最低位,最高位复制原来的最高位可以采用分线器实现。右移后的16位数据,左边8位为部分积,存入部分积寄存器中;右边八位为右移过来的低位积+y的几位高位数据(低位数据随着时钟驱动后的每次计算,被移出去),存入Y寄存器中。

🌼第11关:MIPS运算器设计

1. 通关设计:利用前面实验封装好的 32 位加法器以及 logisim 平台中现有运算部件构建一个 32 位算术逻辑运算单元,通过多路选择器处理,将加、减、乘、除,逻辑与、或、非、异或运算、逻辑左移、逻辑右移、算术右移分别进行运算并得到结果,通过多路选择器将所选运算方式对应的结果给Result,乘除运算时将高位结果或者余数给Result2,其余情况下Result2结果为0。

2. 使用移位器实现逻辑左移、右移、算数右移运算。

本文是华中科大计算机学院实践课内容,大萝卜老师带领大家从逻辑门构造CPU。介绍了11关运算器设计闯关,包括8位可控加减法电路、CLA182四位先行进位电路等设计,涵盖各关卡目的、内容、步骤及总结,涉及多种电路原理和实现方法。

本文是华中科大计算机学院实践课内容,大萝卜老师带领大家从逻辑门构造CPU。介绍了11关运算器设计闯关,包括8位可控加减法电路、CLA182四位先行进位电路等设计,涵盖各关卡目的、内容、步骤及总结,涉及多种电路原理和实现方法。

866

866

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?