`timescale 1ns/1ns

module huawei8//四位超前进位加法器

(

input wire [3:0]A,

input wire [3:0]B,

output wire [4:0]OUT

);

//*************code***********//

wire [3:0] G;

wire [3:0] P;

wire [3:0] f;

wire [4:1] C;

Add1 u0_Add1(

.a(A[0]),

.b(B[0]),

.C_in(1'b0),

.f(f[0]),

.g(G[0]),

.p(P[0])

);

Add1 u1_Add1(

.a(A[1]),

.b(B[1]),

.C_in(C[1]),

.f(f[1]),

.g(G[1]),

.p(P[1])

);

Add1 u2_Add1(

.a(A[2]),

.b(B[2]),

.C_in(C[2]),

.f(f[2]),

.g(G[2]),

.p(P[2])

);

Add1 u3_Add1(

.a(A[3]),

.b(B[3]),

.C_in(C[3]),

.f(f[3]),

.g(G[3]),

.p(P[3])

);

CLA_4 u_CLA_4(

.P(P),

.G(G),

.C_in(1'b0),

.Ci(C),

.Gm(),

.Pm()

);

assign OUT = {C[4], f};

//*************code***********//

endmodule

//下面是两个子模块

module Add1

(

input a,

input b,

input C_in,

output f,

output g,

output p

);

assign f = a ^ b ^ C_in;

assign g = a & b;

assign p = a | b;

endmodule

module CLA_4(

input [3:0]P,

input [3:0]G,

input C_in,

output [4:1]Ci,

output Gm,

output Pm

);

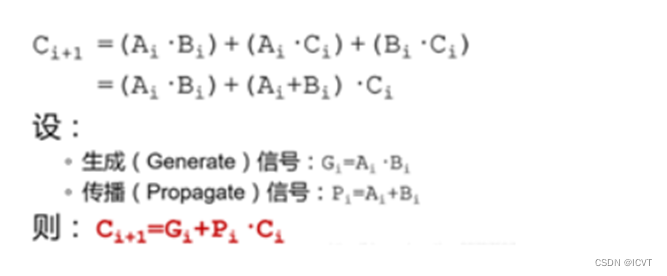

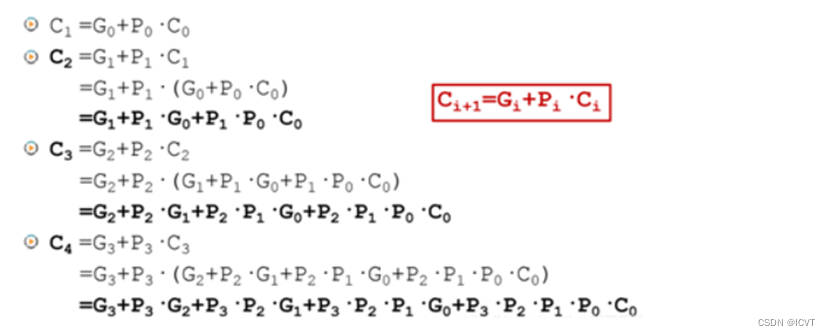

assign Ci[1] = G[0] | (P[0]&C_in);

assign Ci[2] = G[1] | (P[1]&G[0]) | (P[1]&P[0]&C_in);

assign Ci[3] = G[2] | (P[2]&G[1]) | (P[2]&P[1]&G[0]) | (P[2]&P[1]&P[0]&C_in);

assign Ci[4] = G[3] | (P[3]&G[2]) | (P[3]&P[2]&G[1]) | (P[3]&P[2]&P[1]&G[0]) | (P[3]&P[2]&P[1]&P[0]&C_in);

endmodule

610

610

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?