首先下好装有eda工具的虚拟机

准备一个简单的全加器代码full_add.v,一个验证代码tb.v(csdn都是,我就不贴了)

1.终端输入命令:vcs -full64 tb.v full_add.v -l readme.log +v2k -debug_all(跑了一个全加器的tb)

出现Error-[ITSFM] Illegal `timescale for module Module "top" has `timescale but previous module(s)/package(s) do not.编译时,要将带有`timescale或者宏定义的文件列在前面

-full64 VCS以64位运行

-l readme.log 用于将编译产生的信息放在log文件内

+v2k是使VCS兼容verilog 2001以前的标准

-debug_all用于产生debug所需的文件

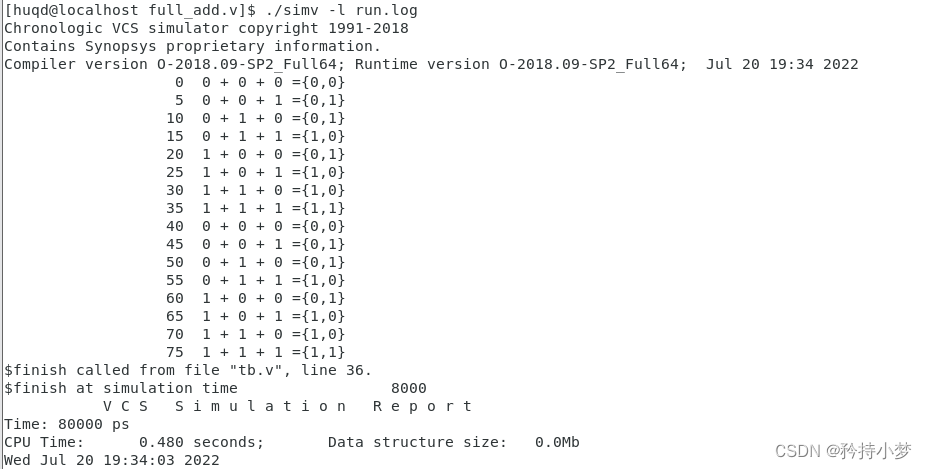

2. ./simv -l run.log开始仿真,终端可以看到tb中需要打印的信息

-l run.log记录终端上产生的信息

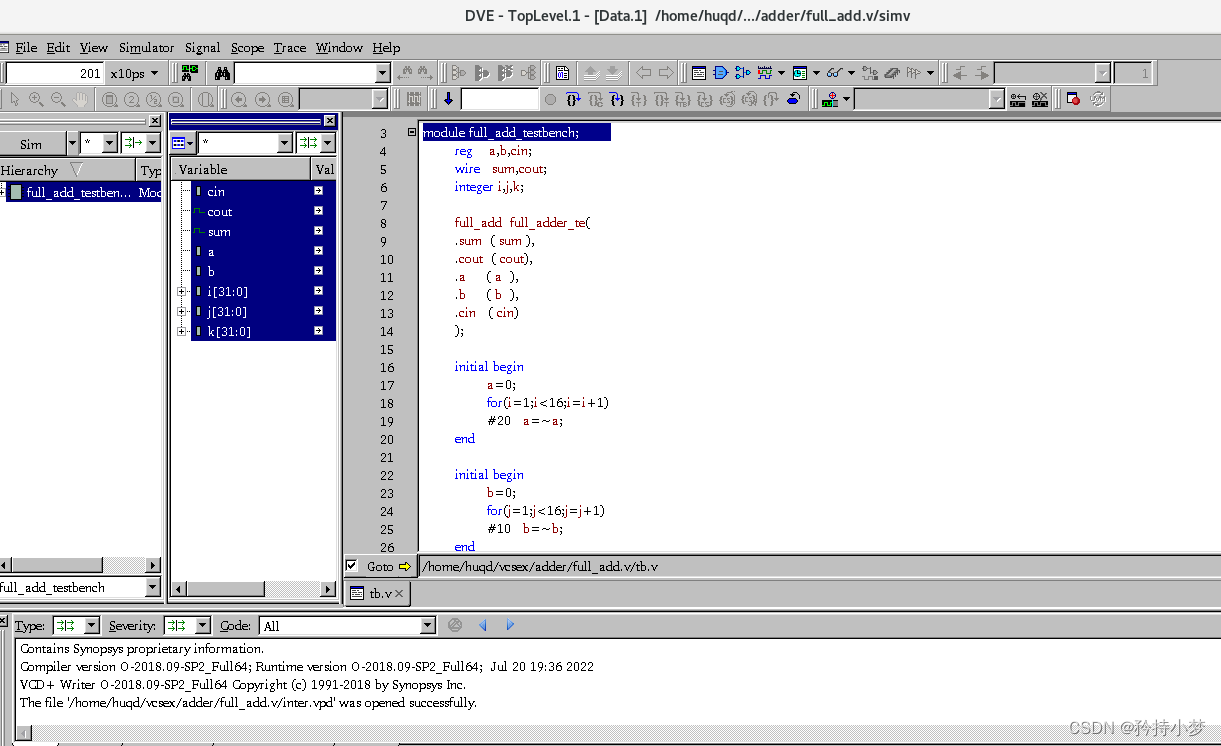

3. ./simv -gui命令打开图形化界面DVE,选中所有信号 --> 右键Add to Waves --> New Wave View

本文介绍了VCS仿真工具的基本使用方法,包括编译全加器代码、解决`timescale`错误、运行仿真、打开图形化界面DVE查看波形,以及使用-f选项、-R、-Mupdate等编译选项提高效率。通过建立tc.f文件和makefile,简化复杂项目的编译过程。

本文介绍了VCS仿真工具的基本使用方法,包括编译全加器代码、解决`timescale`错误、运行仿真、打开图形化界面DVE查看波形,以及使用-f选项、-R、-Mupdate等编译选项提高效率。通过建立tc.f文件和makefile,简化复杂项目的编译过程。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?