1.AHB-SRAMC 设计需求

(1)支持低功耗(clock gating,power gating)SRAM Memory的读写时功耗与非读写时(standby)状态的功耗;不使用SRAM时,处于standby(待机)

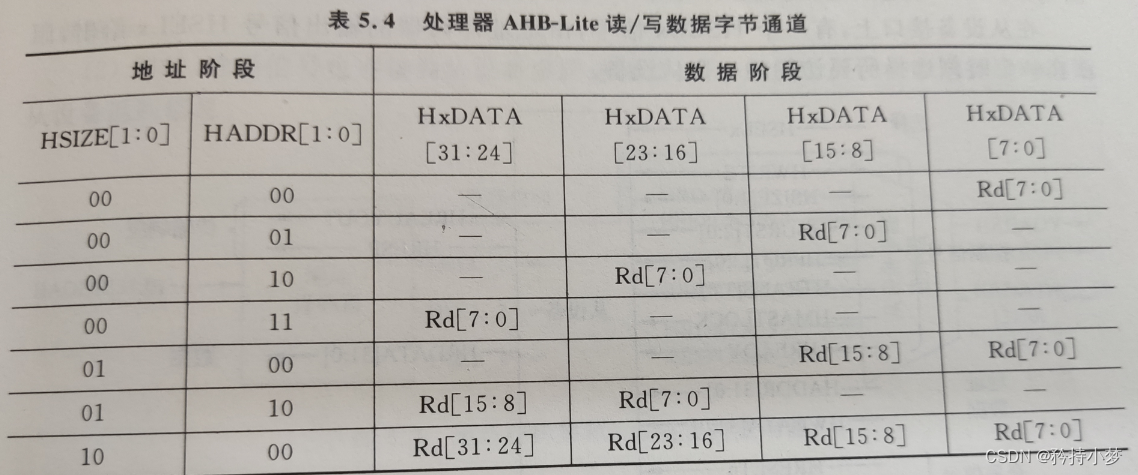

(2)支持8,16,32位SRAM数据读写操作

(3)支持SRAM的单周期读写

(4)支持在多块SRAM组成的储存器中,根据不同地址,系统选择一块或者多块SRAM,未被选中的SRAM块处于待机状态

(5)能够根据AHB总线的读写宽度进行相应SRAM位宽选择(AHB是32bit(4个地址数据)数据位宽,一个地址是8bit数据。假如我只需要读2个地址,这个时候就需要显著标明有效位宽了)

2.AHB-SRAMC 设计架构

在计算机中最小的信息单位是bit,也就是一个二进制位,8个bit组成一个Byte,也就是字节。总线一次访问的是4个8bit,即32bit,这就是为什么64K大小的RAM,实际用到的SRAM深度为16K。因为一个SRAM能存取的数据宽度是32位,相当于是能存4个地址。因此64K个地址存储空间,只需要16K的深度。

由于考虑低功耗的话,我们将其分为了上下2个8K。因为AHB访问一次的话,只可能访问一个地址,要么在上8K,要么在下8K。这样就可以通过地址的最高位来判断它是上8K还是下8K。如果是上8K,下8KCS为0,就可以让其工作在standby模式,可以降低其功耗。

3.AHB

(1)AMBA分为APB、AHB(AHB-lite)、ASB。AHB特点:高性能,2级流水线操作,可支持多个总线主设备,支持burst传输(实质就是只发送一次地址)

burst传输:(实质就是只发送一次地址,一次发一串数据)

通常总线带宽是32bits,即可以读取4个地址的数据。对于传统single传输,需要在第一个地址周期发送ADDR = 0x50,便可以在第二个数据周期读取地址0x50/0x51/0x52/0x53组成的32位数据。再想读接下来的4个地址数据,需要再在第一个地址周期发送ADDR = 0x54,便可以在第二个数据周期读取地址0x54/0x55/0x56/0x57组成的32位数据。这样读取下来,一共花费了4拍。

而Burst传输要想读取上述2个32位数据,需要在第一个地址周期发送ADDR = 0x50和INCR2(表示需要从0x50这个地址连着读2个32位数据),那么可以在第二个数据周期读取一个32位数据,在第三个数据周期再读取一个32为数据,一共花费了3拍。

同理,多读N个数据,那就发送地址之外再发送INCN即可,一共需要N+1拍。

Burst分为回环(WRAP)(适用于Cache填充)和增量(INCR),

总线带宽,上升沿触发。(AHB相对于APB,主要在于两级流水)

| 信号 | 来源 | 描述 |

| HCLK | 时钟源 | 时钟 |

| HRESETn | 系统总线 | 复位,AHB复位信号低有效,一般与总线复位信号相连 |

| HADDR[31:0] | Master | 地址总线。最大可达32位,由外围总线桥单元驱动 |

| HTRANS[1:0] | Master | 当前传输类型:IDLE, BUSY,NONSEQ, SEQ |

| HWRITE | Master | 高为写操作,低为读操作 |

| HSIZE[2:0] | Master | 8,16,32,Byte,Halfword,Word |

| HBURST[2:0] | Master | 单个数据,任意长度数据,打包4拍,地址回环Single,INCR,WRAP4,INCR4 |

| HPROT[3:0] | Master | 保护控制信号,需要slave带保护功能,一般不用 |

| HWDATA | Master | 写数据总线,Master到Slave |

| HRDATA | Slave | 读数据总线,Slave到Master |

| HREADY | Slave | 高Slave传输结束,低Slave需延长传输周期 |

| HRESP[1:0] | Slave | Slave发给Master的传输状态,AHB to APB时,PSLVERR被映射到HRESP |

| HSELx | Decoder | slave选择信号 |

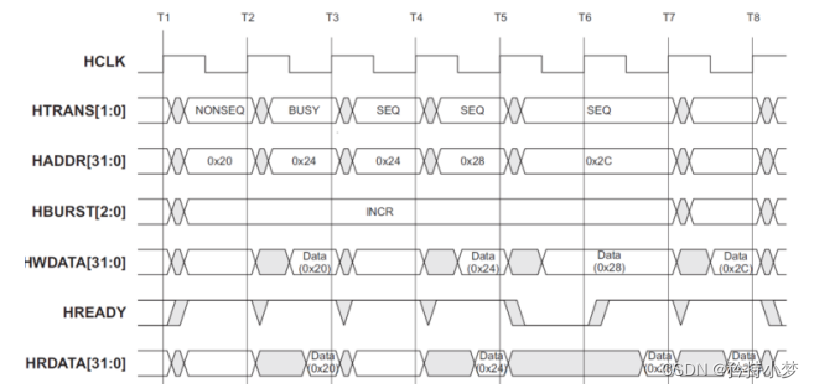

1.递增burst

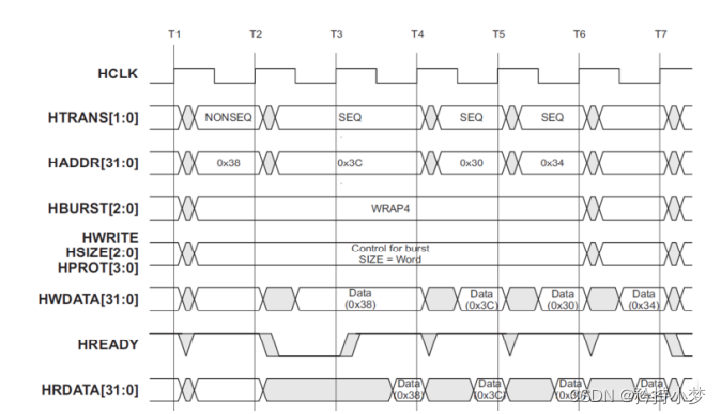

2.回环4beat的burst

HTRANS的busy和HREADY区别在于busy情况下master需要给出下一拍的地址和控制信号,与上一拍相同,ready只需要延长信号传输到下一拍

两级流水:流水操作直接体现就是在进行地址1发送的时候,可以读取地址0对应的数据。

(2)AHB一次访问需要两拍

4.SRAM

(1)SRAM一次访问需要一拍(需要做一个2拍到1拍的转换)

5.AHB协议中addr的限制

(hsize == HWORD)-> (haddr[0] == 1'b0);

(hsize == WORD) -> (haddr[1:0] == 2'b0);- hsize=00时,传输为byte,低8位传输,01为hword,16位传输,10为word,32位传输。

- hword时,低位始终为0,传输word时,haddr2位都是0。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?