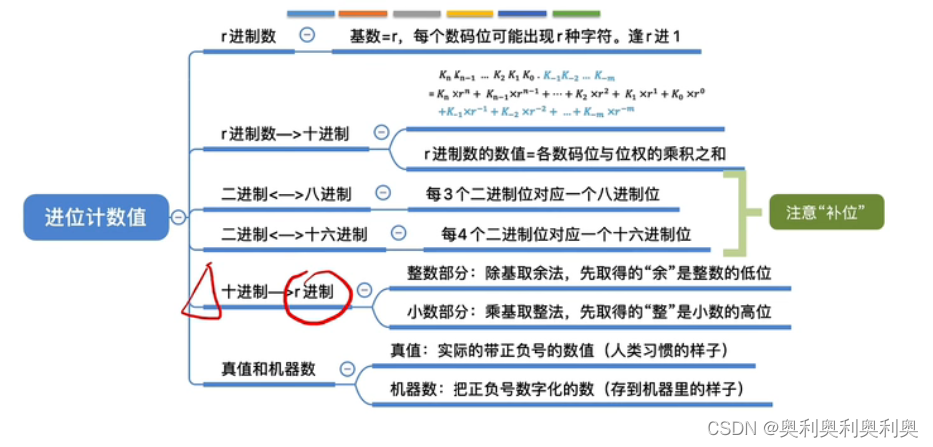

2.1.1进位计数制

1. 概念

(1)基数:r进制的基数为r

(2)使用二进制的原因:

a. 可使用两个稳定的物理器件表示

b. 0、1对应着逻辑真、假

c. 可以方便的使用逻辑as门电路实现算术运算

(3)表示:H16、D10、B2

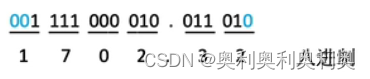

2. 任意进制-》十进制

3. 二进制与八进制、16进制的转换

4. 十进制转任何进制

5. 真值和机器数:真值实际的10进制数、机器数:在机器中存储的样子

注:有可能没办法精确表示:0.3无法用二进制精确表示

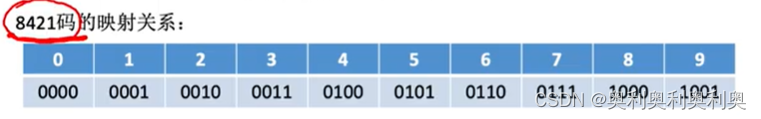

2.1.2 BCD码

1. 8421码(与普通二进制前10个数字相同)

(1)映射见图{8421码映射表}

(2)计算机加法运算:超出+6(0110B)、强制向高位进1

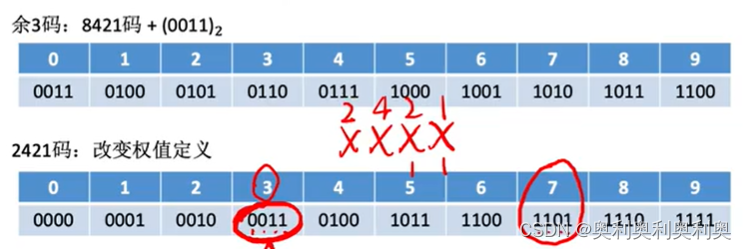

2. 余3码(8421+3(0011B))

(1)映射见图{余3码、2421码映射表}

3. 2421码

(1)映射见图{余3码、2421码映射表}

(2)5后面的数字统一为1开头

区分有权码和无权码:余3码为无权码

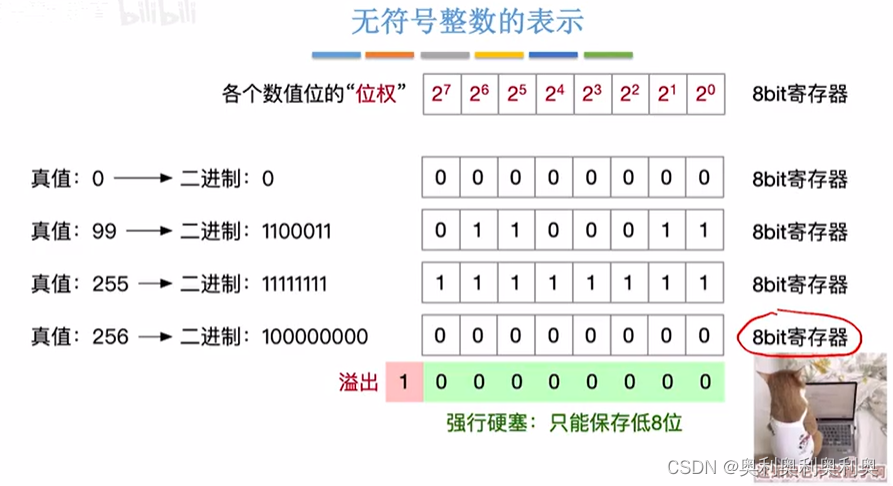

2.1.3 无符号的整数的表示和运算

‘unsigned short、unsigned int’

1. 范围: n bit的无符号整数的表示范围是0~2^n - 1

2. 加法:进位

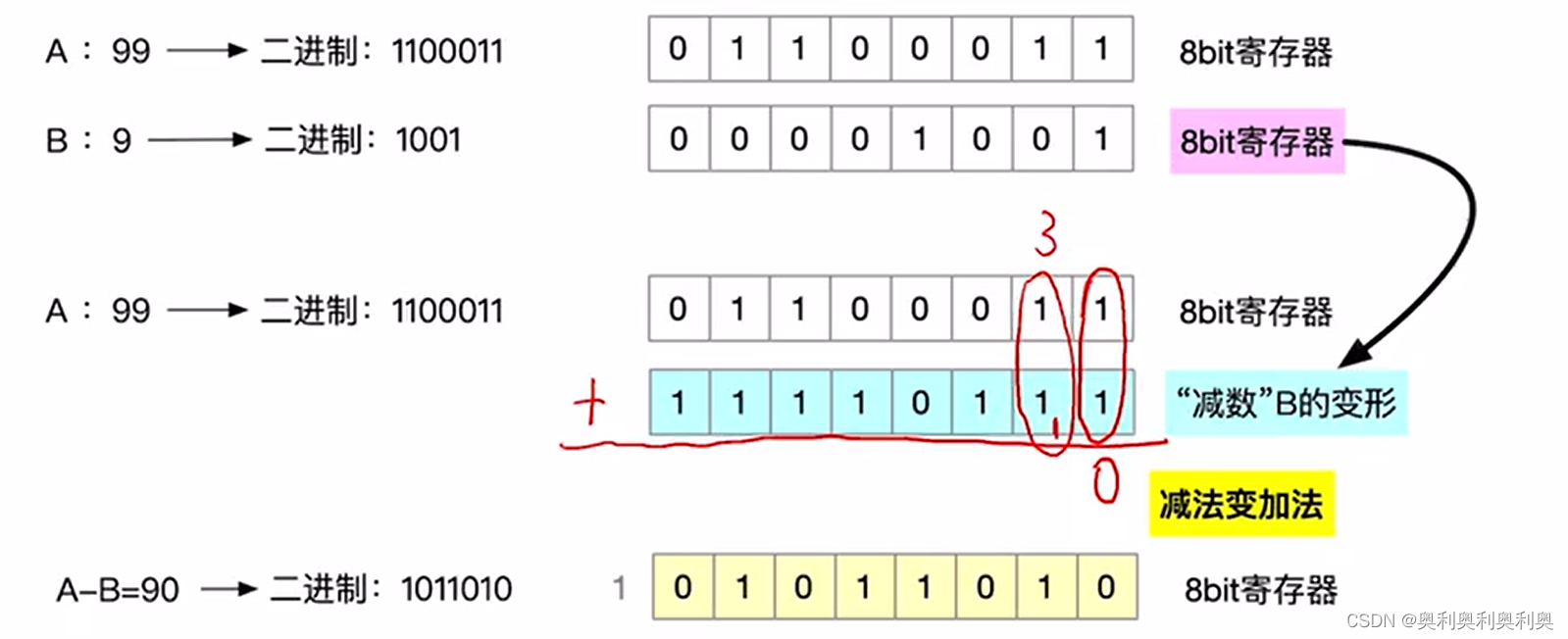

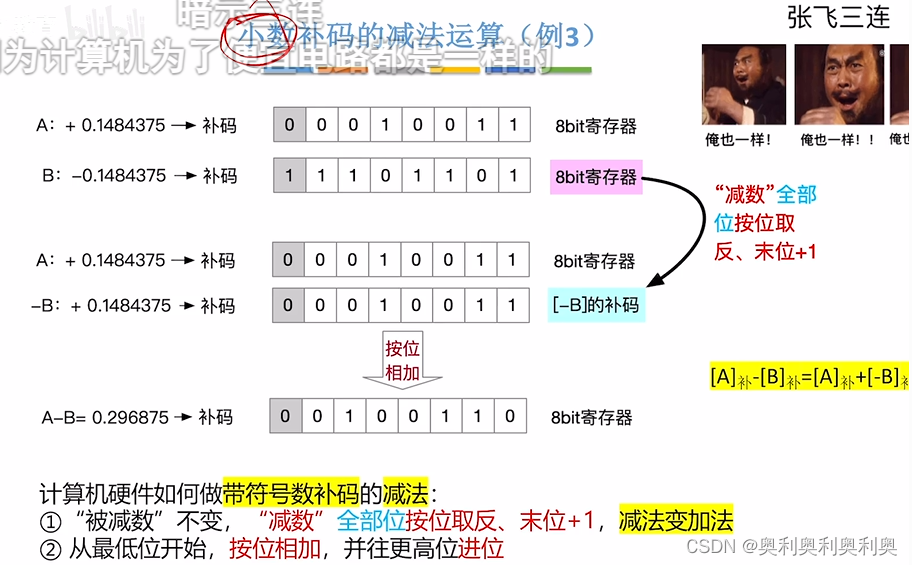

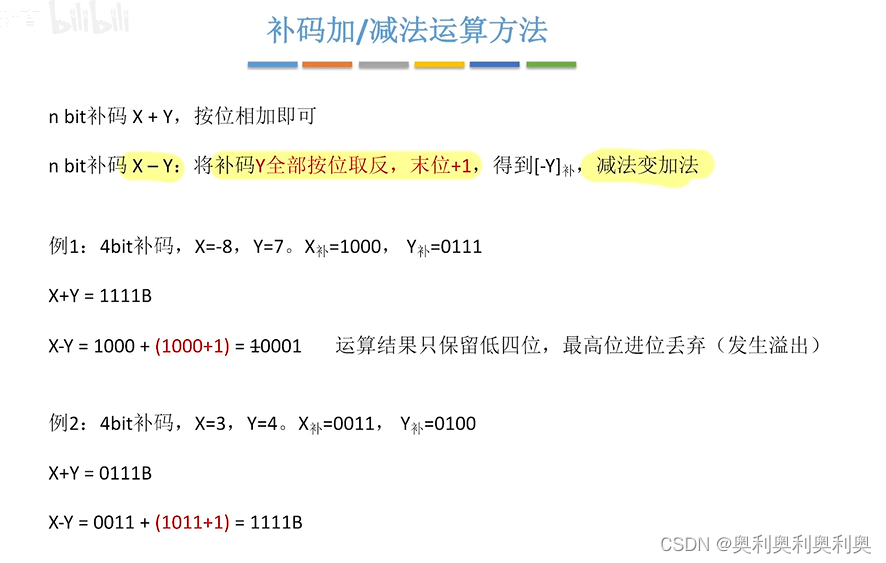

3. 减法:(1)被减数不变、减数全部位按位取反,末位+1,减法变加法

(2)按位相加,并往更高位进位

eg:{无符号位减法试例}

2.1.4 带符号整数在计算机内的表示和运算_原反补、原反补的特性对比、移码

‘short int’

1. 原码表示法

(1)符号位0正1负+数值位

(2)原码的缺点:符号位不能参与运算,需要设计复杂的硬件电路才能处理

解决:用补码表示真值——符号位可以参与运算

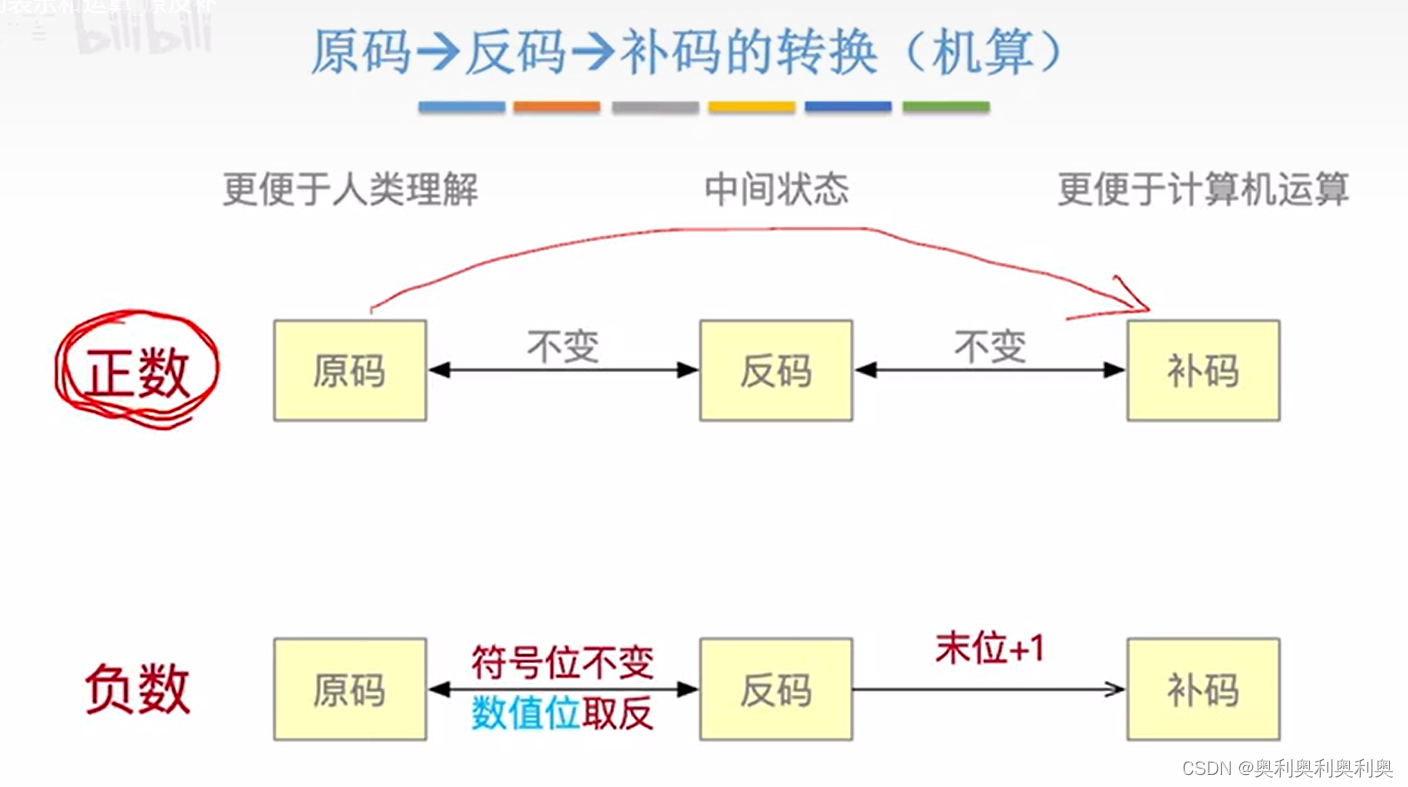

2. 反码表示法

(1)正数的反码 = 原码;负数的反码 = 原码符号位不变,数值位取反

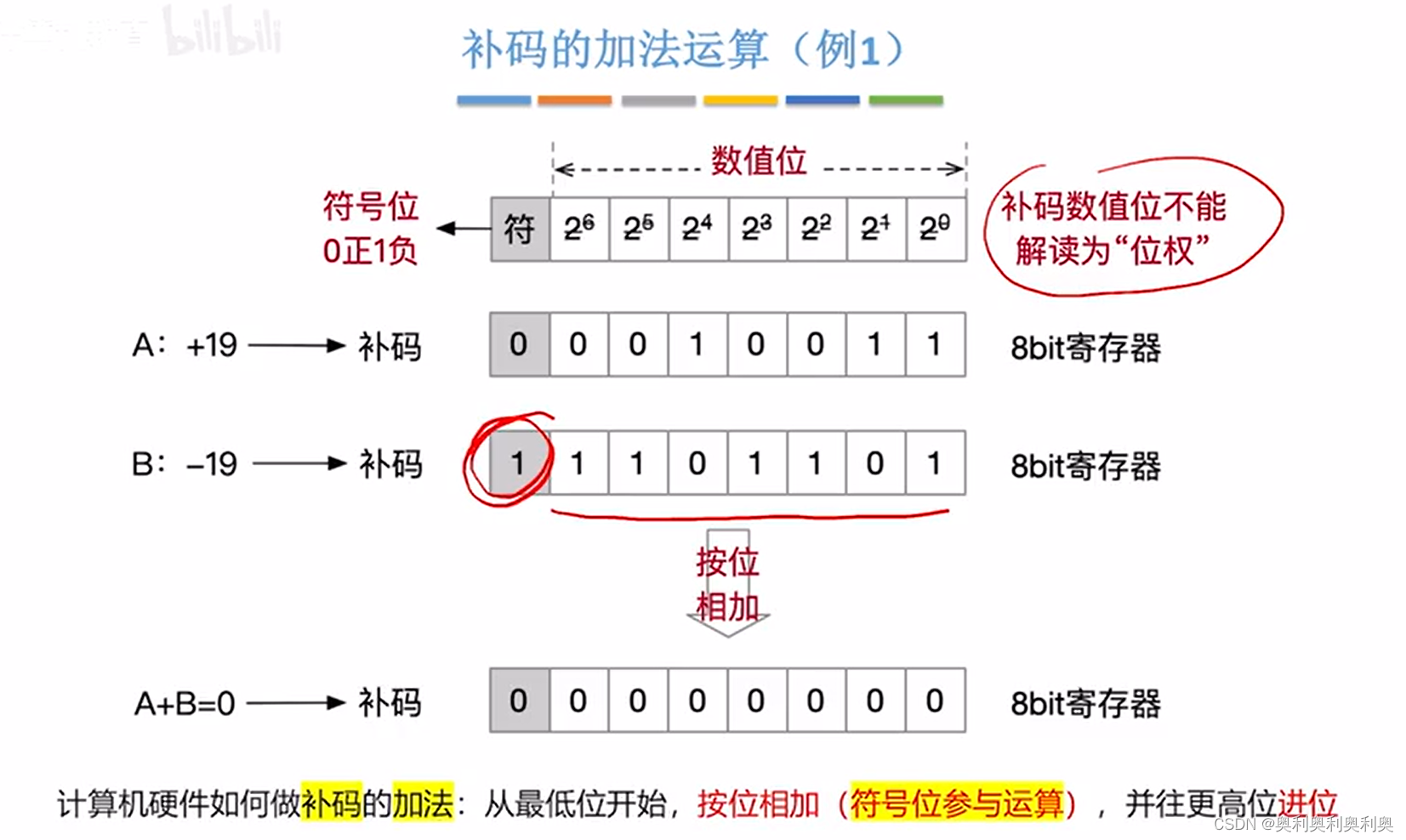

3. 补码

(1)正数的补码 = 原码;负数的补码 = 负数的反码+1

(2)正数的补码 = 原码;负数的补码 = 负数的原码,找到最低位的1,1左边所有数值位取反

x = -100 [x]原 = 1,1100100 [x]补 = 1,0011100

(3)补码的加法:符号位参与计算、进位不算

(4)补码的减法:减法转加法(被减数的补码取反)补码取反 = 补码,找到最低位的1,1左边所有数值位取反,符号位也取反

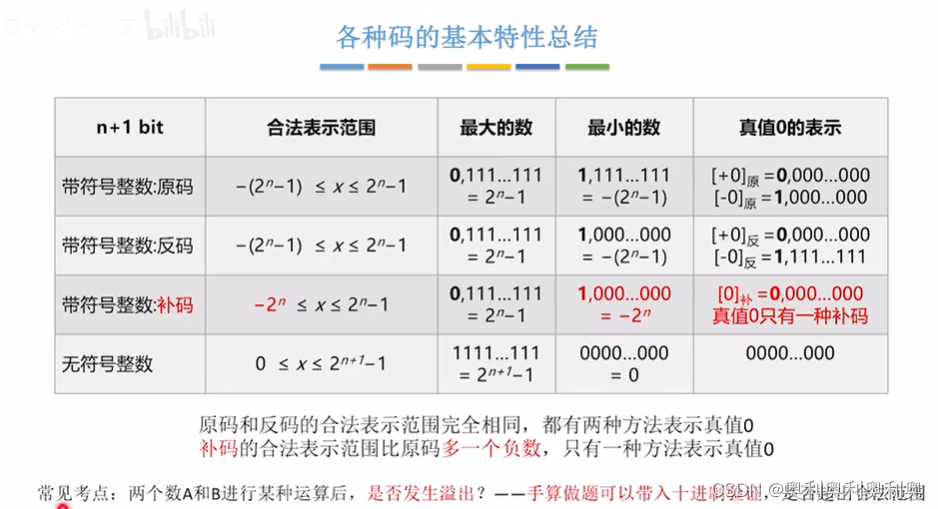

4. 特性对比

(1)n+1比特的原码、反码的范围:-(2^n - 1) ~ 2^n - 1

[+0]原 = 0,000 0000 [-0]原 = 1,000 0000

[+0]反 = 0,000 0000 [-0]反 = 1,111 1111

(2)n+1比特的补码的范围:-2^n ~ 2^n - 1

[ 0 ]补= 0,000 0000

(3)n+1比特的无符号整数的范围:0 ~ 2^n+1 - 1

5. 补码(补码的基础上将符号位取反,注意:移码只能表示整数)

(1)具由的特性:

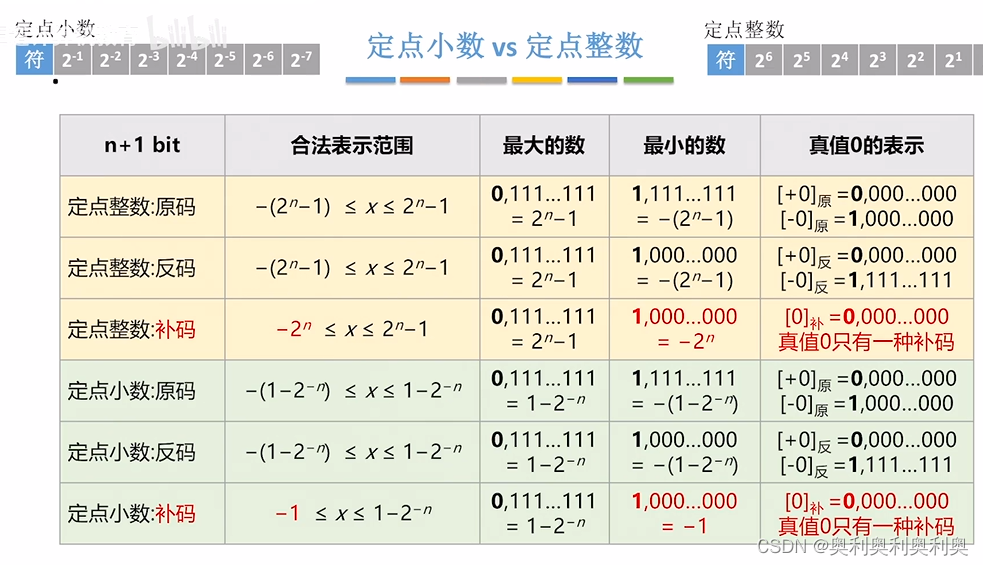

2.1.7 定点小数

1. 定点小数的编码表示:原码、反码、补码(没有移码)

2. 定点小数的加减:转换为补码进行加减

3. 特性迁移(定点小数)

(1)范围:{}

(2)加减: 与定点小数同一套硬件进行运算

2.2.0 奇偶校验码(大纲已删)

1. 奇偶校验码的定义

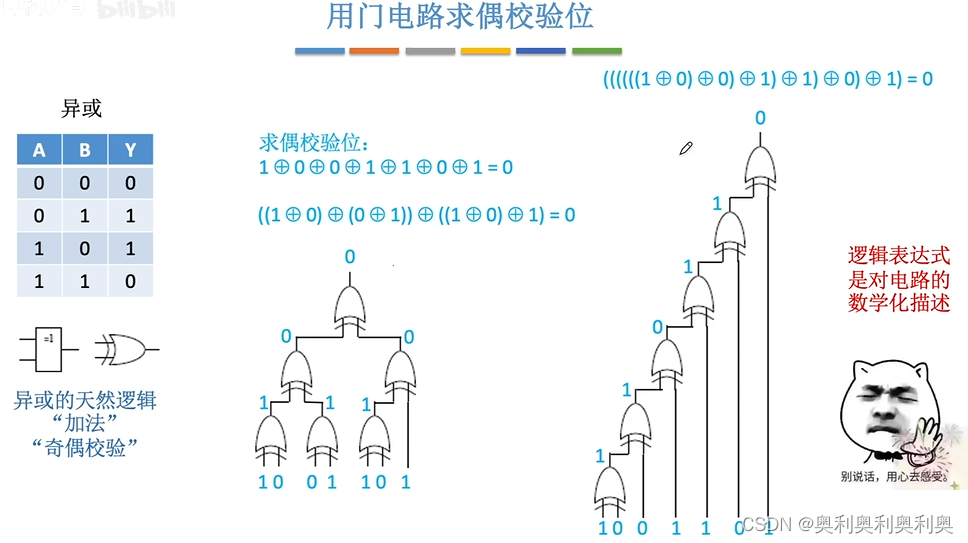

2. 硬件实现:异或运算得到偶校验位,验证时所有位进行异或:1出错

2.2.1

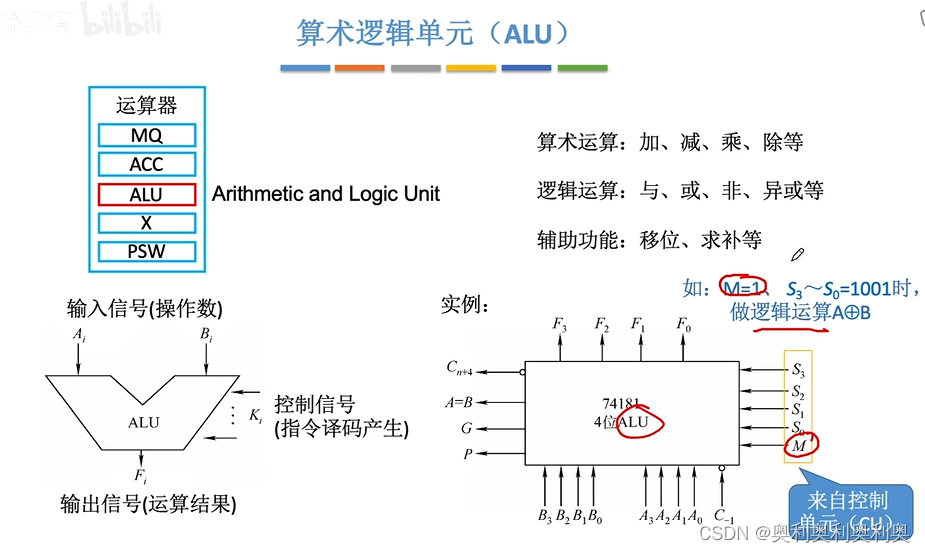

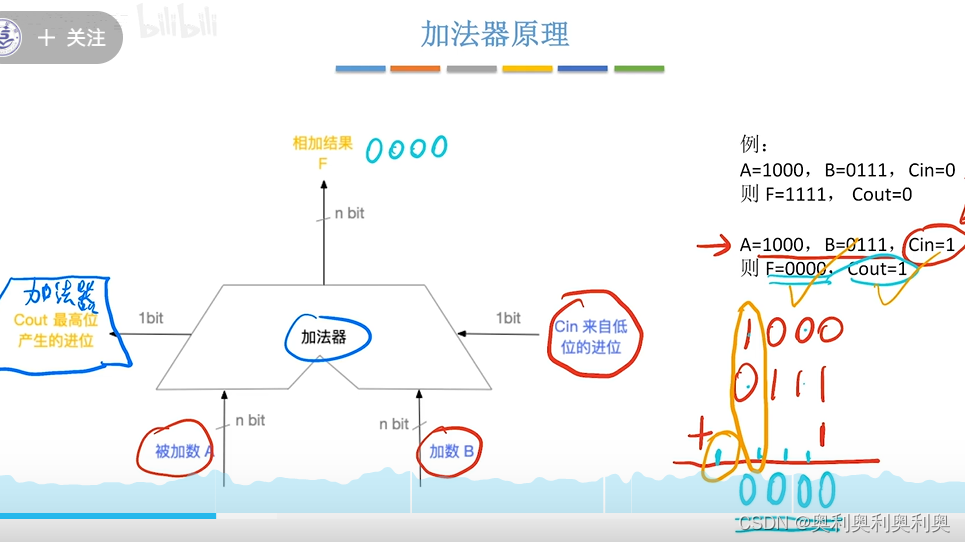

1. ALU算术逻辑单元{算术逻辑单元}

(1)机器字长 = ALU输入的位数 = 寄存器的存储位数

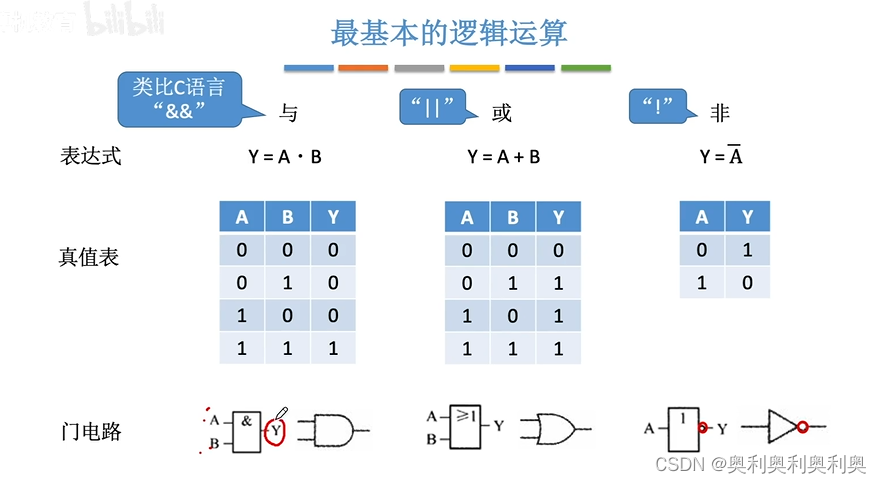

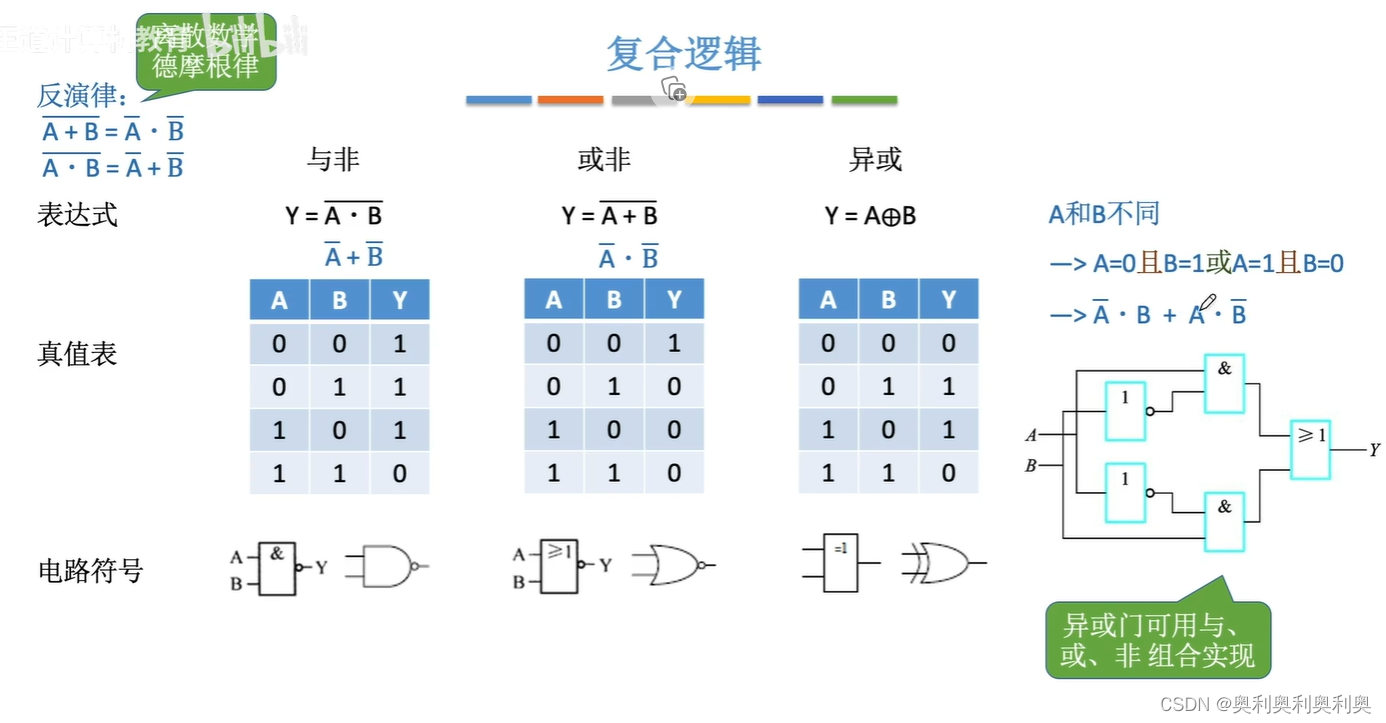

2. 逻辑运算:与、或、非、与非、或非、异或、同或

(1)先乘除(与)、后加减、符合分配结合律(优化电路设计)

(2)反演律\德摩根律:

(3)异或门的实现

(4)用门电路实现奇偶检验

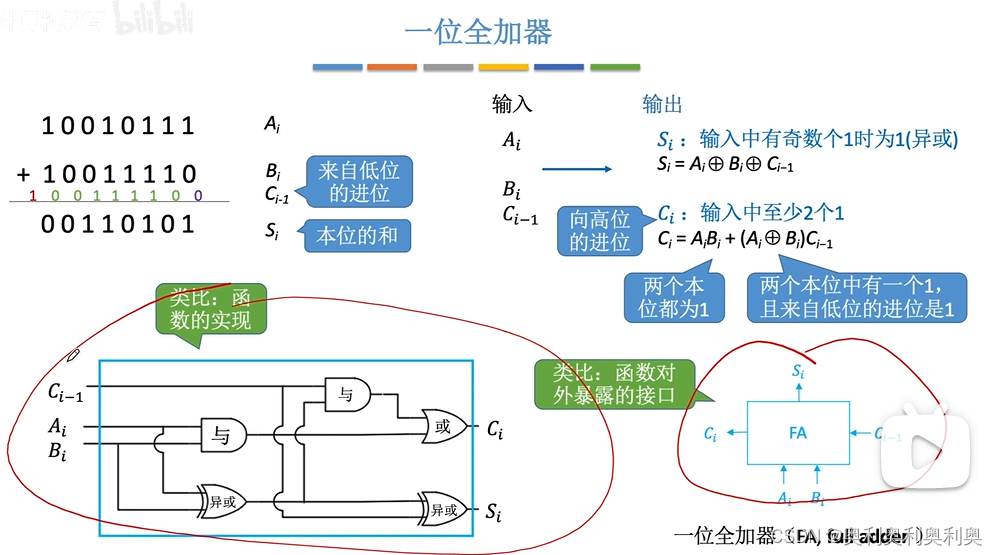

3. 一位全加器

(1)原理与公式推导:{}

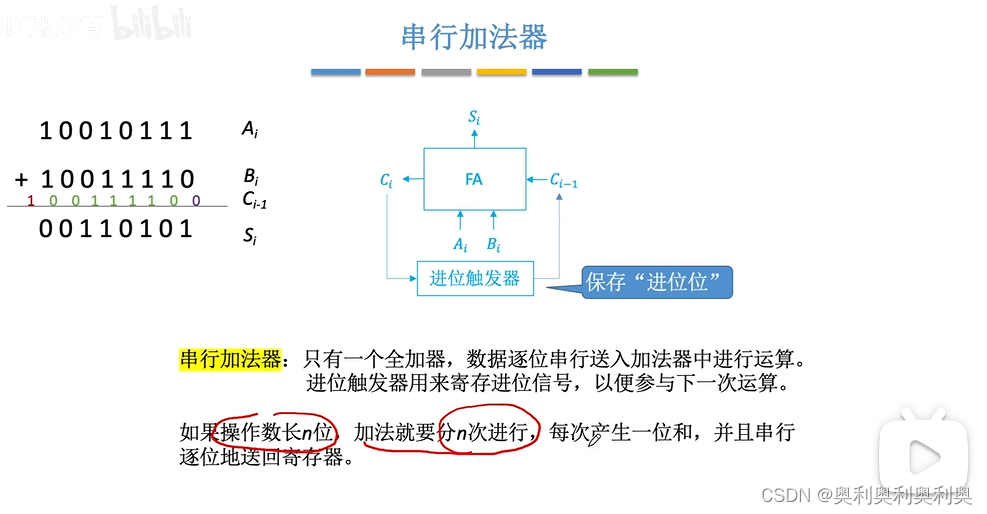

(2)串行加法器:数据逐位串行送入加法器中进行运算、效率低{}

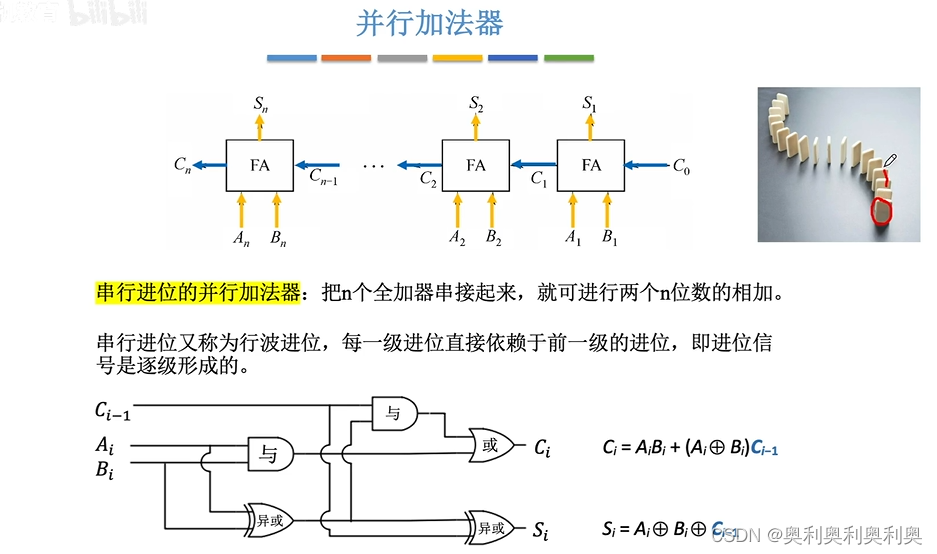

(3)并行加法器(行波进位):把n个全加器串接起来{}

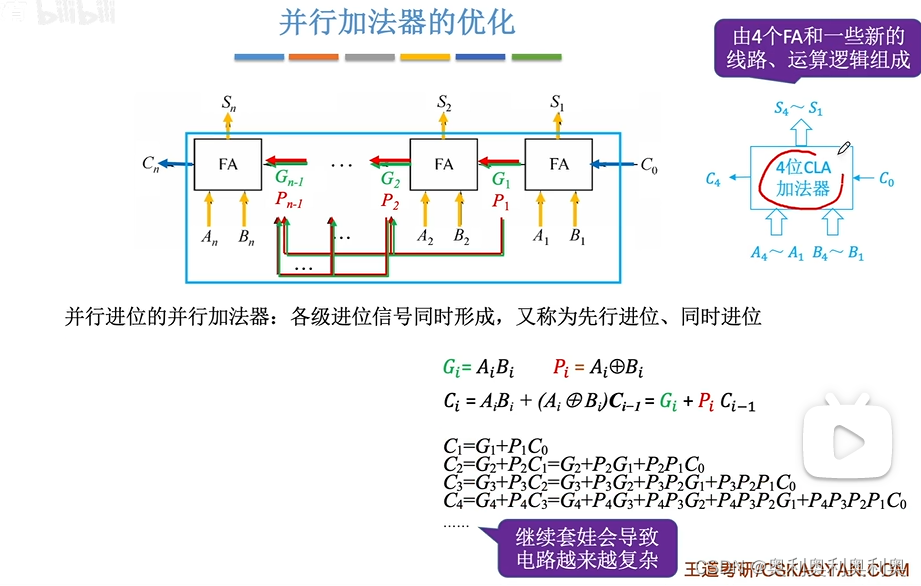

(4)优化:更快的产生进位:各级进位信号同时产生,又称先行进位

a. 但是位数变多会使得电路变得非常复杂

2.2.3 补码加减运算器

1. 两个四位的加法器经过扩展可以实现8位的加法运算

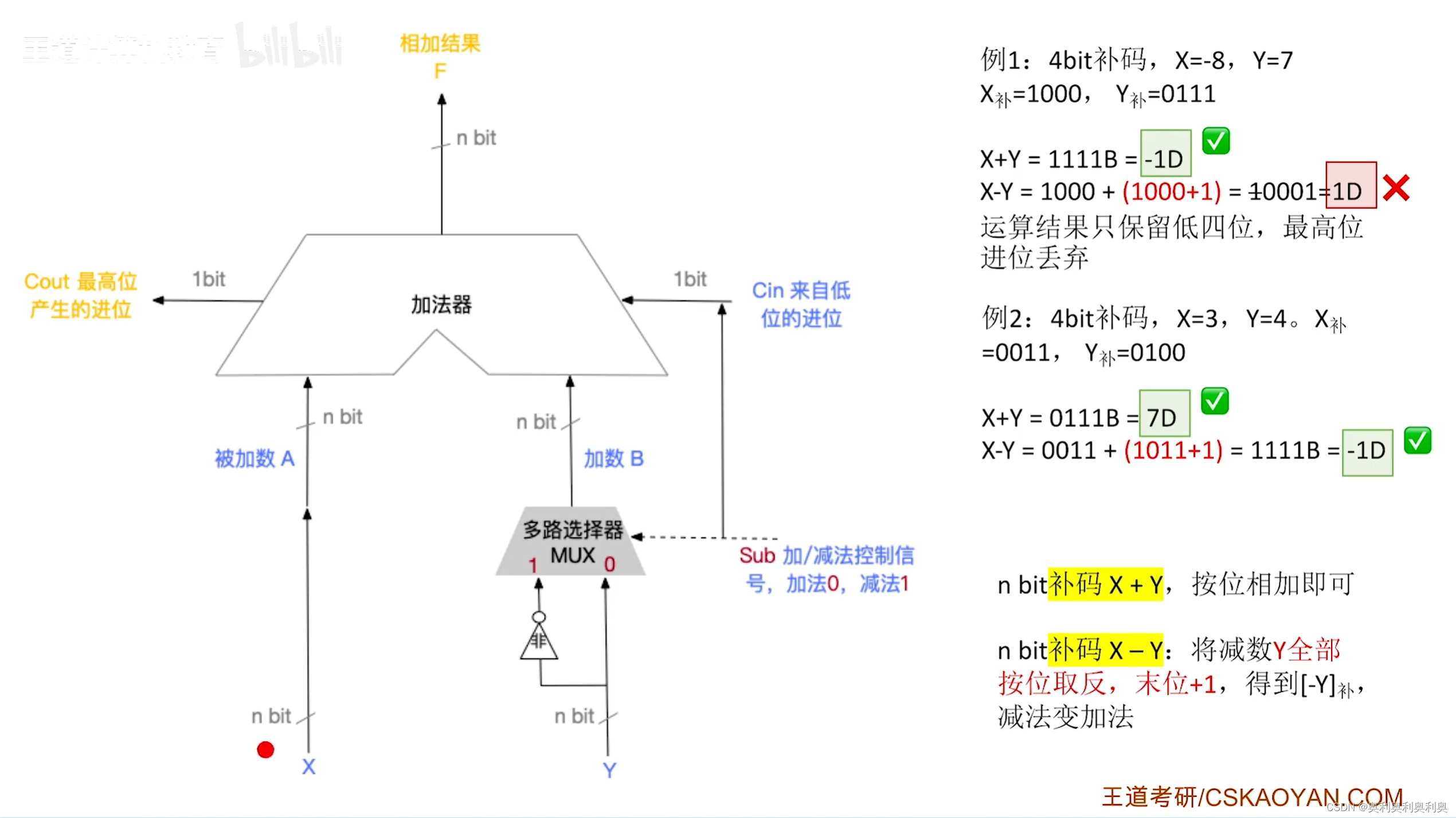

2. 加法器:无论是有符号数还是无符号数,底层实现的加法器是一样的

{加法器实现有符号数的加减} {加法器实现无符号数的加减}

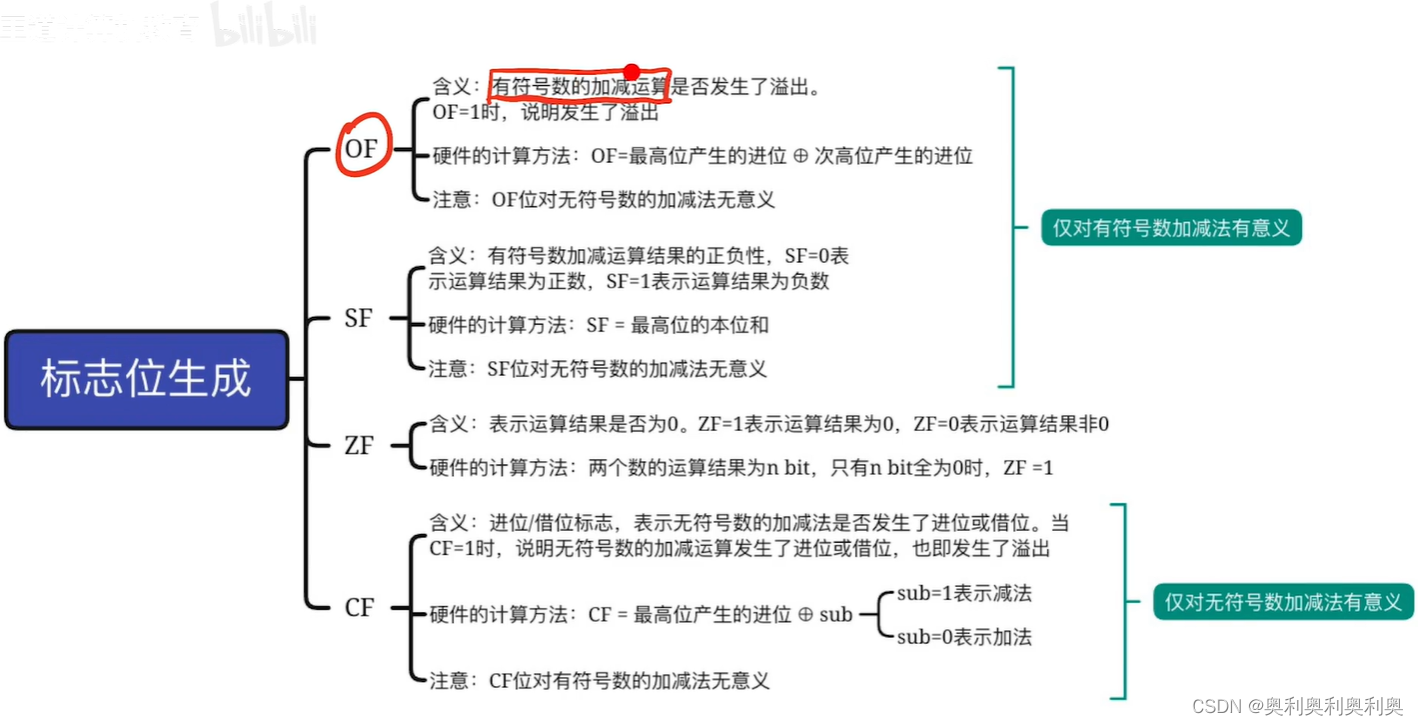

3. 标志位

(1)OF(有符号数):最高位与次高位产生的进位异或结果:1为溢出

eg: 1000B - 0111B(-8-7) = 1000 + 1000 + 1 = 1,0001

(最高位进位1次高位进位0:溢出)

(2)SF(有符号数):最高位表符号

(3)ZF():运算结果是否为0F

(4)CF(无符号数):Cout 异或 Sub,1表示溢出

eg:(3-4)0011B - 0100B = 0011+(1011+1) = 0011+1100 = 1111 = 15D×

(Cout=0,Sub=1,表示溢出)

C

OF(最高两位要同时进位,不同时进位异或为1)、ZF(zero)、CF(减号要进位)、SF(sign)

2.2.5 定点数的移位运算

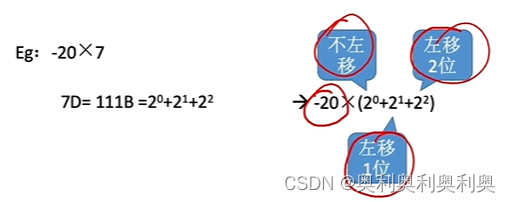

1. 算术移位

负数的移码 -12 -6 -3 操作

原码 1 1100 1 0110 1 0011 补0 反码 1 0011 1 1001 1 1100 补1 补码 1 0100 1 1010 1 1101 高位补1低位补0 作用:计算机实现乘法

2. 逻辑移位(没有意义,凑0,RGB的拼合)

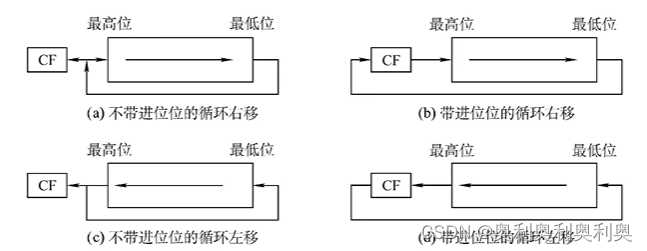

3. 循环移位(成环,区分带进位位与不带进位位)

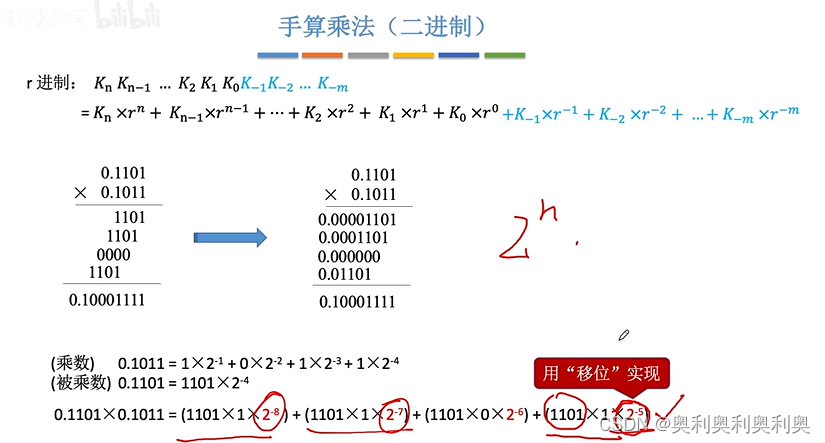

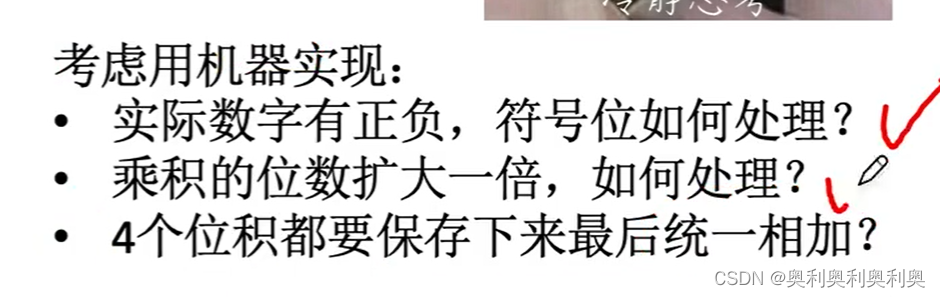

2.2.6 原码、补码的乘、除法运算

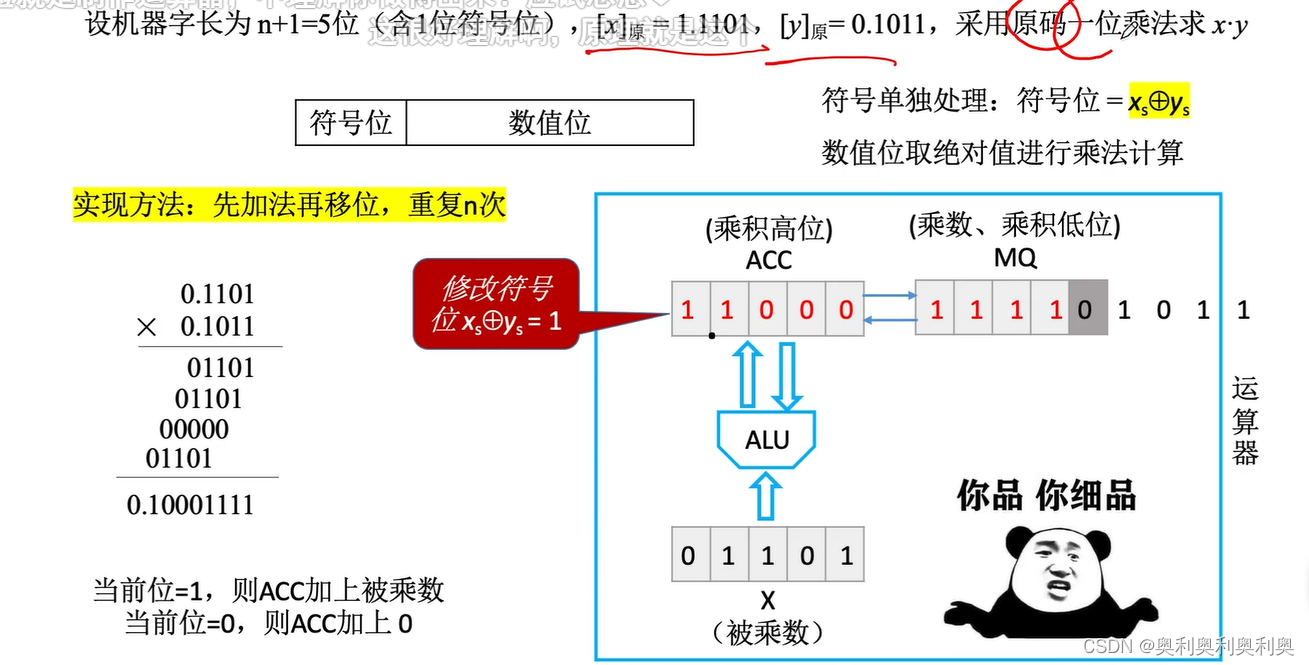

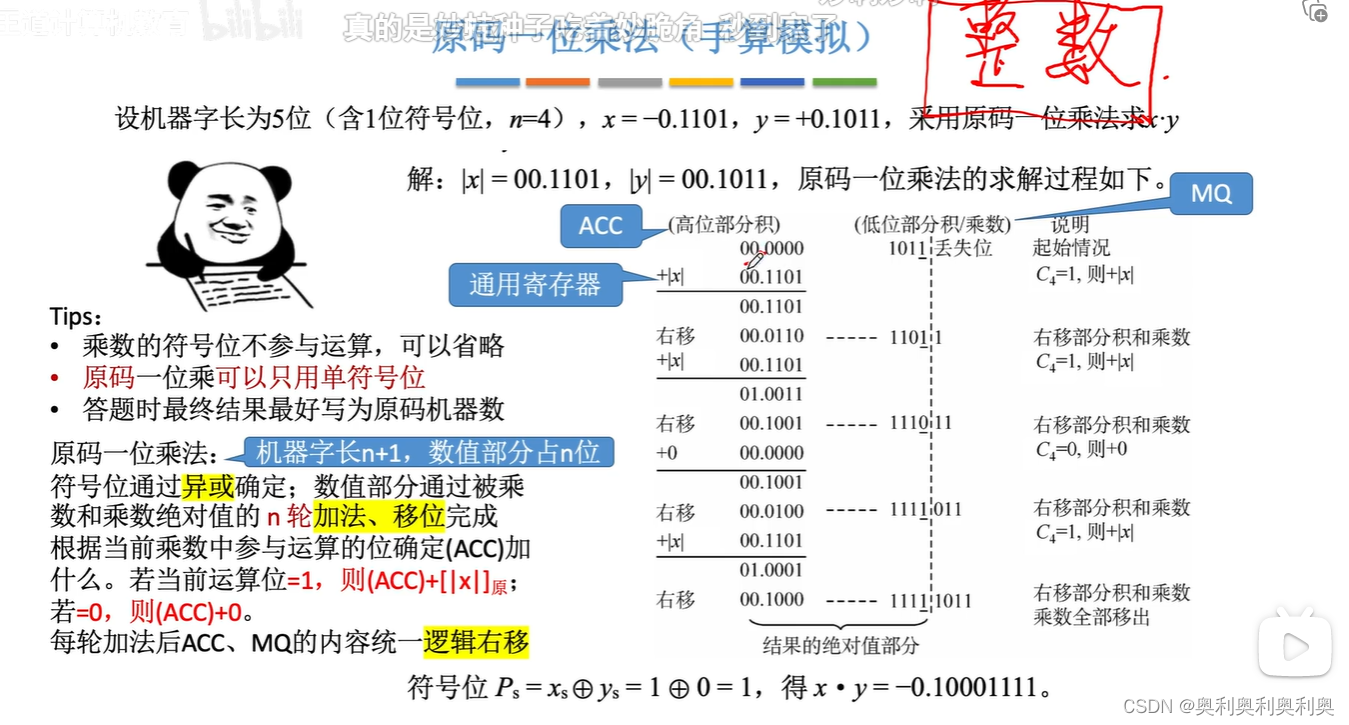

1. 原码乘法

(1)手动乘法的理解

(2)机器实现

a. 符号计算:异或

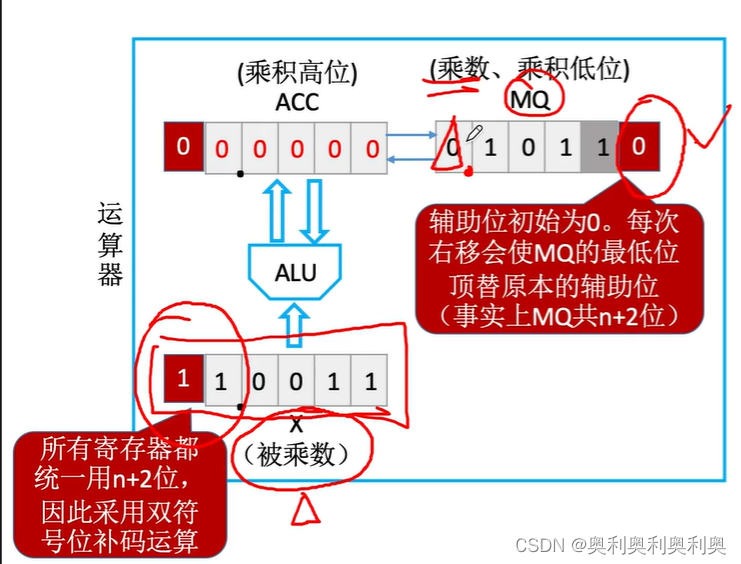

2. 补码的乘法

(1)所有寄存器采用n+2位

MQ(商余寄存器采用1位符号位+4位补码+1位辅助位)

X与ACC(采用2位符号位进行运算)

(2)根据当前MQ中的最低位、辅助位来确定加什么

辅助位 - MQ最低位 = 1,(ACC)+[x]补

辅助位 - MQ最低位 = 0,(ACC)+0

辅助位 - MQ最低位 = -1,(ACC)+[-x]补

(3)手动运算细节

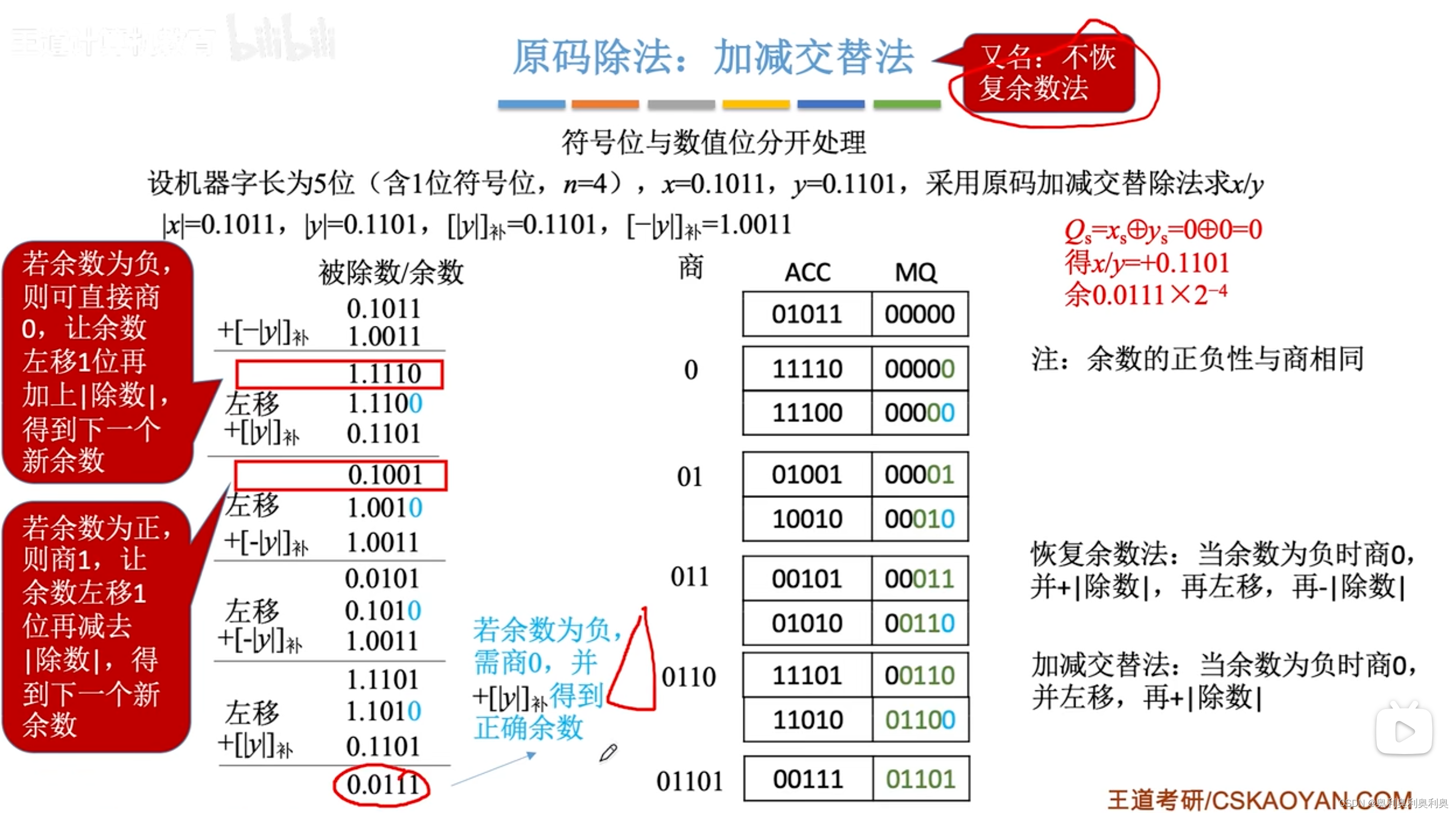

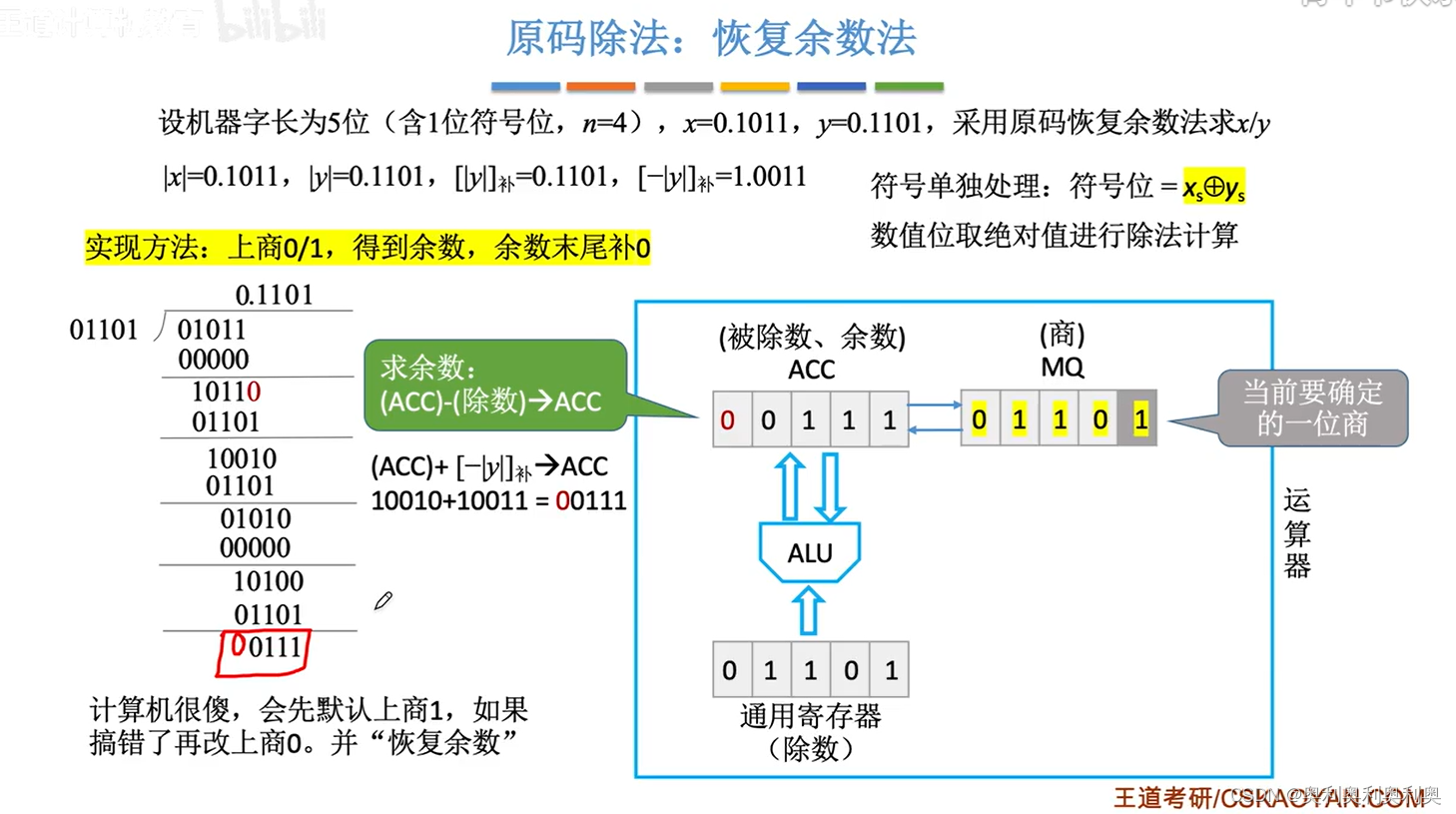

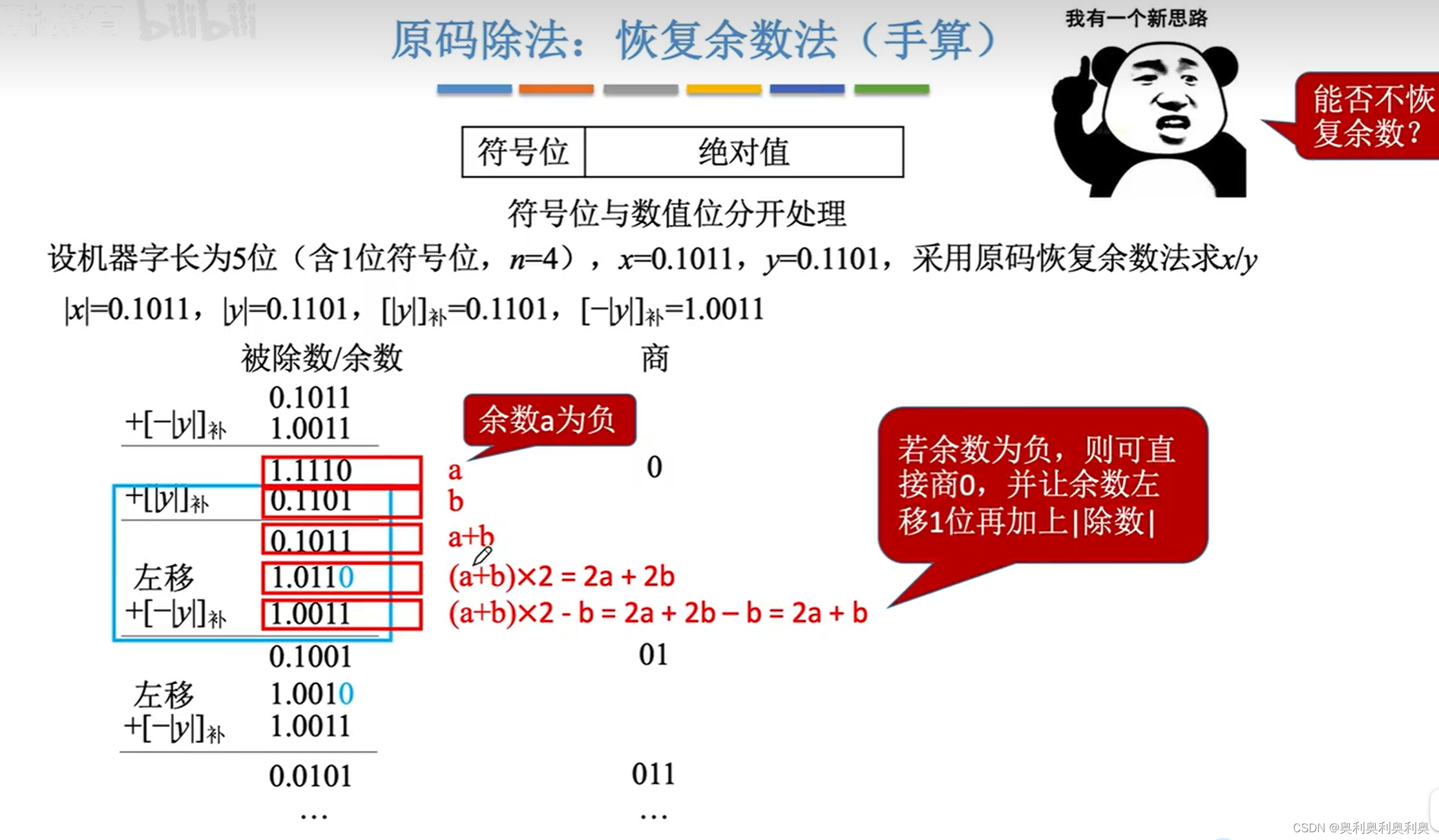

3. 原码的除法(得到定点小数)

(1)恢复余数法(符号单独计算,寄存器为n+1)

a. ACC:被除数、余数(初始值为被除数)

MQ:商(初始值为0)

b. 需要用到被除数y绝对值的正负补码

([|y|]补、[-|y|]补,只有补码能进行相减操作)

c. 默认将每位商置为1,(ACC)+[-|y|]补码->ACC

若结果为负数,撤销上一步 (ACC)+[|y|]补码->ACC

得到的结果左移(ACC与MQ,相当于算数乘2)

d. 余数:余数若为负数,仍需要恢复余数;余数最后的符号与商一致

e. 在原码的除法中,计算机无法表示大于1的商,因此第一位商一定为0(被除数一定小于除数)

(2)加减交替法「原码除法:加减交替」

与恢复余数法一致,只是合并了恢复余数和下一位商的计算:

若余数为负(恢复余数法,前一步为商置1,余数=余数-y):1⃣️本位商改1为0,2⃣️恢复余数:(ACC)+[|y|]补->ACC3⃣️移位:左规(算术乘2)4⃣️下一位预设:下一位商置1,余数更新(ACC)+[-|y|]补->ACC

(假设负余数的大小为a,|y| = b(正数,无论原补码),1⃣️2⃣️3⃣️4⃣️步可统一为:)

1⃣️余数为负数 商置0,2⃣️新余数 = 2*(a+b)-b = 2a+b(先移码再加y)

3⃣️余数为负数 商置1,4⃣️新余数 = 2a-b(先移码再减y)

此简便方法即为加减交替法,本质是对恢复余数法步骤的整合,其他性质不变

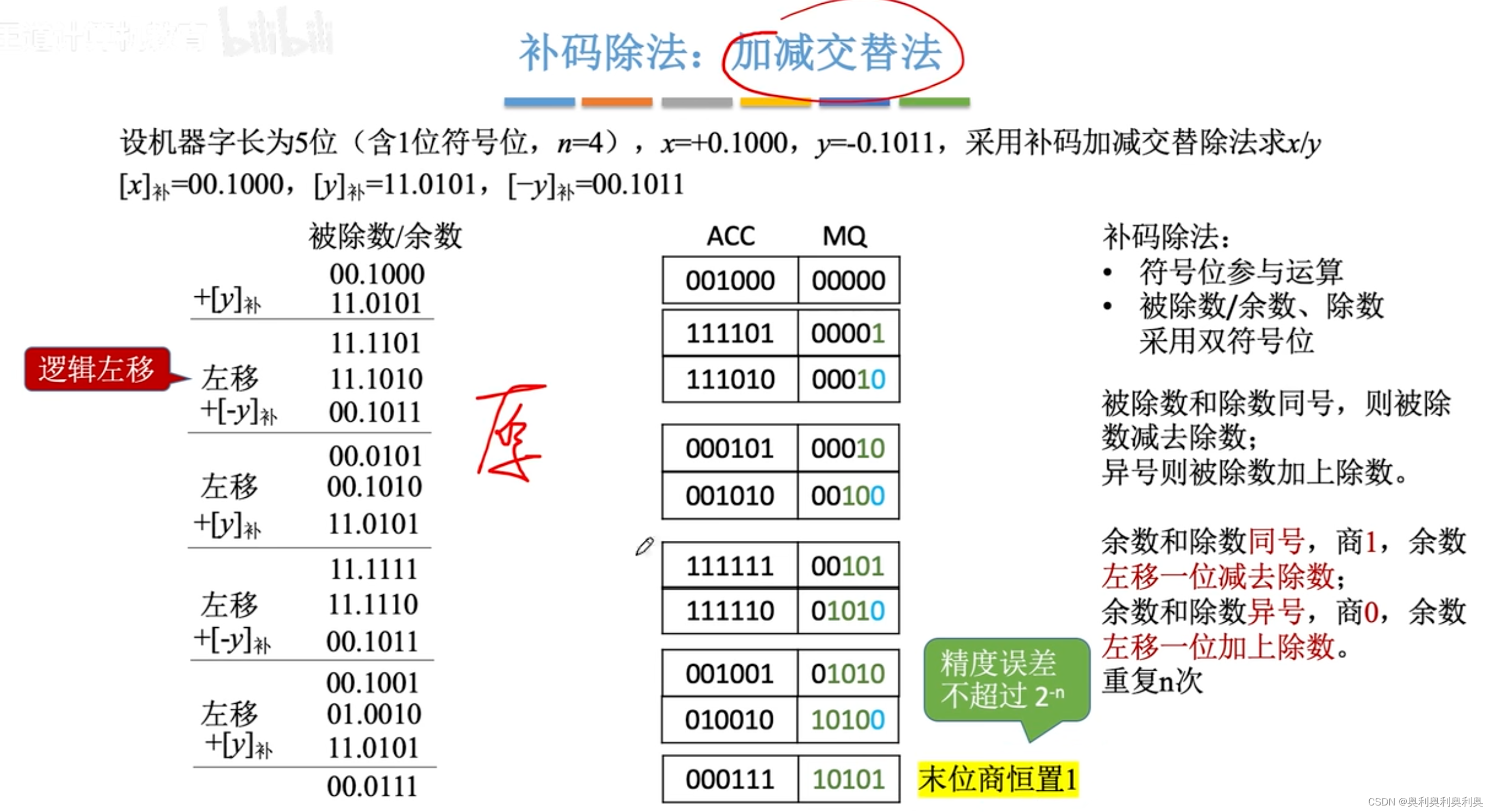

4. 补码的除法(加减交替法,符号位参与计算)

原码除法:加减交替(手动实现)

原码除法:加减交替(流程图)

补码的除法运算 p24

1. C语言类型转换:长变短:高位截断;短变长:

(1) 大小端模式:小端模式符合计算机先读底位的需求

(2) 边界对齐

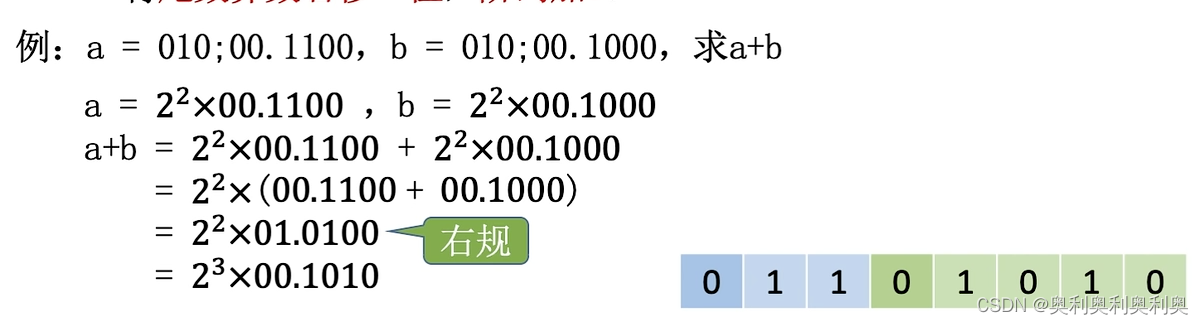

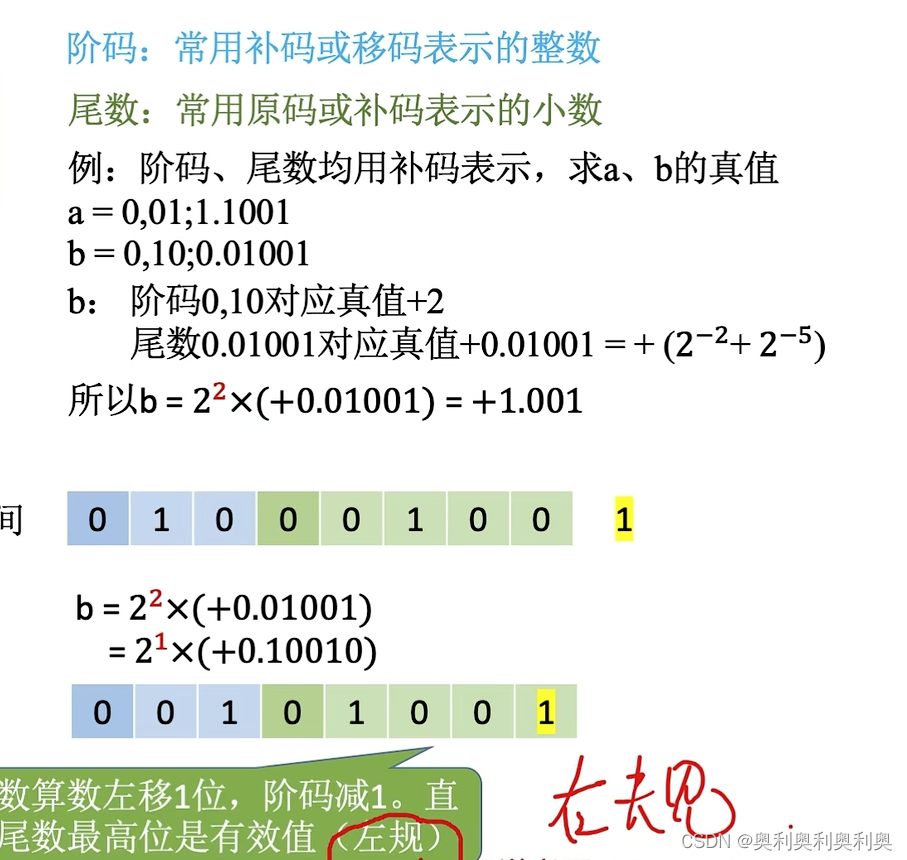

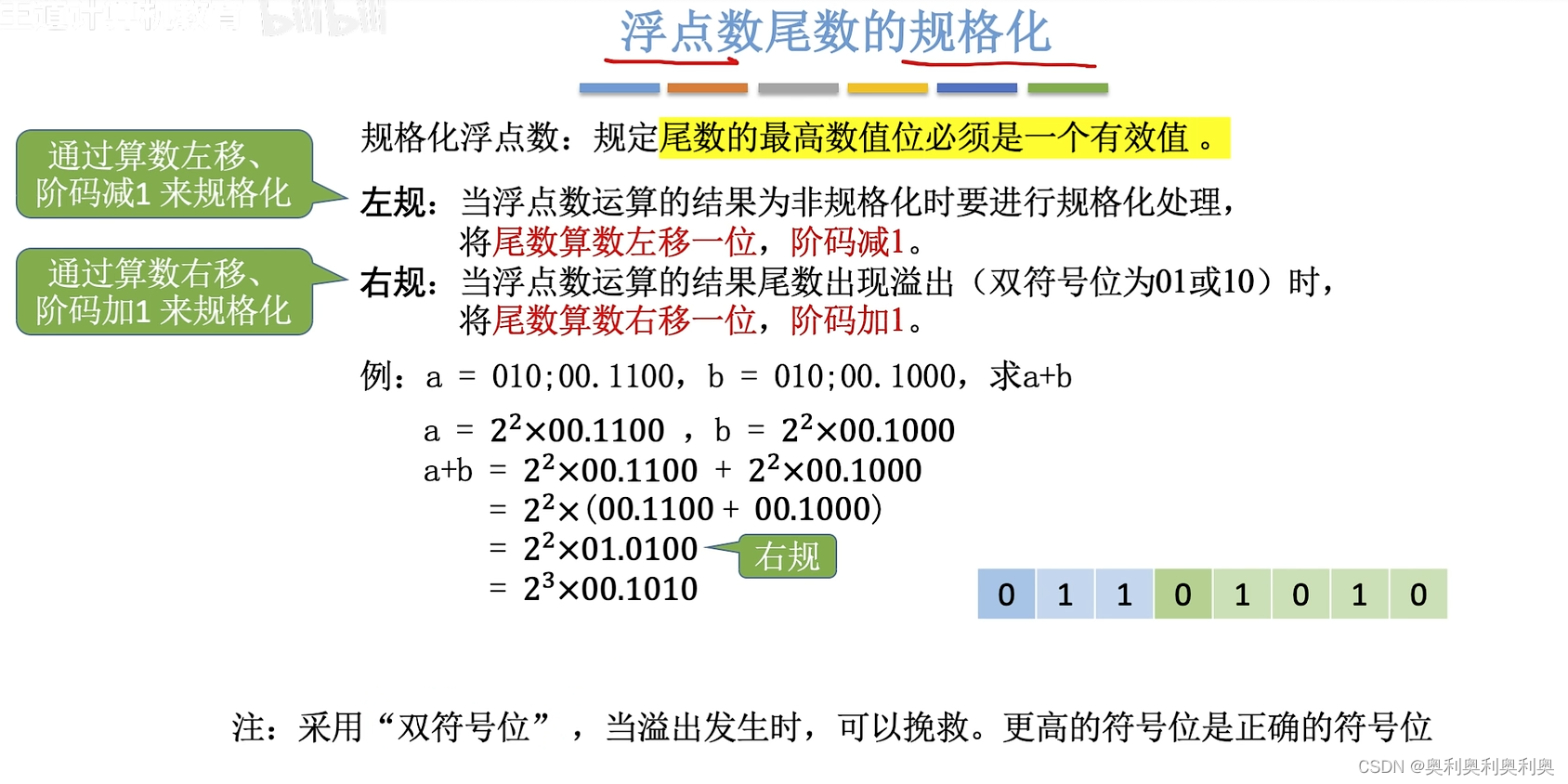

2. 浮点数的运算和排列

(1)阶码+尾数

(2)左规、右规:整体移动、要配合阶码的变化

a. 溢出修正(双符号位):1⃣️双符号高位位判断符号2⃣️左规

b. 防止尾数损失:1⃣️右规

3. 规格化浮点数的特点

(1) 原码表示的尾数进行规格化(最高位为1)

范围:(X.10...0->X.11...1即:1/2<=|M|<=1-2^-n)

(2) 补码表示的尾数进行规格化(最高位为0)

范围:(1.01...1~1.00...0即:-1/2-2^-n>M>-(1-2^-n)-2^-n=-1)

注:此时补码尾数规格化后的表示范围刚好是原码范围的反码形式(方便计算机判断是否规格化)

原码:1.1000 ->1.1111 (-1/2 -> -(1-2^-n)

反码:1.0111 -> 1.0000 (-1/2 -> -1+2^-n)

补码:1.1110 -> 1.0111(计算机能很方便进行规格化) -> 1.0001->1.0000

(-1/2-2^-n -> -1 )

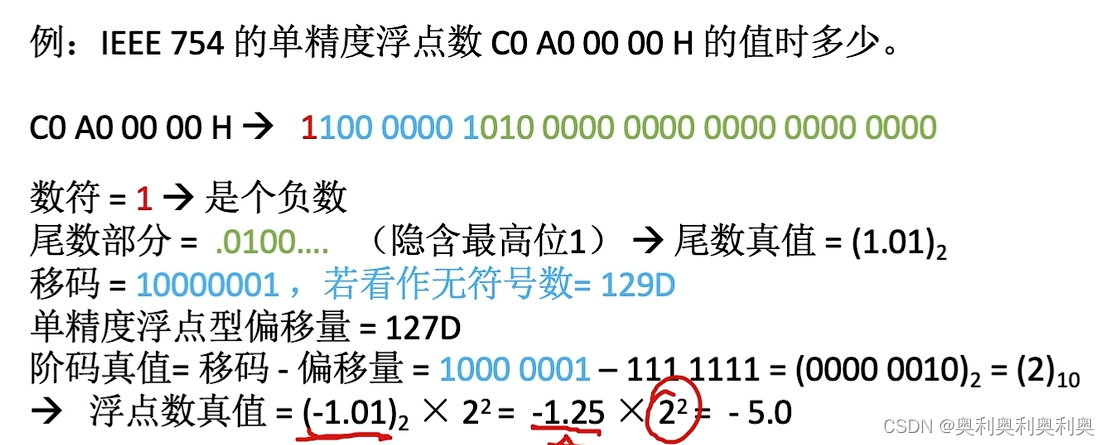

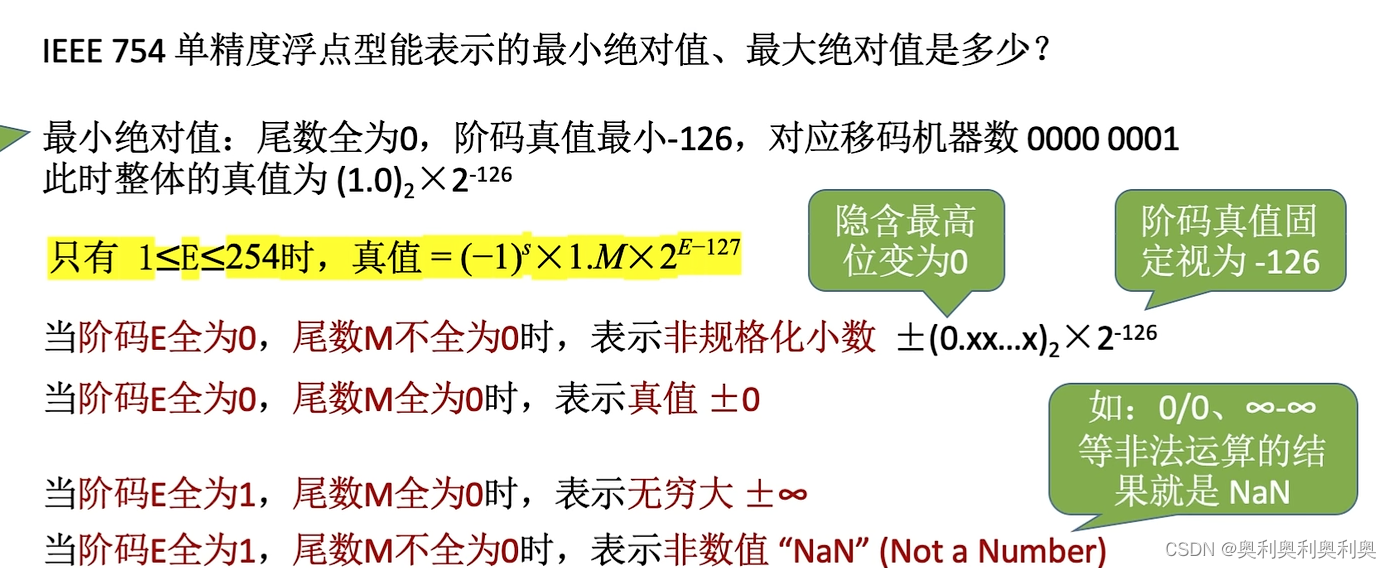

4. 浮点数标准IEEE754(年年考)

(1)移码 = (真值+偏置值)mod2^n(默认2^n-1,可变)

(2)IEEE754标准:ms(数符) + E(阶码) + M(尾数数值位)

a. E(阶码):

偏置值 = 2^n-1 - 1

使得(-2^ n-1 )为全1,(-2^ n-1 )+1 为全0,

正常表示范围剔除这两个最小值((-2^ n-1 )+2~2^ n-1)

b. ms(数符):表示正负号

c. M(尾数数值位):用原码表示(只代表数值,无需补码)

隐藏最高位的1(见2.浮点数的规格化),表示尾数1.M

以float为例:ms E M长度为1 8 23,规格化的短浮点数的真值为

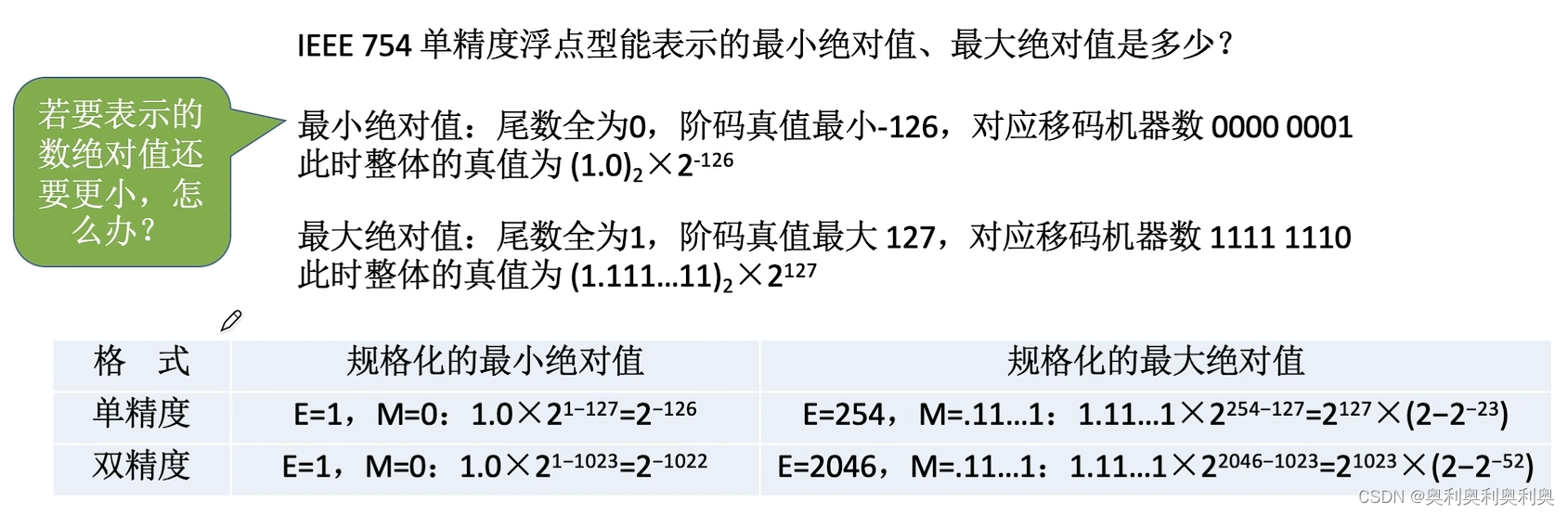

(3)三种浮点数的格式

总位数 Ms E M E移码偏置值 float(单精度浮点数) 32 1 8 23 127 double(双精度浮点数) 64 1 11 52 1023 (1) 转化:IEEE754

(2)表示的范围

a. 规格化小数

b. 非规格化小数和溢出表示、NaN

5. 浮点数的计算

(1)过程:

1⃣️对阶:小阶对大阶,大数变小数(方便计算机实现)

2⃣️尾数加减

3⃣️规格化:左右规

4⃣️舍入:1. 0舍1入法、2.恒置1法

有的机器会把浮点数的尾数单独才拆出去运算,结果舍入后再拼回

5⃣️判断溢出:尾数溢出可处理

(2)例题:

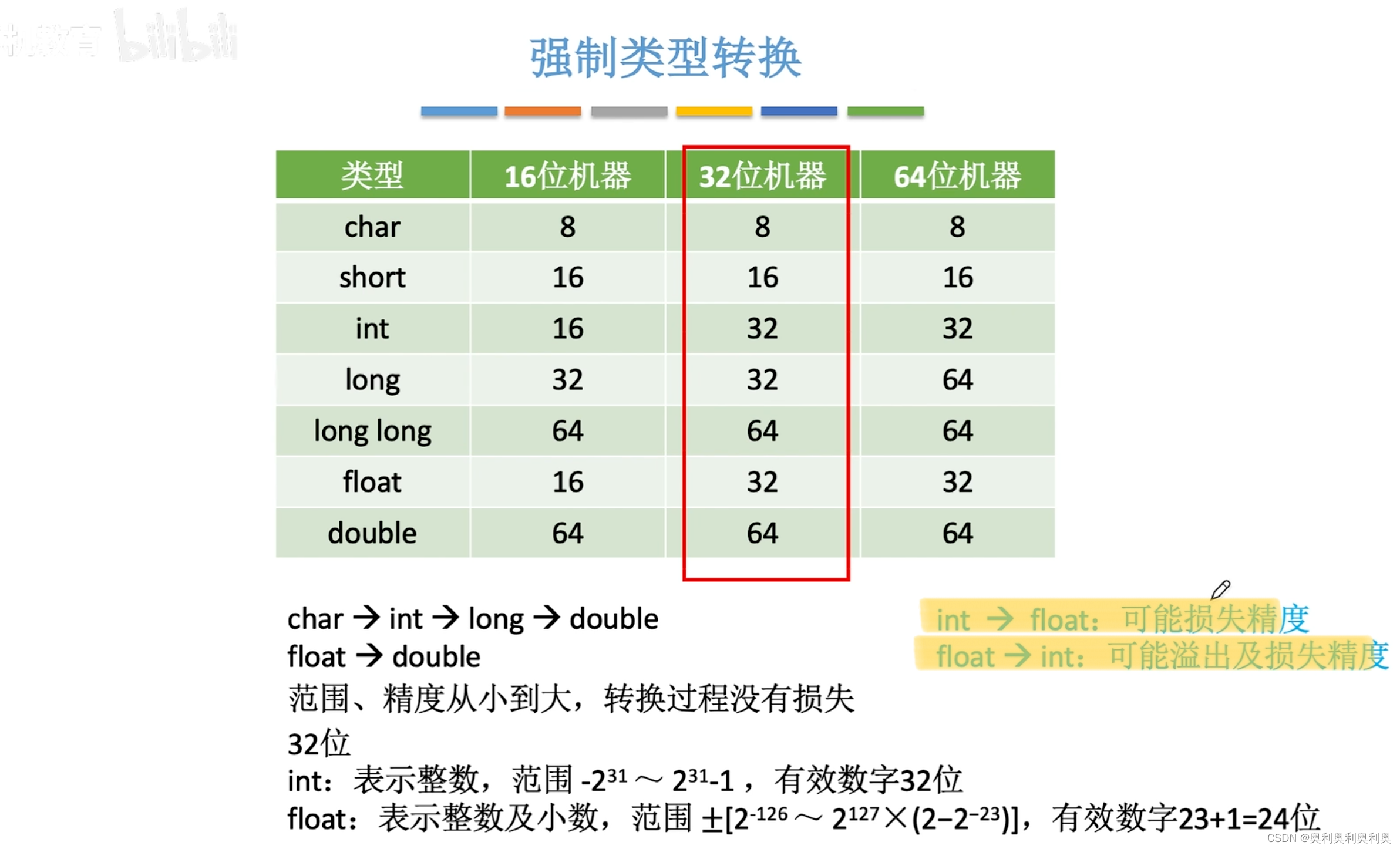

(3)强制类型转换

32位机器位数 64位机器位数 char 8 8 short 16 16 int 32 32 float 32 32 long ‘32’ 64 double 64 64 long long 64 64

a. 无损转换:char->short->int->long->double float->double

b. int(32)->float(8+24) 可能会损失精度

float->int 损失小数部分精度,可能溢出(2^127->2^32)

1161

1161

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?