一、实验任务一

实现一个测试过程,该过程包括启动准备状态、启动测试、停止测试、查询测试结果、显示测试结果、测试结束返回初始化6个状态;用时间来控制该过程,90秒内完成该过程.

1.创建项目

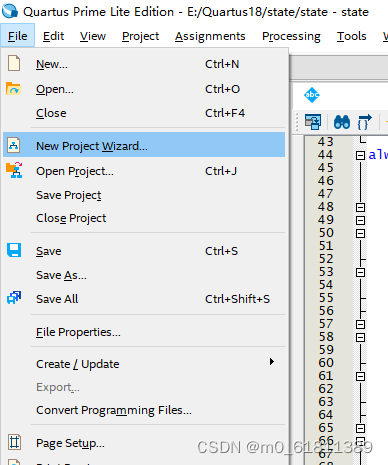

(1).点击File->New Project Wizard

(2).填写项目名称

(3).一直next到Family, Device & Board Settings

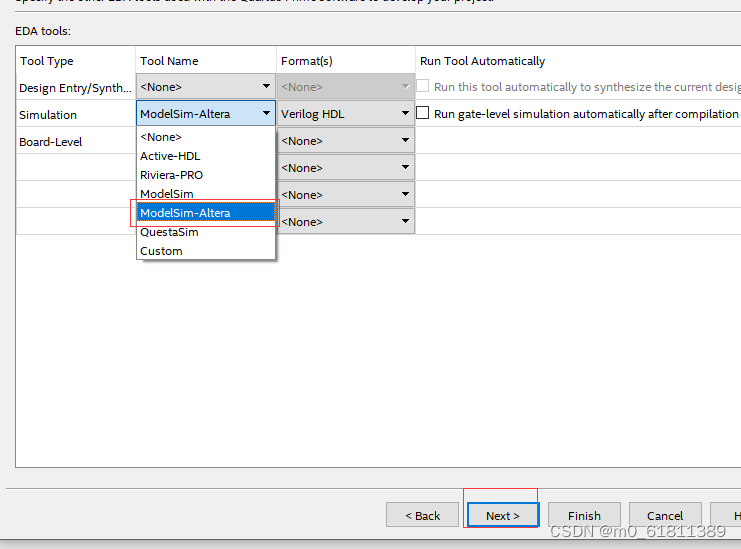

(4).选择ModelSim-Altera

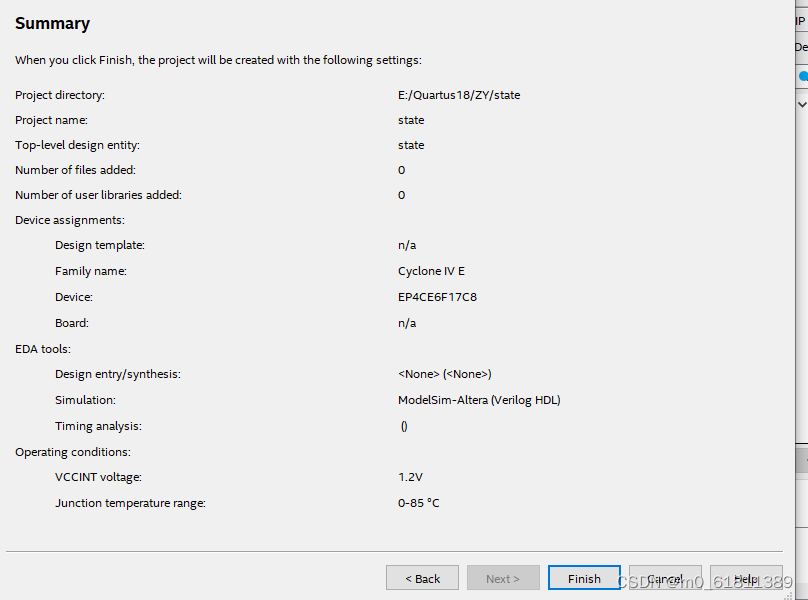

(5).点击finish

2.代码部分

(1).

module state(

input wire clk,

input wire rst_n,

output reg [3:0] led

);

parameter TIME_NUM=89;//90s

parameter MAX_NUM = 26'd49_999_999;//1s

reg [25:0] cnt;//1s计数器

reg [6:0] time_cnt;//90s计数器

reg [2:0] state;//当前状态

parameter ready = 0; // 准备状态,经过20s,led不亮

parameter start_s = 1; // 启动测试状态, 再经过20s,led0亮

parameter stop_s = 2; // 停止测试状态, 再经过10s,led1亮

parameter find_s = 3; // 查询测试结果状态, 再经过20s,led2亮

parameter dis_s = 4; // 显示测试结果状态, 再经过10s,led3亮

parameter fin_s = 5; // 测试结束状态, 再经过10s,led全亮

always@(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt <= 26'd0;

time_cnt <= 7'd0;

end

else if(cnt == MAX_NUM)begin

cnt <= 26'd0;

if(time_cnt == TIME_NUM)begin

time_cnt <= 7'd0;

end

else begin

time_cnt <= time_cnt + 1'b1;

end

end

else begin

cnt <= cnt + 1'd1;

end

end

always@(posedge clk or negedge rst_n)begin

if(!rst_n)

state <= ready;

else

case(state)

ready:begin//inital

if(time_cnt == 19)begin

state <= start_s;

end

else begin

state <= ready;

end

end

start_s:begin//ready

if(time_cnt == 39)begin

state = stop_s;

end

else begin

state <= state;

end

end

stop_s:begin//start

if(time_cnt ==

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

587

587

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?