目录

3.1.1 Write Enable (WREN) (06h)

3.1.2 Write Disable (WRDI) (04h)

3.1.3 Write Enable for Volatile Status Register (50h)

3.1.4 Read Status Register (RDSR) (05h or 35h or 15h)

3.1.5 Write Status Register (WRSR) (01h or 31h or 11h)

3.2.3 Dual Output Fast Read (3Bh)

3.2.4 Dual I/O Fast Read (BBh)

3.3.5 Quad Output First Read (6Bh)

3.2.6 Quad I/O Fast Read (EBh)

3.3.7 Quad I/O Word Read (E7h)

3.2.9 Continuous Read Mode Reset (CRMR) (FFH)

3.2.10 Set Burst with Wrap (77h)

3.2.11 High Performance Mode (HPM) (A3h)

3.3.2 Fast Page Program (FPP) (F2h)

3.3.3 Dual Input Page Program (A2H)

3.4.1 0.5KB Sector Erase (SE05K) (8AH)

3.5.2 Read Manufacture ID /Device ID (REMS) (90h)

3.5.3 Dual I/O Read Manufacture ID /Device ID (92h)

3.5.4 Quad I/O Read Manufacture ID /Device ID (94h)

3.5.5 Read Identification (RDID) (9Fh)

3.5.6 Release from Deep Power down or High Performance Mode and Read Device ID(RDI) (ABh)

3.5.7 Release from Deep Power down or High Performance Mode and Read Device ID(RDI) (ABh)

3.5.8 Deep Power-Down (DPD) (B9h)

3.5.9 Read Serial Flash Discoverable Parameter (5Ah)

3.6.1 Read Security Register (48h)

3.6.2 Program Security Register (42h)

3.6.3 Erase Security Register (44h)

3.7.1 Enable Reset (66h) and Software Reset (99h)

3.8.1 Program/Erase Suspend(PES) (75h)

3.8.2 Program/Erase Resume(PER) (7Ah)

一、工艺

NOR Flash工艺一般有以下三种:

ETOX:技术源于Intel,采用的是浮栅隧穿技术,缺点主要是编程擦除时间长,光罩层次多达35层,外围电路占空间大,晶元面积有效利用率低,功耗高等,因此成本高。

工艺尺寸:55-65nm;适用于大容量。由于热电子效应对物理长度的限制导致沟道尺寸较难进一步缩小,因此向 4Xnm 制程迭代具备一定难度。

SONOS:技术源于Cypress,虽然光罩层次24-26层,擦写时间短,但因为原材料采用氮化硅,在高温下易丢失数据,可靠性低,一般应用于小容量产品,且工作温度不超过85度。

工艺尺寸:40-55nm;适用于小容量。

NORD:技术完全国内自主技术,结构上类似两个ETOX组合,光罩层次24-26层,擦写速度快,晶元面积有效利用率高,因此可以在采用90nm制程的情况下,同样大容量的芯片完全可以做与40nmETOX芯片相同尺寸,甚至更小,且不受国外技术壁垒限制。在擦除次数上,可达到20万次,完全超过ETOX和SONOS的10万次。工作温度-40度到125度,完全满足车规级要求,稳定性好。

工艺尺寸:40-55nm;适用于小容量,介于以上两者之间

二、结构及参数

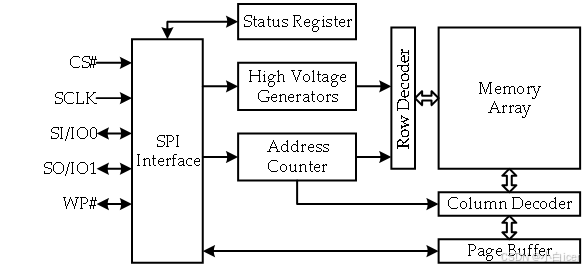

Nor Flash 基本结构如下,通过spi接口进行数据传输,spi接口知识参考链接SPI 及 NOR Flash 介绍_spi nor flash-CSDN博客。

参数如下:

- 电压:1.65v - 3.6V

- 标准spi:SCLK、CS#、DI、DO、WP#

- Dual spi:SCLK、CS#、DI、DO、WP#

- Quad spi:SCLK、CS#、DI、DO、WP#、HPLD#

- Software Reset

- Software and Hardware Protect

- Power Supply Lock-Down and OTP protection

- Top/Bottom complement array protection

- 128bit Unique ID

- SFDP

- 支持Continuous Read

- 3个OTP:3x512byte security registers (fuse array)

- 0.5KB/4KB/32KB/64KB/Chip

- 超过10万次的擦除和编程

- 超过20年的数据保护

- 10uA typical standby current

三、指令

这些指令通过SPI总线控制,指令在CS#下降沿启动,CS#拉高前结束,这些指令通过SPI总线控制,最高有效位(MSB)优先,当存储器被编程或擦除时,或者当状态寄存器被写入时,除了读取状态寄存器之外的所有指令将被忽略,直到编程或擦除周期完成。

3.1 Satus Register

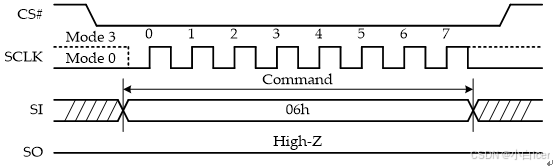

3.1.1 Write Enable (WREN) (06h)

写入启用指令将状态寄存器中的写入启用锁存器(WEL)位设置为1。写状态寄存器(01h,31h,11h)、编程(02h,f2h,a2h,32h)、擦除(8ah,20h,52h,d8h,c7h,60h)、编程安全寄存器(42h)、擦除安全寄存器(44h)。这些指令若不设置WEL为,设备会忽略这些指令。

Drice CS# low --> Send 06h command into SI pin -->Drive CS# high

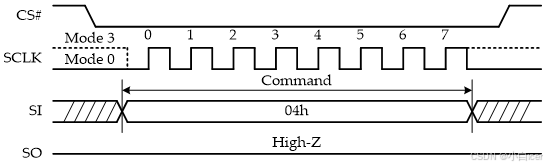

3.1.2 Write Disable (WRDI) (04h)

写入禁用指令重置状态寄存器中的写入启用锁存器(WEL)位到0。通过驱动CS#低电平,将指令代码“04h”移入DI引脚,然后驱动CS#为高电平。

WEL位复位:Power up、04h、WRSR完成、Program完成、Erase完成、42h/44h完成、66h+99h软复位。

Drice CS# low --> Send 04h command into SI pin -->Drive CS# high

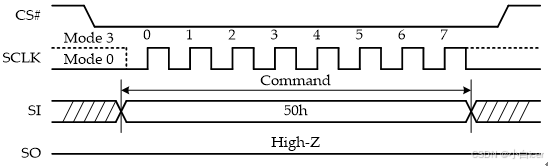

3.1.3 Write Enable for Volatile Status Register (50h)

非易失性状态寄存器位也可以作为易失性位写入。这为更改提供了更大的灵活性系统配置和存储器保护方案,而无需等待典型的非易失性位写入周期或影响状态寄存器非易失性位的耐久性。易失性状态寄存器的写入启用命令必须在写入状态寄存器命令之前发出,并且不能在它们之间插入任何其他命令。否则,易失性状态寄存器的写入启用将被清除。易失性状态寄存器的写入启用命令不会设置写入启用锁存位WEL,它仅对写入状态寄存器命令更改易失性状态有效寄存器位值。

Drice CS# low --> Send 50h command into SI pin -->Drive CS# high

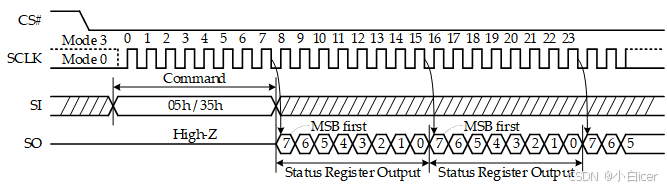

3.1.4 Read Status Register (RDSR) (05h or 35h or 15h)

RDSR命令使主机能够读出状态寄存器。这个命令可以在任何时候发出。即使WRSR、Program、Erase正在进行中。建议设备发出下一个命令之前检查WIP位。命令通过05h、35h、15h分别读取SR1(S7-S0)、SR2(S15-S8)、SR3(S23-S16)。

Drice CS# low --> Send RDSR command into SI pin --> Receive output data on SO pin --> Drive CS# high

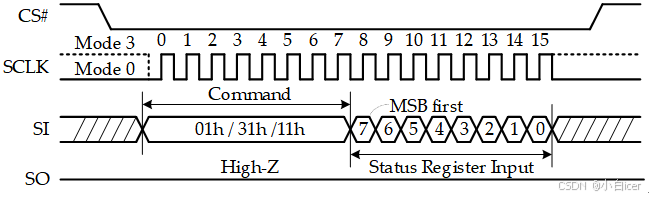

3.1.5 Write Status Register (WRSR) (01h or 31h or 11h)

WRSR命令用来修改状态寄存器的值。在发送WRSR之前,必须设置WEL位。在状态寄存器中,只读位和保留位不受WRSR的影响。写入启用后,通过将CS#驱动到低位来输入指令,发送指令代码“01h”,然后写入状态寄存器数据Byte。

Drice CS# low --> Send WRSR command into SI pin --> Send write data into SI pin --> Drive CS# high

3.2 Read

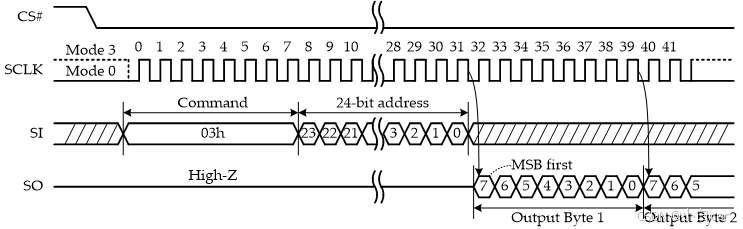

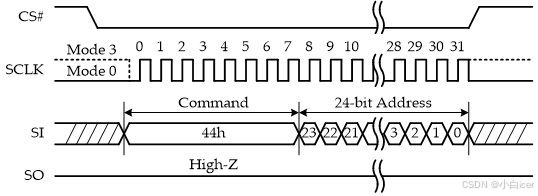

3.2.1 Read (03h)

读取数据指令允许从存储器中顺序读取一个以上的数据字节。这个通过将CS#引脚驱动为低电平,然后将指令代码“03h”后接24位地址(A23-A0)输入DI引脚。指令和地址位在CLK的上升沿被锁存,在接收到地址后,被寻址存储器位置的数据Byte将在DO引脚位于SCLK的下降沿,最高有效位(MSB)在前。地址是自动的在每个字节的数据被移出后递增到下一个更高的地址,从而允许连续的流数据。这意味着整个存储器可以用一条与时钟一样长的指令访问继续。该指令是通过驱动CS#为高电平来完成的。如果在擦除、编程或写入周期正在进行(BUSY=1),指令被忽略,不会有任何对当前周期的影响。03h序列如下:

Drice CS# low --> shift in 03h command --> Shift in 24bit address --> Shift out data --> Drive CS# high

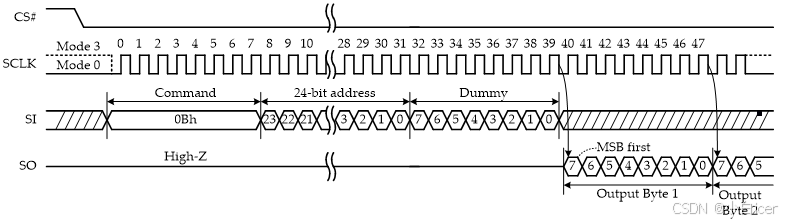

3.2.2 Fast Read (0Bh)

快速读取指令与读取数据指令类似,不同之处它可以在最高频率下读数据,这是通过添加8个dummy clk来实现的24位地址后的时钟。dummy时钟允许设备内部电路用于设置初始地址的额外时间。在dummy时钟期间,DI引脚上的数据值为“不在乎”。指令和地址锁存在SCLK的上升沿,数据输出在SCLK的下降沿以最高的时钟频率。0Bh指令序列如:

Drice CS# low --> shift in 0Bh command --> Shift in 24bit address --> Shift in dummy byte --> Shift out data --> Drive CS# high

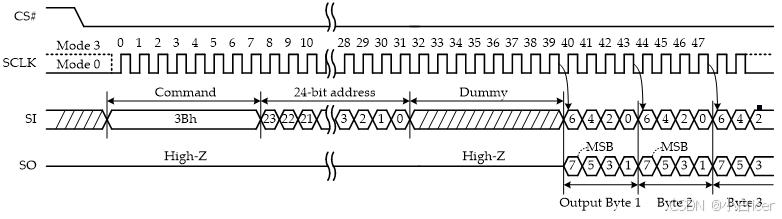

3.2.3 Dual Output Fast Read (3Bh)

快速读取双输出(3Bh)指令类似于标准快速读取(0Bh)的指令,除了数据在两个引脚DO和DI上输出,而不仅仅是DO。速率是标准SPI设备的两倍。快速读取双输出指令非常适合上电后快速将代码从Flash下载到RAM,或用于缓存代码段的应用程序用于执行的RAM。与快速读取指令类似,快速读取双输出指令可以在最高FR的可能频率(见AC特性)。这是通过添加八个“dummy”来实现的24位地址后的时钟。伪时钟允许设备的内部电路用于设置初始地址的额外时间。伪时钟期间的输入数据是“不在乎”。3Bh指令序列如下:

Drice CS# low --> shift in 3Bh command --> Shift in 24bit address --> Shift in dummy byte --> Shift out data dual I/O --> Drive CS# high

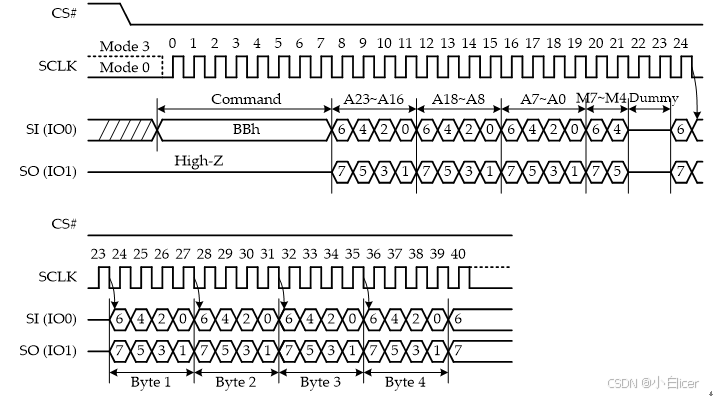

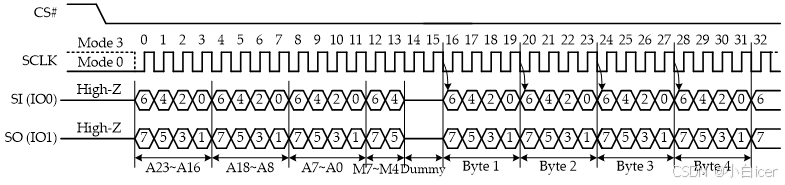

3.2.4 Dual I/O Fast Read (BBh)

快速读取双I/O(BBh)指令允许在保持两个IO的同时改进随机访问引脚IO0和IO1。它类似于快速读取双输出(3Bh)指令,但具有输入功能地址位(A23-0)每两位。这种减少的指令开销可以允许代码执行(XIP)。具有“连续读取模式”的快速读取双I/O快速读取双I/O指令可以通过设置输入地址位(A23-0)后的“连续读取模式”位(M7-0)。然而IO引脚应当在第一数据输出时钟的下降沿之前具有高阻抗。如果“连续读取模式”位(M7-0)是AXH以外的任何值,下一个命令需要第一个BBH命令代码,从而恢复正常操作。BBh指令的序列如下:

Drice CS# low --> shift in BBh command --> Shift in 24bit address dual I/O --> Shift in dummy byte dual I/O --> Shift out data dual I/O --> Drive CS# high

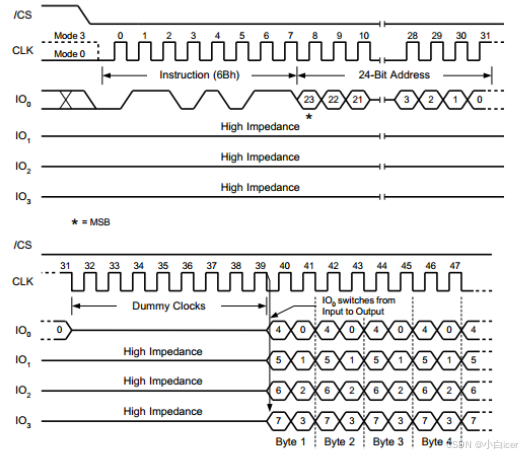

3.3.5 Quad Output First Read (6Bh)

6Bh命令后跟着3byte地址和8个dummy clk,通过四个pin IO3,IO2,IO2,IO0输出数据在每个SCLK的上升沿。第一个地址可以在主存储阵列的任意位置,它会自动递增地址输出数据。QE位必须在6Bh指令之前设置。在执行6Bh命令时,SI是一个双向IO,它首先充当命令和地址的输入,然后成为读数据的输出。6Bh指令序列如:

Drice CS# low --> shift in 6Bh command --> Shift in 24bit address --> Shift in dummy byte --> Shift out data quad I/O --> Drive CS# high

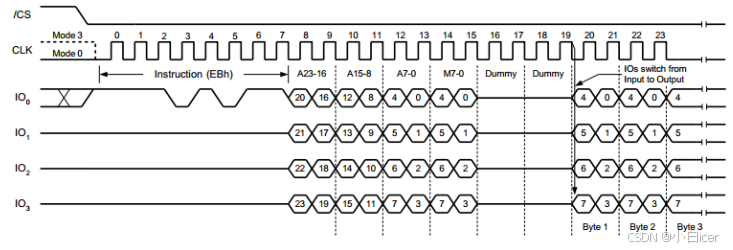

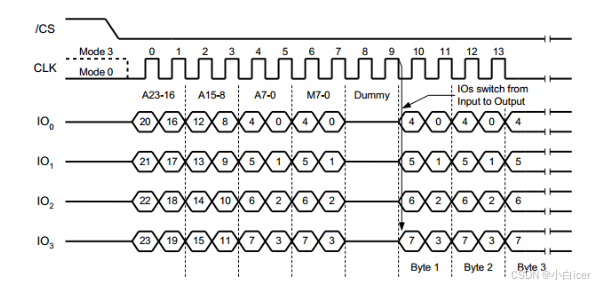

3.2.6 Quad I/O Fast Read (EBh)

EBh命令类似于BBh命令,除了它使用四个数据引脚用于地址传输,连续读取模式位输入,虚拟位和所有的输出数据字节。4个数据引脚的使用极大地提高了IO效率,并允许XIP模式更快的随机访问,这使得主机可以直接从闪存执行,而无需先将代码复制到RAM中。在执行EBh命令之前,必须设置QE为1。EBh指令的序列如下:

Drice CS# low --> shift in EBh command --> Shift in 24bit address quad I/O --> Shift in dummy byte quad I/O --> Shift out data quda I/O --> Drive CS# high

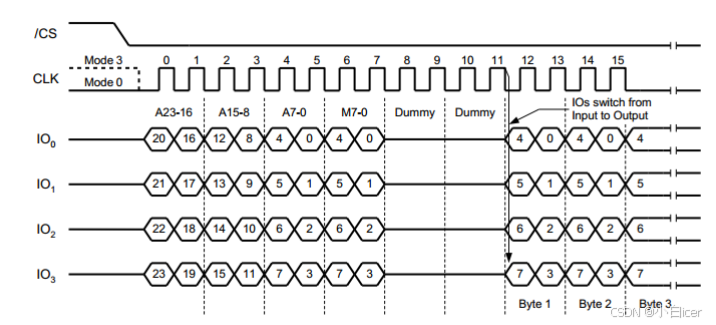

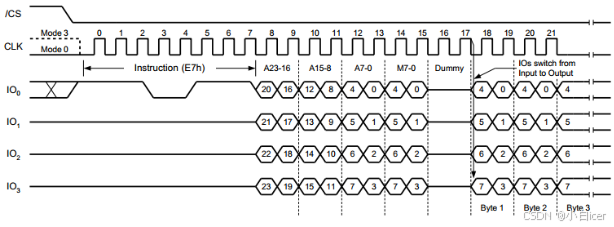

3.3.7 Quad I/O Word Read (E7h)

E7h类似于EBh命令,不同之处在于最低地址位A0必须为0,并且只有两个虚拟时钟。第一个地址可以指向主阵列的任意位置。每输出一个字节后,地址自动递增到下一个字节地址。该命令必须设置QE位。E7h指令的序列如下:

Drice CS# low --> shift in E7h command --> Shift in 24bit address quad I/O --> Shift in dummy byte quad I/O --> Shift out data quda I/O --> Drive CS# high

3.2.8 Continuous Read Mode

设置Mode进入持续读模式。

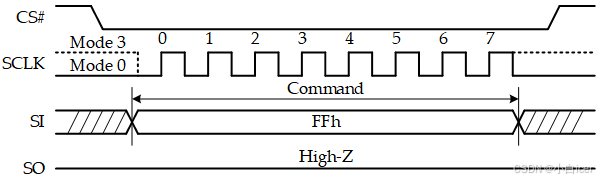

3.2.9 Continuous Read Mode Reset (CRMR) (FFH)

双/四路I/O快速读取操作,“连续读取模式”位(M7-0)实现为进一步减少了命令开销。通过将(M7-0)设置为AXH,下一个双I/O快速读取操作不需要BBH命令代码。

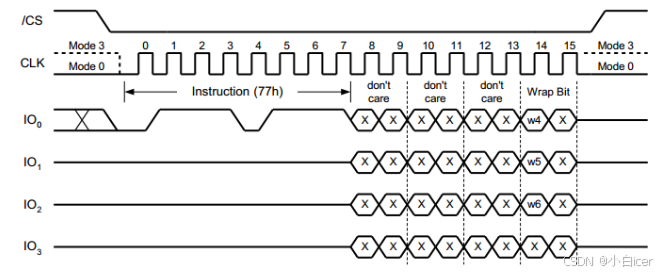

3.2.10 Set Burst with Wrap (77h)

在标准SPI模式下,Set Burst with Wrap(77h)指令与“Fast Read Quad I / O (EBh)”和“Word Read Quad I / O (E7h) ” 指令一起使用,以访问256字节页面内固定长度的8/16/32/64 。某些应用程序可以从此功能中受益,并提高整体系统代码执行性能。

Set Burst with Wrap 77h命令允许设置三个Wrap bits 即W4到W6。当77h和EBh或E7h命令一起使用时,W4、W5、W6某些组合使能使得EBh/E7h可以访问256bytes访问固定长度8、16、32、64字节部分,直到下一次上电。W6-W4位复位:

- Power up;

- Software Reset (66h+99h)Command;

- Another 77h command that resets W4,W5和W6位

| W6,W5 | W4=0 | W4=1(default) | ||

| wrap around | wrap length | wrap around | wrap length | |

| 0,0 | Yes | 8-byte | No | N/A |

| 0,1 | Yes | 16-byte | No | N/A |

| 1,0 | Yes | 32-byte | No | N/A |

| 1,1 | Yes | 64-byte | No | N/A |

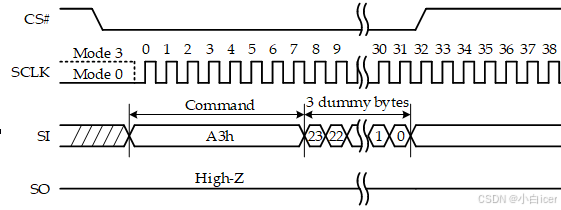

3.2.11 High Performance Mode (HPM) (A3h)

HPM命令允许双I/O和四I/O命令在最高的频率下操作,它可以实现内部补充电泵的预充电,并以更高的功耗为代价使电压随时可用。命令序列为:

Drice CS# low --> Send A3h command opcode --> shift in three dummy bytes --> Drive CS# high

执行HPM命令后,延迟tHPM (20us) 后设备进入高性能模式,该模式下设备的待机电流略高。释放深度下电或HPM(ABh)命令用来将设备从HPM模式下释放,进入待机模式。深度下电命令(B9h)用来将设备从HPM模式下释放出来,进入深度下电模式。

3.3 Program

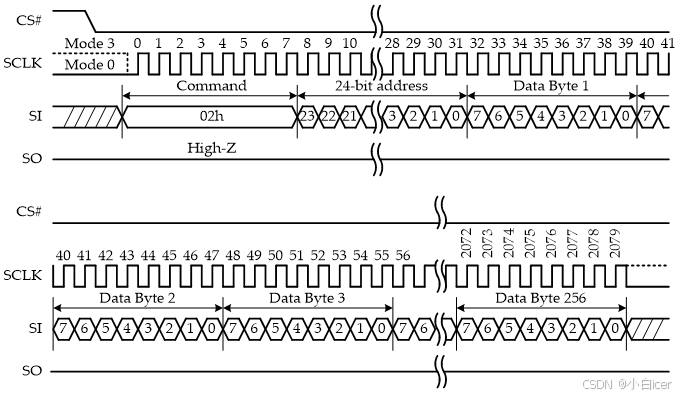

3.3.1 Program (02h)

页面编程指令允许在先前擦除时对多达256字节的数据进行编程所有1。在设备接受页面编程指令(状态寄存器位WEL必须等于1)。该指令通过驱动CS#引脚为低,然后移位指令代码“02h”,后面跟着一个24位地址(A23-A0)和至少一个数据字节输入DI引脚。

如果要对整个256字节页面进行编程,则最后一个地址字节(8个最低有效地址位)后应设置为0。如果最后一个地址Byte不为零,并且时钟数超过剩余页面长度,寻址将换行到页面的开头。在某些情况下,小于256字节(部分页面)可以被编程,而不会对同一页面内的其他字节产生任何影响。一个条件执行部分页面程序的时钟数不能超过剩余的页面长度。如果发送到设备的字节数超过256byte,寻址将换行到页面的开头并覆盖之前发送的数据。与写入和擦除指令一样,CS#引脚必须在最后一个的第八位之后被驱动为高电平字节已被锁定。如果不这样做,页面程序指令将不会执行。CS#之后如果驱动为高电平,则自定时的页面程序指令将在tpp的持续时间内开始。当页面编程周期正在进行时,读取状态寄存器指令可能仍然以便检查BUSY位的状态。在页面编程周期中,BUSY位为1,并且当循环结束并且设备准备再次接受其他指令时变为0。在页面编程周期已结束,状态寄存器中的写使能锁存(WEL)位被清除为0。

3.3.2 Fast Page Program (FPP) (F2h)

快速编程指令编程数据的时候会指定主阵列的指定区域,最大编程数量256byte,WEL位必须使能当设备在编程数据时,试图对先前已编程但未擦除的存储器位置进行编程可能会损坏数据。F2h指令序列如下:

Drice CS# low --> Send in F2h opcode --> Send address --> Send address -->Drive CS# high

F2h命令中指定的地址为编程的起始地址,这个地址指向主阵列的任意位置,主机可以发送任意数量的数据,当地址指向当前页面的结束边界时,它会自动滚回到这个页面的起始边界,因此,快速编程所有的数据字节都落在单个256byte页面中,如果发送到设备的数据超过256byte,则只有最后256bye字节生效,之前所有锁存的数据被丢弃。如果发送的数据少于256byte,则可以在目标地址正确编程,而不会影响同一页面中其他字节。当CS#被驱动高时,一个自定时页面程序周期被启动,当页面编程进行时,建议持续检查状态寄存器WIP位,编程周期完成后,WIP位复位为0。

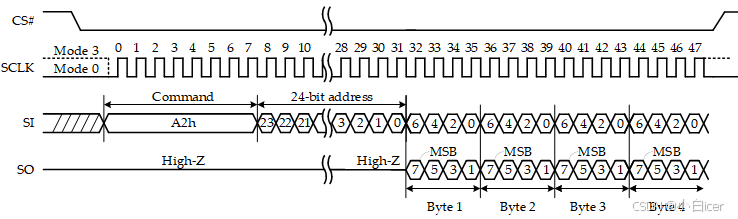

3.3.3 Dual Input Page Program (A2H)

双输入页面编程命令用于使用两个引脚对主存储阵列进行编程:IO0、IO1。写入启用(WREN)命令必须事先执行,以设置写入启用锁存(WEL)位在发送双输入页面程序命令之前。页程序命令由输入在IO上驱动CS#低,然后是命令代码(A2H)、三个地址字节和至少一个数据字节引脚。

如果发送到设备的字节数超过256锁存的数据被丢弃,最后256个数据字节被保证在同一页。如果发送到设备的数据字节少于256,则在请求时对其进行正确编程地址,而不会对同一页的其他字节产生任何影响。CS#必须在最后一个数据Byte的第八位锁存后拉高,双输入页面程序命令不会执行。 一旦CS#被驱动为高电平,自定时双输入页面编程周期(其持续时间为tPP)启动。当双输入页面程序循环正在进行时,可以读取状态寄存器进行检查正在写入(WIP)位的值。在自定时Dual期间,正在写入(WIP)位为1输入页面程序周期,完成时为0。在循环之前的某个未指定时间写入使能锁存器(WEL)位被复位。

3.3.4 Quad Page Program (32h)

32h命令使用四个pin IO0,IO1,IO2,IO3向指定的主存储阵列编程数据,QPP最大编程数据数量是256byte。WEL位必须使能当设备在编程数据时,试图对先前已编程但未擦除的存储器位置进行编程可能会损坏数据。使用32h指令QE位必须设置。32h指令序列如下:

Drice CS# low --> Send in 32h opcode --> Send address --> Send in data,four bit per SCLK cycle -->Drive CS# high

32h命令中指定的地址为编程的起始地址,这个地址指向主阵列的任意位置,主机可以发送任意数量的数据,当地址指向当前页面的结束边界时,它会自动滚回到这个页面的起始边界,因此,快速编程所有的数据字节都落在单个256byte页面中,如果发送到设备的数据超过256byte,则只有最后256bye字节生效,之前所有锁存的数据被丢弃。如果发送的数据少于256byte,则可以在目标地址正确编程,而不会影响同一页面中其他字节。当CS#被驱动高时,一个自定时页面程序周期被启动,当页面编程进行时,建议持续检查状态寄存器WIP位,编程周期完成后,WIP位复位为0。一个32h的命令应用到一个由块保护位(BP4、BP3、BP2、BP1、BP0)保护后不会执行。

3.4 Erase

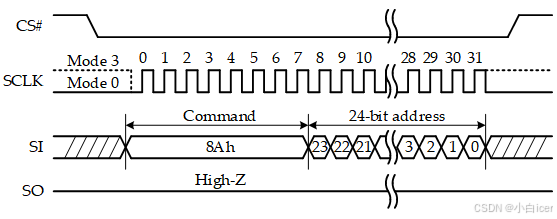

3.4.1 0.5KB Sector Erase (SE05K) (8AH)

扇区擦除0.5K(SE05K)命令用于擦除所选扇区的所有数据,必须事先执行Enable(WREN)命令以设置Write Enable Latch(WEL)位。这个扇区擦除0.5K(SE05K)命令是通过驱动CS#低位输入的,后面跟着命令代码,以及DI上的3地址字节。扇区内的任何地址都是扇区擦除0.5K(SE05K)的有效地址命令CS#必须在整个序列期间被驱动为低电平。

扇区擦除命令序列:CS#变低发送扇区擦除命令3字节地址on DI CS#变高。CS#必须在最后一个地址Byte的第八位已经被锁存;否则扇区擦除0.5K(SE05K)命令为未执行。一旦CS#被驱动为高电平,则自定时扇区擦除周期(其持续时间为tSE)为启动。当扇区擦除周期正在进行时,可以读取状态寄存器以检查正在写入(WIP)位。在自定时扇区擦除周期期间,进行中写入(WIP)位为1,并且当其完成时为0。在循环完成之前的某个未指定时间,写入启用锁存器(WEL)位被复位。扇区擦除0.5K(SE05K)命令应用于受块保护的扇区保护位未执行。

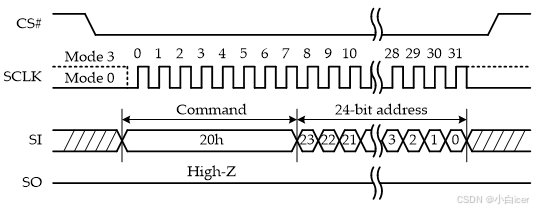

Sector Erase (SE) (20h)

扇区擦除指令将指定扇区(4K字节)内的所有内存设置为全部为1(FFh)。在设备接受扇区擦除之前,必须执行写入启用指令(状态寄存器位WEL必须等于1)。该指令是通过将CS#引脚驱动为低电平和在24位扇区地址(A23-A0)之后移位指令代码“20h”。

最后一个字节的第八位被锁存后,CS#引脚必须被驱动为高电平。如果不这样做扇区擦除指令将不会被执行。在CS#被驱动为高电平时,自定时扇区擦除指令将在tSE的持续时间内开始(参见AC特性)。当扇区擦除周期为在进行中,读取状态寄存器指令仍然可以被访问以检查BUSY位的状态。BUSY位在扇区擦除周期中为1,当周期结束且设备准备再次接受其他指示。扇区擦除周期结束后,写入启用锁存器状态寄存器中的(WEL)位被清除为0。如果寻址页由块保护位保护。

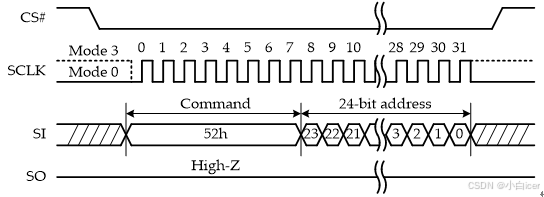

32KB Block Erase (BE) (52h)

块擦除指令将指定块(64K字节)或半块(32K字节)内的所有内存设置为所有1(FFh)的擦除状态。在设备将接受块擦除指令(状态寄存器位WEL必须等于1)。指令由发起将CS#引脚驱动为低电平,并将指令代码“D8h”或“52h”移位到24位块地址之后A23-A0。

最后一个字节的第八位被锁存后,CS#引脚必须被驱动为高电平。如果不这样做块擦除指令将不会被执行。在CS#被驱动为高电平之后,自定时块擦除指令将在tBE的持续时间内开始(见AC交流特性)。块擦除周期处于则仍然可以访问读取状态寄存器指令以检查BUSY位的状态。BUSY位在块擦除周期中为1,当周期结束且设备准备再次接受其他指示。块擦除周期结束后,写入启用锁存器状态寄存器中的(WEL)位被清除为0。如果寻址页由块保护位保护。

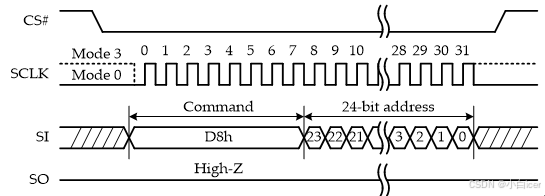

64KB Block Erase (BE) (D8h)

D8h和52h指令相似。

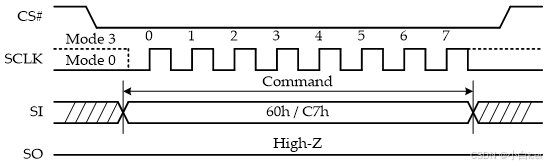

Chip Erase (CE) (60h/C7h)

芯片擦除指令将设备内的所有存储器设置为全部1的擦除状态(FFh),在设备接受芯片擦除指令(状态寄存器)之前,必须执行启用指令位WEL必须等于1。通过将CS#引脚驱动为低电平并移动指令代码来启动指令“C7h”或“60h”。

第八位被锁存后,CS#引脚必须被驱动为高电平。如果不这样做,芯片擦除指令将不会被执行。在CS#被驱动为高电平时,自定时芯片擦除指令将开始持续时间tCE(参见AC交流特性)。当芯片擦除周期正在进行时,读取状态仍然可以访问寄存器指令来检查BUSY位的状态。在芯片擦除周期,完成后变为0,设备准备再次接受其他指令。芯片擦除周期结束后,状态寄存器中的写使能锁存(WEL)位被清除为0。如果任何页面都受到块保护保护。

3.5 ID

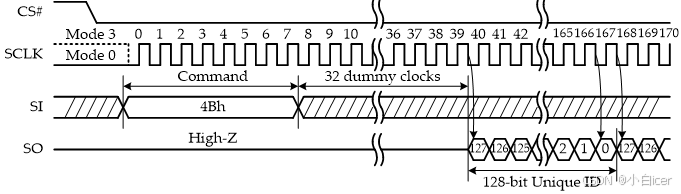

3.5.1 Read Unique ID (4Bh)

读取唯一ID指令访问出厂设置的只读128位唯一编号。ID号可以与用户软件方法结合使用,以帮助防止复制或克隆系统。读取唯一ID指令是通过将CS#引脚驱动为低电平来启动的并将指令代码“4Bh”移位四个字节的伪时钟。指令序列如下:

Drice CS# low --> shift in 4Bh opcode --> Four byte fummy clk -->Drive CS# high

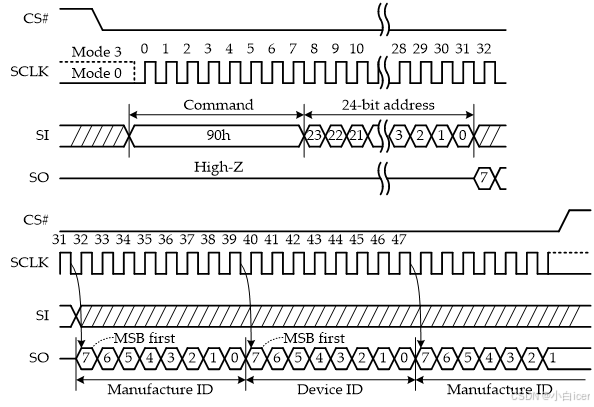

3.5.2 Read Manufacture ID /Device ID (REMS) (90h)

90h命令提供获取制造商和设备ID,如果地址为A0=0,则首先读出制造商ID,如果A0=1,则首先读出设备ID。数据在SCLK上升沿移位出,只要CS为低,两个ID依次移出。命令系列:

Drice CS# low --> shift in 90h opcode --> thress byte address --> Shift out IDs -->Drive CS# high

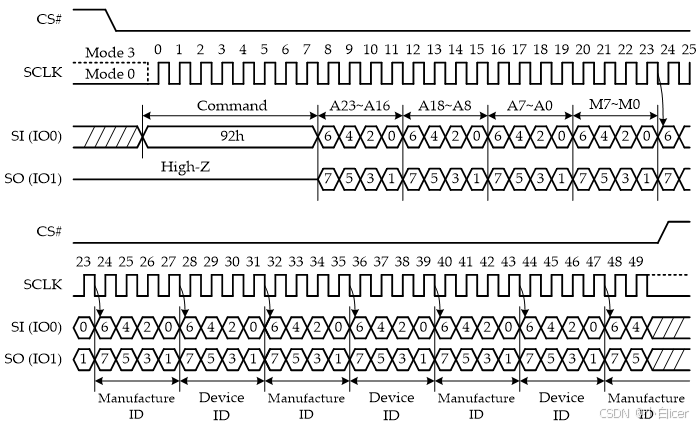

3.5.3 Dual I/O Read Manufacture ID /Device ID (92h)

92h命令输出制造商ID和设备ID,24位地址和8模式位在92h指令之后,如果地址为A0=0,则首先读出制造商ID,如果A0=1,则首先读出设备ID。92h的模式不会使设备进入连续读模式。数据在SCLK上升沿移位出,只要CS为低,两个ID依次移出。92h序列为:

Drice CS# low --> shift in 92h opcode --> thress byte address --> mode--> Shift out IDs -->Drive CS# high

3.5.4 Quad I/O Read Manufacture ID /Device ID (94h)

94h命令输出制造商ID和设备ID,24位地址和8模式位和四个dummy clk 在92h指令之后,如果地址为A0=0,则首先读出制造商ID,如果A0=1,则首先读出设备ID。92h的模式不会使设备进入连续读模式。94h指令前必须首先设置QE位。数据在SCLK上升沿移位出,只要CS为低,两个ID依次移出。92h序列为:

Drice CS# low --> shift in 94h opcode --> thress byte address --> mode--> 4clk dummy --> Shift out IDs -->Drive CS# high

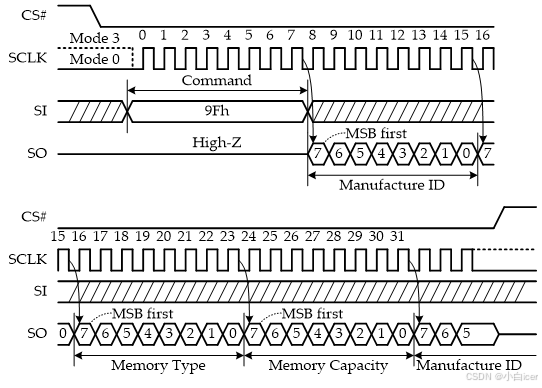

3.5.5 Read Identification (RDID) (9Fh)

9Fh命令输出制造商ID,存储类型和存储能力ID代码,RDID在 WRSR、Program、Erase期间将被忽略。9Fh命令序列:

Drice CS# low --> shift in 9Fh opcode --> Shift out MIDs --> Shift out memory type --> Shift out memory capacity data --> Drive CS# high

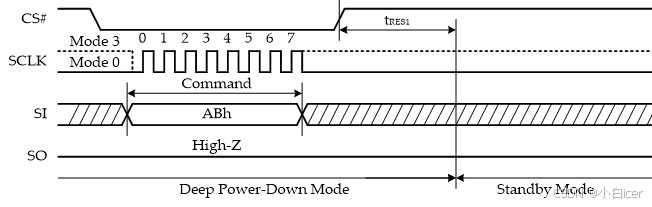

3.5.6 Release from Deep Power down or High Performance Mode and Read Device ID(RDI) (ABh)

当单独发送没有任何dummy 周期,ABh命令会从深度断电模式或者高性能模式释放出来。如果设备处于深度断电模式,ABH结束CS拉高之后持续tRES1时间,如果设备没有处于深度断电模式,则CS解除之后立即进入正常操作。如果ABh在WRSR、Program、Erase期间发出,则该命令无效。

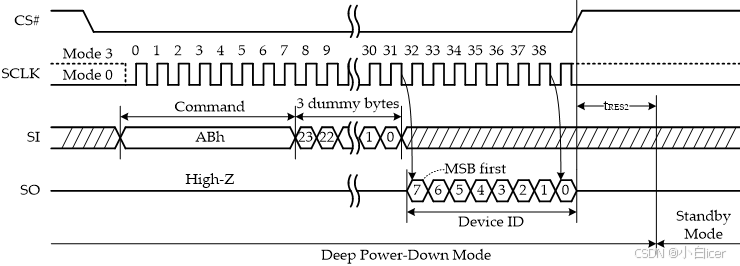

3.5.7 Release from Deep Power down or High Performance Mode and Read Device ID(RDI) (ABh)

如果设备之前处于深度断电模式,ABh可以从深度断电模式释放并获取设备ID,操作码3个dummy byte 和设备ID输出字节,CS拉高必须持续tRES2之后返回到正常模式。如果ABh在WRSR、Program、Eras期间发出,则该命令无效。

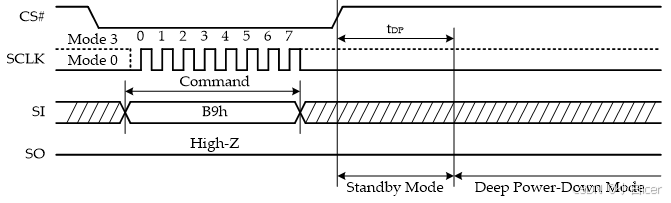

3.5.8 Deep Power-Down (DPD) (B9h)

DPD命令是唯一可以将设备带入到最低功耗模式,深度断电模式,可以减少电流从待机模式Icc1到Icc2,在这种状态,设备忽略除 RDI 指令和 Software Rese 指令所有指令。这个指令提供了额外的软件保护机制,保护设备免受所有的WRSR、Program、Erase。指令序列:

Drice CS# low --> Send in B9h opcode -->Drive CS# high

CS#引脚必须在命令输入的第八位后驱动为高电平,否则操作不会执行。一旦CS#被驱动为高,如果内部没有WRSR、Program、Erase进行,设备首先返回待机模式,经过tDP时间,设备进入深度断电模式,电流功耗大大减少。RDI (ABh)、Soft Reset (66h+99h) 或者下电都可以将DPD释放出来,恢复到待机模式,当WRSR、Program、Erase进行中,DP模式会被忽略。

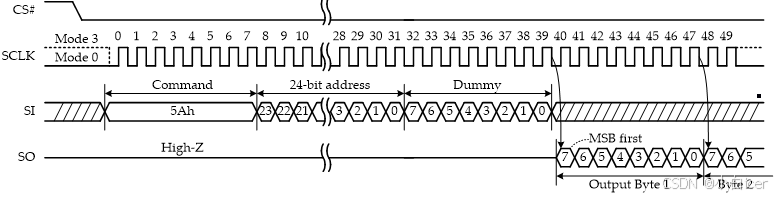

3.5.9 Read Serial Flash Discoverable Parameter (5Ah)

SFDP信息被存储在标准表中,包括了设备的功能和性能参数,主机可以查询这些表进行必要的调整,以适应来自多个供应商的不同功能。

Drice CS# low --> shift in 5Ah opcode --> Shift in thress byte address --> Shift in dummy byte --> Shift out data -->Drive CS# high

3.6 Security Register

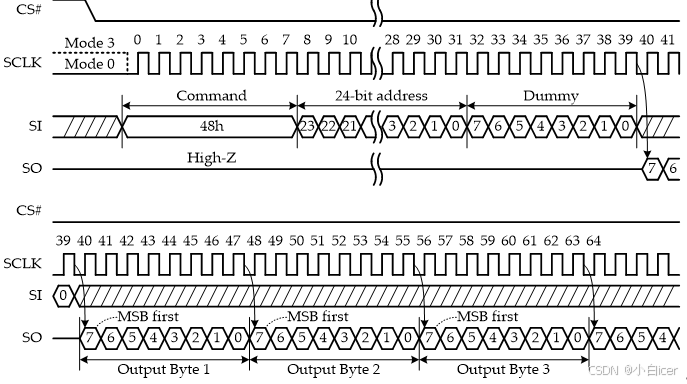

3.6.1 Read Security Register (48h)

读安全寄存器指令和快速读指令相似,输出数据以大频率,首地址可以指向安全寄存器的任意地址,这些地址会依次递增移出,如果到达最后一个字节地址,会回卷到第一个地址。48h指令序列:

Drice CS# low --> shift in 48h command --> Shift in 24bit address --> Shift in dummy byte --> Shift out data --> Drive CS# high

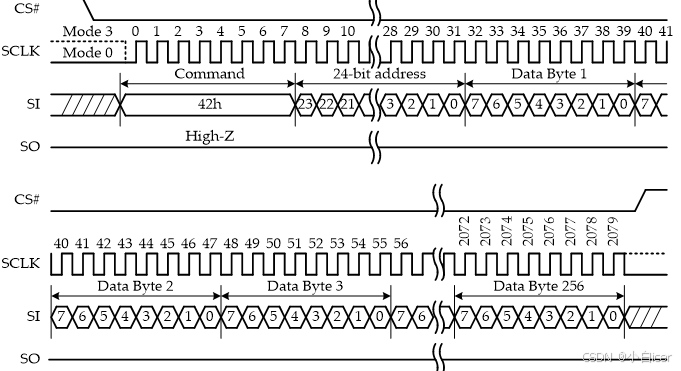

3.6.2 Program Security Register (42h)

编程42h命令向安全寄存器指定区域写数据。WEL位在编程前必须设置,对于先前未擦除区域进行编程可能影响写入数据正确。编程同02要求。42h指令序列如下:

Drice CS# low --> shift in 42h command --> Shift in 24bit address --> Shift in data --> Drive CS# high

3.6.3 Erase Security Register (44h)

三个1024byte安全寄存器可以单独读写擦,主机可以使用安全寄存器可以存储安全或者重要的信息区分于主阵列存储。类似于片擦或者块擦,44h指令擦除前设置WEL位,44h可以擦除3个1024 byte的其中一个安全寄存器。44h指令的序列如下:

Drice CS# low --> shift in 44h command --> Shift in 24bit address --> Drive CS# high

CS#引脚必须在地址输入的最后一位之后驱动为高电平,否则该命令会被设备忽略。当CS#拉高后,开始擦除,在擦除期间WIP为1,擦除介绍后,一段时间后WIP清成0。可以设置LB1、LB2、LB3对每个OTP进行保护,一旦被保护,安全寄存器将不受擦除影响。

3.7 Reset

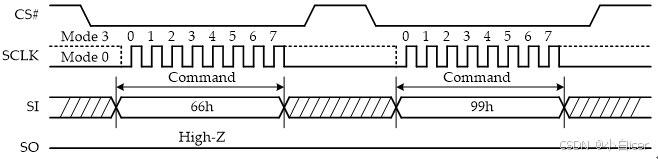

3.7.1 Enable Reset (66h) and Software Reset (99h)

软件复位命令终止所有正在进行的内部操作,并将设备恢复到默认上电状态。所有易失性设置都会丢失,易失性状态寄存器位、WEL、SUS1、SUS2、连续模式设置(M7-M0)和wrap set(w6-w4)位。软件控制的Reset命令通过重新加载volatile将设备恢复到其初始通电状态寄存器的非易失性默认值。如果在擦除、编程或写入过程中启动软件重置寄存器操作该扇区、页面或寄存器中的数据不稳定,操作被中断需要再次启动。

当设备处于深度断电模式时,软件重置命令被忽略,并且没有效应要重置设备,请发送释放断电命令(ABh),并在tRES(20us)持续时间后设备将恢复正常操作,软件重置命令将被接受。如果在Reset命令序列为被设备接受。建议在发出重置之前检查状态寄存器中的BUSY位命令序列。

3.8 Suspend

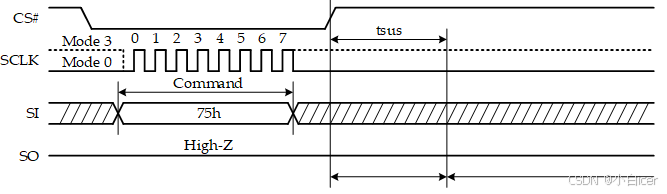

3.8.1 Program/Erase Suspend(PES) (75h)

PES指令仅在page program,sector erase和block erase 指令期间有效,它允许中断/挂起这些操作,可以从其他sector或者block中读取数据,PES指令生效需要Tsus的时间(一般大概20us)。

在pgm suspend期间不允许 WRSR (01h,31h,11h)、Erase/pgm security register(44h/42h)、Erase(20h,52h,d8h,60h,c7h)、pgm(02h,f2h,a2h,32h)。Erase suspend 不允许WRSR (01h,31h,11h)、Erase(20h,52h,d8h,60h,c7h)、44h。

紧接着执行PES指令,WIP位在Tsus期间会由1清成0,并且SUS2或者SUS1位根据挂起操作由0设置为1,在挂起期间执行复位操作会将设备下电并释放挂起状态。

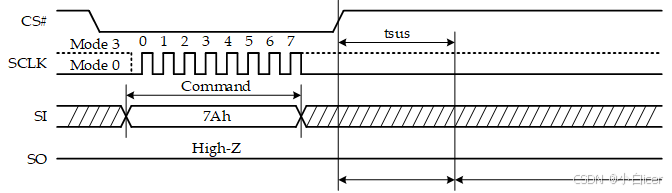

3.8.2 Program/Erase Resume(PER) (7Ah)

当设备处于Program或者Erase 挂起期间,主机可以发出PER指令将设备带出挂起状态,并且恢复先前暂停的program或Erase操作。PER指令要求SUS1或SUS2位为1,WIP=0,在PER指令被接收之后,在200ns之内将SUS1或SUS2清成0,WIP设置为1,表明重新进行Program或Erase操作。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?