目录

为了方便阅读,本文涉及到的寄存器位在文后已做黄色标注。

定时器与外部触发同步请看:http://t.csdn.cn/SQerE

TIMx定时器能够在多种模式下和一个外部的触发同步:复位模式、门控模式和触发模式。

在STM32中,所有TIMx定时器在内部相连,用于定时器同步或链接。当一个定时器处于主模式时,它可以对另一个处于从模式的定时器的计数器进行复位、启动、停止或提供时钟等操作。

使用一个定时器作为另一个定时器的预分频器

如:可以配置定时器1作为定时器2的预分频器。参考图2,进行下述操作:

● 配置定时器1为主模式,它可以在每一个更新事件UEV时输出一个周期性的触发信号。在 TIM1_CR2寄存器的MMS=’010’时,每当产生一个更新事件时在TRGO1上输出一个上升沿信号。

笔记:配置定时器1,让每周期产生一个脉冲,从TRGO1输出。

● 连接定时器1的TRGO1输出至定时器2,设置TIM2_SMCR寄存器的TS=’000’,配置定时器2 为使用ITR1作为内部触发的从模式。

笔记:将定时器1产生的脉冲信号连接到定时器2的内部触发接口,作为定时器2的时钟。

● 然后把从模式控制器置于外部时钟模式1(TIM2_SMCR寄存器的SMS=111);这样定时器2 即可由定时器1周期性的上升沿(即定时器1的计数器溢出)信号驱动。

笔记:设置定时器2的从模式,让其上升沿才计数(即有一个上升沿,计数器计数一次)。

● 最后, 必须设置相应(TIMx_CR1寄存器)的CEN位分别启动两个定时器。

注: 如果OCx已被选中为定时器1的触发输出(MMS=1xx),它的上升沿用于驱动定时器2的计数器。

笔记:上面的例子是从定时器1的TRGO1输出脉冲,注解中说的是用比较输出的接口OCx输出脉冲,具体见图1定时器框图。

使用一个定时器使能另一个定时器

在这个例子中,定时器2的使能由定时器1的输出比较控制。参考图2的连接。

只当定时器1的 OC1REF为高时,定时器2才对分频后的内部时钟计数。两个定时器的时钟频率都是由预分频器 对CK_INT除以3(fCK_CNT=fCK_INT/3)得到。

● 配置定时器1为主模式,送出它的输出比较参考信号(OC1REF)为触发输出(TIM1_CR2寄存 器的MMS=100)

笔记:让定时器1从OC1REF输出信号。

● 配置定时器1的OC1REF波形(TIM1_CCMR1寄存器)

● 配置定时器2从定时器1获得输入触发(TIM2_SMCR寄存器的TS=000)

笔记:定时器2选择内部触发,即将定时器1产生的信号从ITR0接入。

● 配置定时器2为门控模式(TIM2_SMCR寄存器的SMS=101)

笔记:输入为高电平,那么计数器计数;输入为低电平,计数器停止计数。

● 置TIM2_CR1寄存器的CEN=1以使能定时器2

● 置TIM1_CR1寄存器的CEN=1以启动定时器1

注: 定时器2的时钟不与定时器1的时钟同步,这个模式只影响定时器2计数器的使能信号。

在图3的例子中,在定时器2启动之前,它们的计数器和预分频器未被初始化,因此它们从当前的数值开始计数。可以在启动定时器1之前复位2个定时器,使它们从给定的数值开始,即在定时器计数器中写入需要的任意数值。写TIMx_EGR寄存器的UG位即可复位定时器。

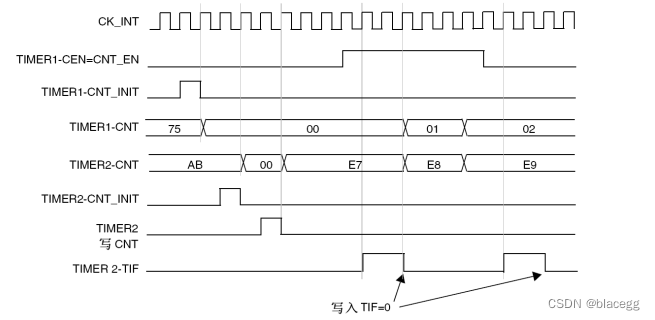

在下一个例子中,需要同步定时器1和定时器2。定时器1是主模式并从0开始,定时器2是从模式并从0xE7开始;2个定时器的预分频器系数相同。写’0’到TIM1_CR1的CEN位将禁止定时器1,定时器2随即停止。

● 配置定时器1为主模式,送出输出比较1参考信号(OC1REF)做为触发输出(TIM1_CR2寄存 器的MMS=100)。

笔记:让定时器1从OC1REF输出信号。

● 配置定时器1的OC1REF波形(TIM1_CCMR1寄存器)。

● 配置定时器2从定时器1获得输入触发(TIM2_SMCR寄存器的TS=000)

笔记:定时器2选择内部触发,即将定时器1产生的信号从ITR0接入。

● 配置定时器2为门控模式(TIM2_SMCR寄存器的SMS=101)

笔记:输入为高电平,那么计数器计数;输入为低电平,计数器停止计数。

● 置TIM1_EGR寄存器的UG=’1’,复位定时器1。

● 置TIM2_EGR寄存器的UG=’1’,复位定时器2。

笔记:使两个定时器的计数器值都复位成0,即从0开始计数。

● 写’0xE7’至定时器2的计数器(TIM2_CNTL),初始化它为0xE7。

笔记:让定时器2从0xE7计数。

● 置TIM2_CR1寄存器的CEN=’1’以使能定时器2。

● 置TIM1_CR1寄存器的CEN=’1’以启动定时器1。

● 置TIM1_CR1寄存器的CEN=’0’以停止定时器1。

使用一个定时器去启动另一个定时器

在这个例子中,使用定时器 1 的更新事件使能定时器2。参考图2的连接。一旦定时器 1 产生更新事件,定时器2即从它当前的数值(可以是非0)按照分频的内部时钟开始计数。在收到触发信号时,定时器2的CEN位被自动地置’1’,同时计数器开始计数直到写’0’到TIM2_CR1寄存器的CEN 位。两个定时器的时钟频率都是由预分频器对CK_INT除以3(fCK_CNT=fCK_INT/3)。

● 配置定时器1为主模式,送出它的更新事件(UEV)为触发输出(TIM1_CR2寄存器的MMS=010) 。

笔记:配置定时器1,让每周期产生一个脉冲,从TRGO1输出。

● 配置定时器1的周期(TIM1_ARR寄存器)。

● 配置定时器2从定时器1获得输入触发(TIM2_SMCR寄存器的TS=000)

笔记:定时器2选择内部触发,即将定时器1产生的信号从ITR0接入。

● 配置定时器2为触发模式(TIM2_SMCR寄存器的SMS=110)

笔记:让定时器2收到上升沿时开启。

● 置TIM1_CR1寄存器的CEN=1以启动定时器1。

在上一个例子中,可以在启动计数之前初始化两个计数器。 图6显示在相同配置情况下,使用触发模式而不是门控模式(TIM2_SMCR寄存器的SMS=110)的动作。

使用一个外部触发同步地启动2个定时器

这个例子中当定时器1的TI1输入上升时使能定时器1,使能定时器1的同时使能定时器2,参见图 2。为保证计数器的对齐,定时器1必须配置为主/从模式(对应TI1为从,对应定时器2为主):

● 配置定时器1为主模式,送出它的使能做为触发输出(TIM1_CR2寄存器的MMS=’001’)。

● 配置定时器1为从模式,从TI1获得输入触发(TIM1_SMCR寄存器的TS=’100’)。

笔记:在定时器1的TI1接一个外部的触发信号。

● 配置定时器1为触发模式(TIM1_SMCR寄存器的SMS=’110’)。

笔记:让定时器1收到上升沿时开启。

● 配置定时器1为主/从模式,TIM1_SMCR寄存器的MSM=’1’。

● 配置定时器2从定时器1获得输入触发(TIM2_SMCR寄存器的TS=000)

● 配置定时器2为触发模式(TIM2_SMCR寄存器的SMS=’110’)。

笔记:让定时器2收到上升沿时开启。

当定时器1的TI1上出现一个上升沿时,两个定时器同步地按照内部时钟开始计数,两个TIF标志 也同时被设置。

注: 在这个例子中,在启动之前两个定时器都被初始化(设置相应的UG位),两个计数器都从0开始, 但可以通过写入任意一个计数器寄存器(TIMx_CNT)在定时器间插入一个偏移。下图中能看到主/ 从模式下在定时器1的CNT_EN和CK_PSC之间有个延迟。

涉及寄存器参考

控制寄存器 1(TIMx_CR1)

偏移地址:0x00

复位值:0x0000

| 位15:10 | 保留,始终读为0。 |

| 位9:8 | CKD[1:0]: 时钟分频因子 (Clock division) 定义在定时器时钟(CK_INT)频率与数字滤波器(ETR,TIx)使用的采样频率之间的分频比例。 00:tDTS = tCK_INT 01:tDTS = 2 x tCK_INT 10:tDTS = 4 x tCK_INT 11:保留 |

| 位7 | ARPE:自动重装载预装载允许位 (Auto-reload preload enable) 0:TIMx_ARR寄存器没有缓冲; 1:TIMx_ARR寄存器被装入缓冲器。 |

| 位6:5 | CMS[1:0]:选择中央对齐模式 (Center-aligned mode selection) 00:边沿对齐模式。计数器依据方向位(DIR)向上或向下计数。 01:中央对齐模式1。计数器交替地向上和向下计数。配置为输出的通道(TIMx_CCMRx寄存器 中CCxS=00)的输出比较中断标志位,只在计数器向下计数时被设置。 10:中央对齐模式2。计数器交替地向上和向下计数。配置为输出的通道(TIMx_CCMRx寄存器 中CCxS=00)的输出比较中断标志位,只在计数器向上计数时被设置。 11:中央对齐模式3。计数器交替地向上和向下计数。配置为输出的通道(TIMx_CCMRx寄存器 中CCxS=00)的输出比较中断标志位,在计数器向上和向下计数时均被设置。 注:在计数器开启时(CEN=1),不允许从边沿对齐模式转换到中央对齐模式。 |

| 位4 | DIR:方向 (Direction) 0:计数器向上计数; 1:计数器向下计数。 注:当计数器配置为中央对齐模式或编码器模式时,该位为只读。 |

| 位3 | OPM:单脉冲模式 (One pulse mode) 0:在发生更新事件时,计数器不停止; 1:在发生下一次更新事件(清除CEN位)时,计数器停止。 |

| 位2 | URS:更新请求源 (Update request source) 软件通过该位选择UEV事件的源 0:如果使能了更新中断或DMA请求,则下述任一事件产生更新中断或DMA请求: − 计数器溢出/下溢 − 设置UG位 − 从模式控制器产生的更新 1:如果使能了更新中断或DMA请求,则只有计数器溢出/下溢才产生更新中断或DMA请求。 |

| 位1 | UDIS:禁止更新 (Update disable) 软件通过该位允许/禁止UEV事件的产生 0:允许UEV。更新(UEV)事件由下述任一事件产生: − 计数器溢出/下溢 − 设置UG位 − 从模式控制器产生的更新具有缓存的寄存器被装入它们的预装载值。(译注:更新影子寄存器) 1:禁止UEV。不产生更新事件,影子寄存器(ARR、PSC、CCRx)保持它们的值。如果设置了 UG位或从模式控制器发出了一个硬件复位,则计数器和预分频器被重新初始化。 |

| 位0 | CEN:使能计数器 0:禁止计数器; 1:使能计数器。 注:在软件设置了CEN位后,外部时钟、门控模式和编码器模式才能工作。 触发模式可以自动地通过硬件设置CEN位。 在单脉冲模式下,当发生更新事件时,CEN被自动清除。 |

控制寄存器 2(TIMx_CR2)

偏移地址:0x04

复位值:0x0000

| 位15:8 | 保留,始终读为0。 |

| 位7 | TI1S:TI1选择 (TI1 selection) 0:TIMx_CH1引脚连到TI1输入; 1:TIMx_CH1、TIMx_CH2和TIMx_CH3引脚经异或后连到TI1输入。 |

| 位6:4 | MMS[2:0]:主模式选择 (Master mode selection) 这3位用于选择在主模式下送到从定时器的同步信息(TRGO)。可能的组合如下: 000:复位 – TIMx_EGR寄存器的UG位被用于作为触发输出(TRGO)。如果是触发输入产生的 复位(从模式控制器处于复位模式),则TRGO上的信号相对实际的复位会有一个延迟。 001:使能 – 计数器使能信号CNT_EN被用于作为触发输出(TRGO)。有时需要在同一时间启动 多个定时器或控制在一段时间内使能从定时器。计数器使能信号是通过CEN控制位和门控模式 下的触发输入信号的逻辑或产生。 当计数器使能信号受控于触发输入时,TRGO上会有一个延迟,除非选择了主/从模式(见 TIMx_SMCR寄存器中MSM位的描述)。 010:更新 – 更新事件被选为触发输入(TRGO)。例如,一个主定时器的时钟可以被用作一个从 定时器的预分频器。 011:比较脉冲 – 在发生一次捕获或一次比较成功时,当要设置CC1IF标志时(即使它已经为 高),触发输出送出一个正脉冲(TRGO)。 100:比较 – OC1REF信号被用于作为触发输出(TRGO)。 101:比较 – OC2REF信号被用于作为触发输出(TRGO)。 110:比较 – OC3REF信号被用于作为触发输出(TRGO)。 111:比较 – OC4REF信号被用于作为触发输出(TRGO)。 |

| 位3 | CCDS:捕获/比较的DMA选择 0:当发生CCx事件时,送出CCx的DMA请求; 1:当发生更新事件时,送出CCx的DMA请求。 |

| 位2:0 | 保留,始终读为0。 |

从模式控制寄存器(TIMx_SMCR)

偏移地址:0x08

复位值:0x0000

| 位15 | ETP:外部触发极性 (External trigger polarity) 该位选择是用ETR还是ETR的反相来作为触发操作 0:ETR不反相,高电平或上升沿有效; 1:ETR被反相,低电平或下降沿有效。 |

| 位14 | ECE:外部时钟使能位 (External clock enable) 该位启用外部时钟模式2 0:禁止外部时钟模式2; 1:使能外部时钟模式2。计数器由ETRF信号上的任意有效边沿驱动。 注1:设置ECE位与选择外部时钟模式1并将TRGI连到ETRF(SMS=111和TS=111)具有相同功 效。 注2:下述从模式可以与外部时钟模式2同时使用:复位模式、门控模式和触发模式;但是,这 时TRGI不能连到ETRF(TS位不能是’111’)。 注3:外部时钟模式1和外部时钟模式2同时被使能时,外部时钟的输入是ETRF。 |

| 位13:12 | ETPS[1:0]:外部触发预分频 (External trigger prescaler) 外部触发信号ETRP的频率必须最多是CK_INT频率的1/4。当输入较快的外部时钟时,可以使 用预分频降低ETRP的频率。 00:关闭预分频; 01:ETRP频率除以2; 10:ETRP频率除以4; 11:ETRP频率除以8。 |

| 位11:8 | ETF[3:0]:外部触发滤波 (External trigger filter) 这些位定义了对ETRP信号采样的频率和对ETRP数字滤波的带宽。实际上,数字滤波器是一个 事件计数器,它记录到N个事件后会产生一个输出的跳变。 0000:无滤波器,以fDTS采样 1000:采样频率fSAMPLING=fDTS/8,N=6 0001:采样频率fSAMPLING=fCK_INT,N=2 1001:采样频率fSAMPLING=fDTS/8,N=8 0010:采样频率fSAMPLING=fCK_INT,N=4 1010:采样频率fSAMPLING=fDTS/16,N=5 0011:采样频率fSAMPLING=fCK_INT,N=8 1011:采样频率fSAMPLING=fDTS/16,N=6 0100:采样频率fSAMPLING=fDTS/2,N=6 1100:采样频率fSAMPLING=fDTS/16,N=8 0101:采样频率fSAMPLING=fDTS/2,N=8 1101:采样频率fSAMPLING=fDTS/32,N=5 0110:采样频率fSAMPLING=fDTS/4,N=6 1110:采样频率fSAMPLING=fDTS/32,N=6 0111:采样频率fSAMPLING=fDTS/4,N=8 1111:采样频率fSAMPLING=fDTS/32,N=8 |

| 位7 | MSM:主/从模式 (Master/slave mode) 0:无作用; 1:触发输入(TRGI)上的事件被延迟了,以允许在当前定时器(通过TRGO)与它的从定时器间的 完美同步。这对要求把几个定时器同步到一个单一的外部事件时是非常有用的。 |

| 位6:4 | TS[2:0]:触发选择 (Trigger selection) 这3位选择用于同步计数器的触发输入。 000:内部触发0(ITR0),TIM1 100:TI1的边沿检测器(TI1F_ED) 001:内部触发1(ITR1),TIM2 101:滤波后的定时器输入1(TI1FP1) 010:内部触发2(ITR2),TIM3 110:滤波后的定时器输入2(TI2FP2) 011:内部触发3(ITR3),TIM4 111:外部触发输入(ETRF) 关于每个定时器中ITRx的细节,参见表1。 注:这些位只能在未用到(如SMS=000)时被改变,以避免在改变时产生错误的边沿检测。 |

| 位3 | 保留,始终读为0。 |

| 位2:0 | SMS[2:0]:从模式选择 (Slave mode selection) 当选择了外部信号,触发信号(TRGI)的有效边沿与选中的外部输入极性相关(见输入控制寄存器 和控制寄存器的说明) 000:关闭从模式 – 如果CEN=1,则预分频器直接由内部时钟驱动。 001:编码器模式1 – 根据TI1FP1的电平,计数器在TI2FP2的边沿向上/下计数。 010:编码器模式2 – 根据TI2FP2的电平,计数器在TI1FP1的边沿向上/下计数。 011:编码器模式3 – 根据另一个信号的输入电平,计数器在TI1FP1和TI2FP2的边沿向上/下计 数。 100:复位模式 – 选中的触发输入(TRGI)的上升沿重新初始化计数器,并且产生一个更新寄存 器的信号。 101:门控模式 – 当触发输入(TRGI)为高时,计数器的时钟开启。一旦触发输入变为低,则计 数器停止(但不复位)。计数器的启动和停止都是受控的。 110:触发模式 – 计数器在触发输入TRGI的上升沿启动(但不复位),只有计数器的启动是受控 的。 111:外部时钟模式1 – 选中的触发输入(TRGI)的上升沿驱动计数器。 注:如果TI1F_EN被选为触发输入(TS=100)时,不要使用门控模式。这是因为,TI1F_ED在每 次TI1F变化时输出一个脉冲,然而门控模式是要检查触发输入的电平。 |

| 从定时器 | ITR0 (TS = 000) | ITR1 (TS = 001) | ITR2 (TS = 010) | ITR3 (TS = 011) |

| TIM2 | TIM1 | TIM8 | TIM3 | TIM4 |

| TIM3 | TIM1 | TIM2 | TIM5 | TIM4 |

| TIM4 | TIM1 | TIM2 | TIM3 | TIM8 |

| TIM5 | TIM2 | TIM3 | TIM4 | TIM8 |

捕获/比较模式寄存器 1(TIMx_CCMR1)

偏移地址:0x18

复位值:0x0000

通道可用于输入(捕获模式)或输出(比较模式),通道的方向由相应的CCxS定义。该寄存器其它 位的作用在输入和输出模式下不同。OCxx描述了通道在输出模式下的功能,ICxx描述了通道在 输出模式下的功能。因此必须注意,同一个位在输出模式和输入模式下的功能是不同的。

| 位15 | OC2CE:输出比较2清0使能 (Output compare 2 clear enable) |

| 位14:12 | OC2M[2:0]:输出比较2模式 (Output compare 2 mode) |

| 位11 | OC2PE:输出比较2预装载使能 (Output compare 2 preload enable) |

| 位10 | OC2FE:输出比较2快速使能 (Output compare 2 fast enable) |

| 位9:8 | CC2S[1:0]:捕获/比较2选择 (Capture/Compare 2 selection) 该位定义通道的方向(输入/输出),及输入脚的选择: 00:CC2通道被配置为输出; 01:CC2通道被配置为输入,IC2映射在TI2上; 10:CC2通道被配置为输入,IC2映射在TI1上; 11:CC2通道被配置为输入,IC2映射在TRC上。此模式仅工作在内部触发器输入被选中时(由 TIMx_SMCR寄存器的TS位选择)。 注:CC2S仅在通道关闭时(TIMx_CCER寄存器的CC2E=’0’)才是可写的。 |

| 位7 | OC1CE:输出比较1清0使能 (Output compare 1 clear enable) 0:OC1REF 不受ETRF输入的影响; 1:一旦检测到ETRF输入高电平,清除OC1REF=0。 |

| 位6:4 | OC1M[2:0]:输出比较1模式 (Output compare 1 enable) 该3位定义了输出参考信号OC1REF的动作,而OC1REF决定了OC1的值。OC1REF是高电平 有效,而OC1的有效电平取决于CC1P位。 000:冻结。输出比较寄存器TIMx_CCR1与计数器TIMx_CNT间的比较对OC1REF不起作用; 001 :匹配时设置通道 1 为有效电平。当计数器 TIMx_CNT 的值与捕获 / 比较寄存器 1 (TIMx_CCR1)相同时,强制OC1REF为高。 010 :匹配时设置通道 1 为无效电平。当计数器 TIMx_CNT 的值与捕获 / 比较寄存器 1 (TIMx_CCR1)相同时,强制OC1REF为低。 011:翻转。当TIMx_CCR1=TIMx_CNT时,翻转OC1REF的电平。 100:强制为无效电平。强制OC1REF为低。 101:强制为有效电平。强制OC1REF为高。 110:PWM模式1- 在向上计数时,一旦TIMx_CNTTIMx_CCR1时通道1为无效电平(OC1REF=0),否 则为有效电平(OC1REF=1)。 111:PWM模式2- 在向上计数时,一旦TIMx_CNTTIMx_CCR1时通道1为有效电平,否则为无效电 平。 注1:一旦LOCK级别设为3(TIMx_BDTR寄存器中的LOCK位)并且CC1S=’00’(该通道配置成输 出)则该位不能被修改。 注2:在PWM模式1或PWM模式2中,只有当比较结果改变了或在输出比较模式中从冻结模式 切换到PWM模式时,OC1REF电平才改变。 |

| 位3 | OC1PE:输出比较1预装载使能 (Output compare 1 preload enable) 0:禁止TIMx_CCR1寄存器的预装载功能,可随时写入TIMx_CCR1寄存器,并且新写入的数 值立即起作用。 1:开启TIMx_CCR1寄存器的预装载功能,读写操作仅对预装载寄存器操作,TIMx_CCR1的 预装载值在更新事件到来时被传送至当前寄存器中。 注1:一旦LOCK级别设为3(TIMx_BDTR寄存器中的LOCK位)并且CC1S=’00’(该通道配置成输 出)则该位不能被修改。 注2:仅在单脉冲模式下(TIMx_CR1寄存器的OPM=’1’),可以在未确认预装载寄存器情况下使 用PWM模式,否则其动作不确定。 |

| 位2 | OC1FE:输出比较1 快速使能 (Output compare 1 fast enable) 该位用于加快CC输出对触发器输入事件的响应。 0:根据计数器与CCR1的值,CC1正常操作,即使触发器是打开的。当触发器的输入出现一个 有效沿时,激活CC1输出的最小延时为5个时钟周期。 1:输入到触发器的有效沿的作用就象发生了一次比较匹配。因此,OC被设置为比较电平而与 比较结果无关。采样触发器的有效沿和CC1输出间的延时被缩短为3个时钟周期。 该位只在通道被配置成PWM1或PWM2模式时起作用。 |

| 位1:0 | CC1S[1:0]:捕获/比较1 选择 (Capture/Compare 1 selection) 这2位定义通道的方向(输入/输出),及输入脚的选择: 00:CC1通道被配置为输出; 01:CC1通道被配置为输入,IC1映射在TI1上; 10:CC1通道被配置为输入,IC1映射在TI2上; 11:CC1通道被配置为输入,IC1映射在TRC上。此模式仅工作在内部触发器输入被选中时(由 TIMx_SMCR寄存器的TS位选择)。 注:CC1S仅在通道关闭时(TIMx_CCER寄存器的CC1E=’0’)才是可写的。 |

| 位15:12 | IC2F[3:0]:输入捕获2滤波器 (Input capture 2 filter) |

| 位11:10 | IC2PSC[1:0]:输入/捕获2预分频器 (input capture 2 prescaler) |

| 位9:8 | CC2S[1:0]:捕获/比较2选择 (Capture/compare 2 selection) 这2位定义通道的方向(输入/输出),及输入脚的选择: 00:CC2通道被配置为输出; 01:CC2通道被配置为输入,IC2映射在TI2上; 10:CC2通道被配置为输入,IC2映射在TI1上; 11:CC2通道被配置为输入,IC2映射在TRC上。此模式仅工作在内部触发器输入被选中时(由 TIMx_SMCR寄存器的TS位选择)。 注:CC2S仅在通道关闭时(TIMx_CCER寄存器的CC2E=’0’)才是可写的。 |

| 位7:4 | IC1F[3:0]:输入捕获1滤波器 (Input capture 1 filter) 这几位定义了TI1输入的采样频率及数字滤波器长度。数字滤波器由一个事件计数器组成,它记录到N个事件后会产生一个输出的跳变: 0000:无滤波器,以fDTS采样 1000:采样频率fSAMPLING=fDTS/8,N=6 0001:采样频率fSAMPLING=fCK_INT,N=2 1001:采样频率fSAMPLING=fDTS/8,N=8 0010:采样频率fSAMPLING=fCK_INT,N=4 1010:采样频率fSAMPLING=fDTS/16,N=5 0011:采样频率fSAMPLING=fCK_INT,N=8 1011:采样频率fSAMPLING=fDTS/16,N=6 0100:采样频率fSAMPLING=fDTS/2,N=6 1100:采样频率fSAMPLING=fDTS/16,N=8 0101:采样频率fSAMPLING=fDTS/2,N=8 1101:采样频率fSAMPLING=fDTS/32,N=5 0110:采样频率fSAMPLING=fDTS/4,N=6 1110:采样频率fSAMPLING=fDTS/32,N=6 0111:采样频率fSAMPLING=fDTS/4,N=8 1111:采样频率fSAMPLING=fDTS/32,N=8 注:在现在的芯片版本中,当ICxF[3:0]=1、2或3时,公式中的fDTS由CK_INT替代。 |

| 位3:2 | IC1PSC[1:0]:输入/捕获1预分频器 (Input capture 1 prescaler) 这2位定义了CC1输入(IC1)的预分频系数。 一旦CC1E=’0’(TIMx_CCER寄存器中),则预分频器复位。 00:无预分频器,捕获输入口上检测到的每一个边沿都触发一次捕获; 01:每2个事件触发一次捕获; 10:每4个事件触发一次捕获; 11:每8个事件触发一次捕获。 |

| 位1:0 | CC1S[1:0]:捕获/比较1选择 (Capture/Compare 1 selection) 这2位定义通道的方向(输入/输出),及输入脚的选择: 00:CC1通道被配置为输出; 01:CC1通道被配置为输入,IC1映射在TI1上; 10:CC1通道被配置为输入,IC1映射在TI2上; 11:CC1通道被配置为输入,IC1映射在TRC上。此模式仅工作在内部触发器输入被选中时(由 TIMx_SMCR寄存器的TS位选择)。 注:CC1S仅在通道关闭时(TIMx_CCER寄存器的CC1E=’0’)才是可写的。 |

事件产生寄存器(TIMx_EGR)

偏移地址:0x14

复位值:0x0000

| 位15:7 | 保留,始终读为0。 |

| 位6 | TG:产生触发事件 (Trigger generation) 该位由软件置’1’,用于产生一个触发事件,由硬件自动清’0’。 0:无动作; 1:TIMx_SR寄存器的TIF=1,若开启对应的中断和DMA,则产生相应的中断和DMA。 |

| 位5 | 保留,始终读为0。 |

| 位4 | CC4G:产生捕获/比较4事件 (Capture/compare 4 generation) 参考CC1G描述。 |

| 位3 | CC3G:产生捕获/比较3事件 (Capture/compare 3 generation) 参考CC1G描述。 |

| 位2 | CC2G:产生捕获/比较2事件 (Capture/compare 2 generation) 参考CC1G描述。 |

| 位1 | CC1G:产生捕获/比较1事件 (Capture/compare 1 generation) 该位由软件置’1’,用于产生一个捕获/比较事件,由硬件自动清’0’。 0:无动作; 1:在通道CC1上产生一个捕获/比较事件: 若通道CC1配置为输出: 设置CC1IF=1,若开启对应的中断和DMA,则产生相应的中断和DMA。 若通道CC1配置为输入: 当前的计数器值捕获至TIMx_CCR1寄存器;设置CC1IF=1,若开启对应的中断和DMA,则产 生相应的中断和DMA。若CC1IF已经为1,则设置CC1OF=1。 |

| 位0 | UG:产生更新事件 (Update generation) 该位由软件置’1’,由硬件自动清’0’。 0:无动作; 1:重新初始化计数器,并产生一个更新事件。注意预分频器的计数器也被清’0’(但是预分频系 数不变)。若在中心对称模式下或DIR=0(向上计数)则计数器被清’0’,若DIR=1(向下计数)则计数 器取TIMx_ARR的值。 |

计数器(TIMx_CNT)

偏移地址:0x24

复位值:0x0000

| 位15:0 | CNT[15:0]:计数器的值 (Counter value) |

自动重装载寄存器(TIMx_ARR)

偏移地址:0x2C

复位值:0x0000

| 位15:0 | ARR[15:0]: 自动重装载的值 (Auto reload value) ARR包含了将要传送至实际的自动重装载寄存器的数值。 当自动重装载的值为空时,计数器不工作。 |

2000

2000

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?