ESD 保护方案

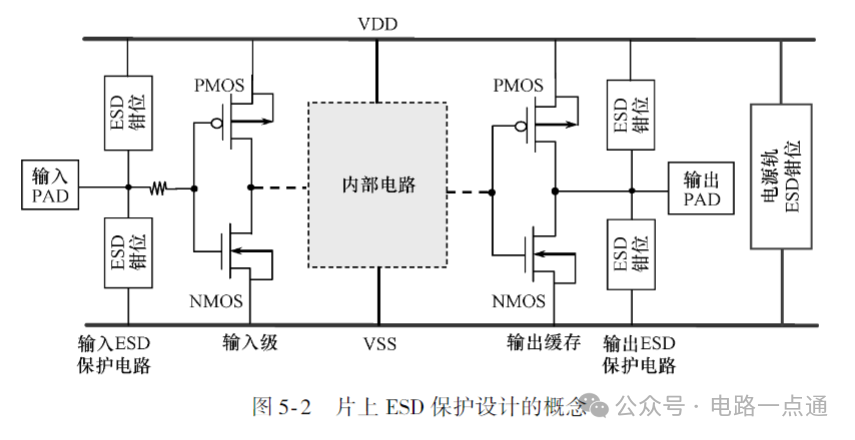

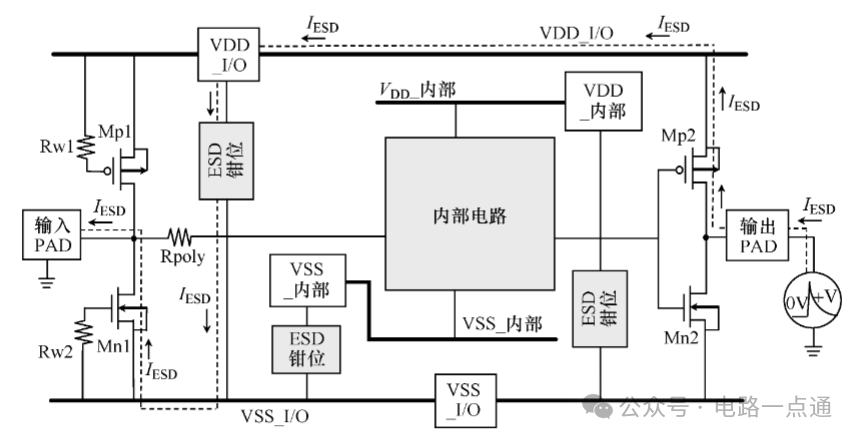

图 5- 2 所示的片上保护设计概念被用来避免来自几乎随机组合的引脚之间的HBM / MM ESD 应力损伤。对每一个输入或输出引脚, 在压焊点与 VDD 和 VSS 电源线之间采用 ESD 钳位器件, 用于泄放 I / O 引脚上的四种模式的 ESD 应力。为了克服引脚到引脚之间的 ESD 应力和 VDD 到 VSS 之间的 ESD 应力, 在 IC 的VDD 与 VSS 电源线之间必须放置电源轨 ESD 钳位电路[4,5] 。对大多数逻辑 IC,I / O 电路的电源引脚通常与核心电路的电源引脚分开, 以避免噪声耦合, 并且可以减小地弹。图 5- 3 所示为典型的采用独立电源引脚的整个芯片 ESD 保护方案。

图 5- 2 片上 ESD 保护设计的概念除了输入与输出端口的 ESD 钳位器件, 对 IC 中所有器件和电路防止 ESD 损伤( 特别是针对引脚到引脚和 VDD 到 VSS 的 ESD 应力) , 实现整个芯片保护的最重要的设计是合理排布电源线, 并且在不同的电源线之间采用电源轨 ESD 钳位电路。如图 5- 3 中虚线所示, ESD 电流泄放通路或在引脚对引脚 ESD 放电下的 IC,可以通过使用 I / O ESD 器件、 金属电源线和电源轨 ESD 钳位电路来建立。

使用正确的整片 ESD 保护计划, 通过位于 I / O 端口的 ESD 钳位器件和位于电源轨之间的 ESD 钳位电路, 才能实现对核心电路的有效保护。

图 5- 3 IC 中 I / O 电路和内部电路采用不同电源引脚的整片 ESD 保护方案

大多数传统的 ESD 保护设计集中在针对 I / O 端口的 ESD 保护电路和器件,

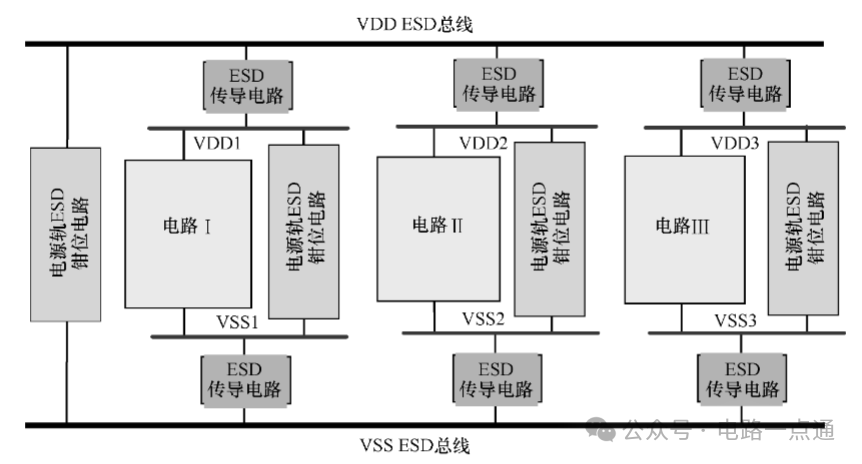

这可以给四种引脚组合模式的 I / O 端口提供针对 ESD 应力的保护。但是, 位于I / O 端口的 ESD 保护电路或器件不能针对引脚到引脚和 VDD 到 VSS 的 ESD 应力实现对内部电路足够的保护, 从而经常发生 ESD 应力引起内部电路失效, 但在I / O 端口的 ESD 器件并没有发生失效。对于采用多个独立电源的 IC 来说, 建议采用的整片 ESD 保护方案如图 5- 4 所示, 一个著名半导体生产线的设计规则中采用了这种设计。

图 5- 4 针对拥有多个不同电源线的 IC 整片 ESD 保护方案

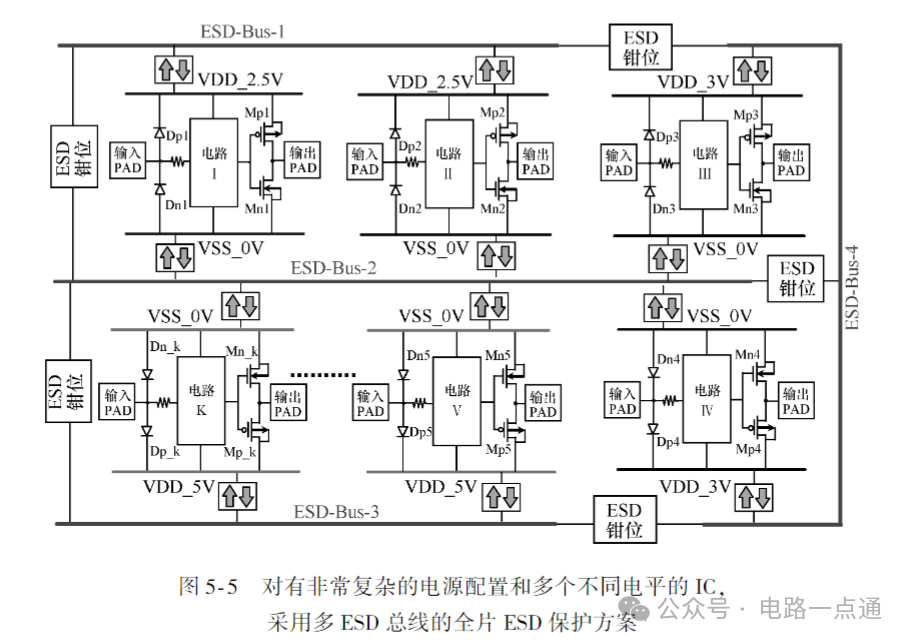

VDD ESD 总线与独立电源 ( VDD1, VDD2, VDD3 ) 之间的ESD 传导电路使用层叠二极管[7] 甚至是双向晶闸管 ( SCR) 整流器[8,9] 。对一个采用具有多个不同电平的复杂电源的 IC ( 例如片上系统 ( SoC) ) , 采用多个 ESD 总线的整片 ESD 保护方案如图 5- 5 所示。在整片 ESD 保护方案中, 位于 I / O 端口和 电 源 轨 之 间 的 ESD 钳 位 器 件 仍 然 可 以 实 现 对 内 部 电 路 的 安 全保护。

1648

1648

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?