SRAM读写时序;

读/写周期波形图精确地反映了SRAM工作的时间关系。我们把握住地址线、控制线、数据线三组信号线何时有效,就能很容易看懂这个周期时序图。

在读周期中,地址线先有效,以便进行地址译码,选中存储单元。为了读出数据,片选信号CS和读出使能信号OE也必须有效(由高电平变为低电平)。从地址有效开始经tAQ(读出)时间,数据总线I/O上出现了有效的读出数据。之后CS非、OE非信号恢复高电平,tRC以后才允许地址总线发生改变。tRC时间即为读周期时间。

在写周期中,也是地址线先有效,接着片选信号CS非有效,写命令WE非有效(低电平),此时数据总线I/O上必须置写入数据,在tyo时间段将数据写入存储器。之后撤销写命令WE和CS。为了写入可靠,I/O 线的写入数据要有维持时间thD, CS非的维持时间也比读周期长。twc时间称为写周期时间。为了控制方便,一般取 tRc=twc,通常称为存取周期。 SRAM的工作原理:

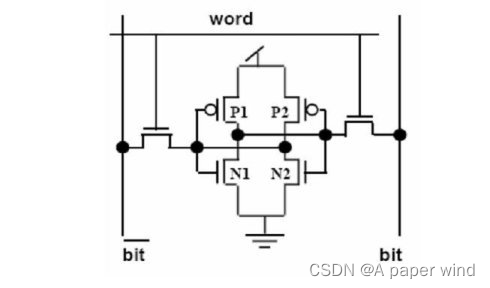

在静态存储器器件中,一位由6只晶体管组成,称为一个存储元,如图所示:

N1和N2构成触发器,P1和P2分别作为Q1和Q2的负载电阻。N1截止而N2导通时的状态称为"1"。相反的状态称为"0"。

读出时,置选择线为高电平,使两个开关管导通,从读/写线输出原存的信息。

写入时,写入数据使读/写线呈相应电平(例如写"1"时,读/写线"1"为高电平,读/写线"0"为低电平),再使选择线为高电平,于是触发器被置为相应的状态(写"1"时,置为"1"状态,即N1截止N2导通)。显然,无论存储元保存的信息是"1"还是"0",N1,N2,P1和P2,4只MOS管总有两只处于导通状态。

1217

1217

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?