FPGA实现功能的方式与其他芯片通过软件实现方式有所不同,简单的来说,它是通过高级语言来控制内部资源的分配来实现想要的功能,我们所编写的语言知识将想要实现的功能描述出来,然后通过编辑器来转换成芯片能够识别的代码,实现内部资源的布线,实现功能。

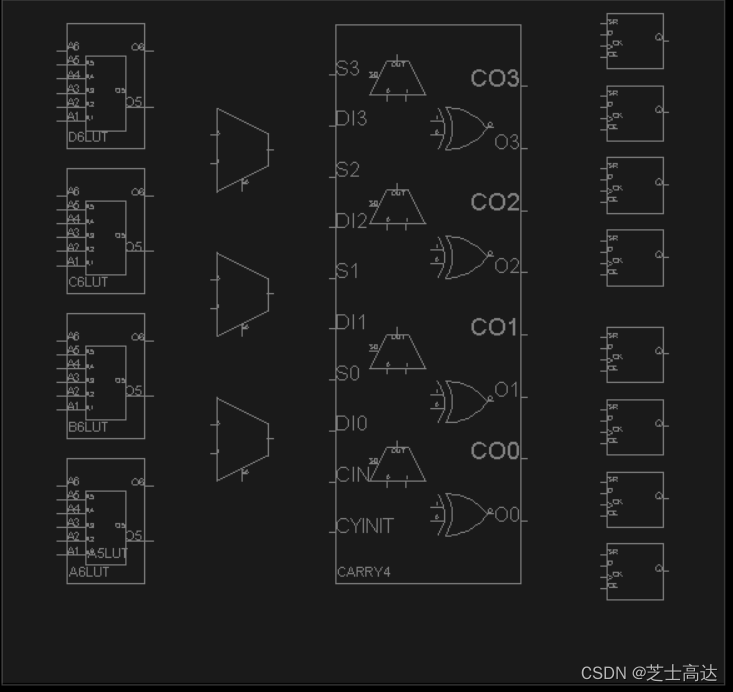

FPGA内部有很多可供用户任意配置的资源,其中包括:可编程逻辑、可编程I/O、互连线、IP核等资源,很多学过数字电路的人都知道与或非门可以构成几乎所有的数字电路,但是FPGA内部最基本的主要单元并不是这些与或非门,而是由无数个查找表 (Look Up Tabe,简称为LUT)和寄存器构成。

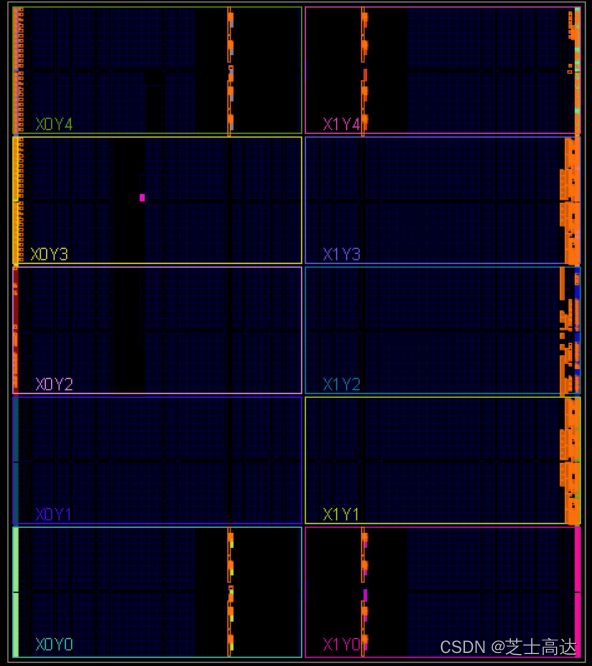

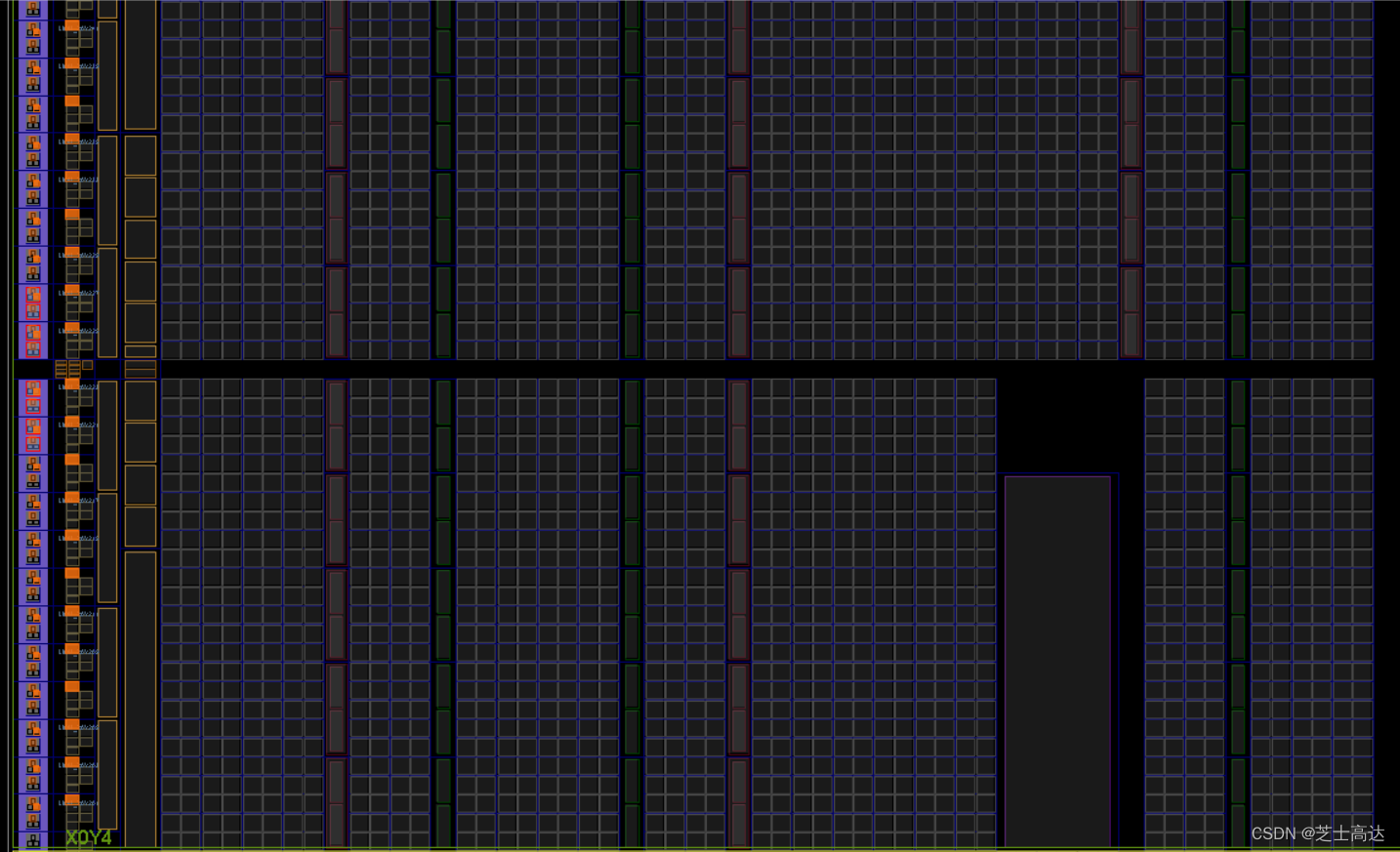

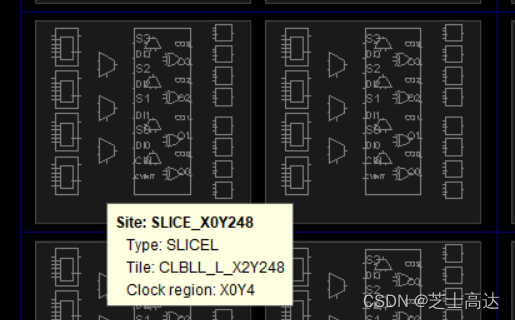

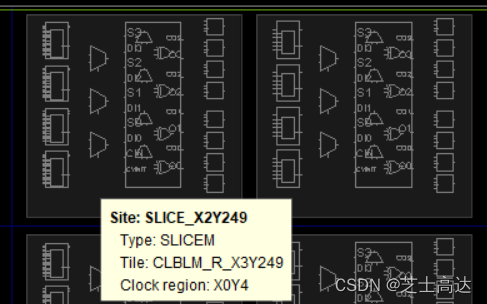

上图是在Vivado中查看的芯片内部资源情况,可以通过放大来实现查看内部资源情况,让我们更好的学习,一片FPGA芯片中包含了数以万计的LUT模块,是功能实现的主力资源,下面图中的一个一个小方格都是SLICE,每一个SLICE中包含了4个LUT与一些逻辑门。

每两个SLICE被包括在一个CLB中,SLICE有两种类型,分别为SLICEL(L是指Logic)和SLICEM(M是指Memory),SLICEL和SLICEM的区别是,SLICEM中含有能够把LUT资源重新整合为Ram和Rom的逻辑。

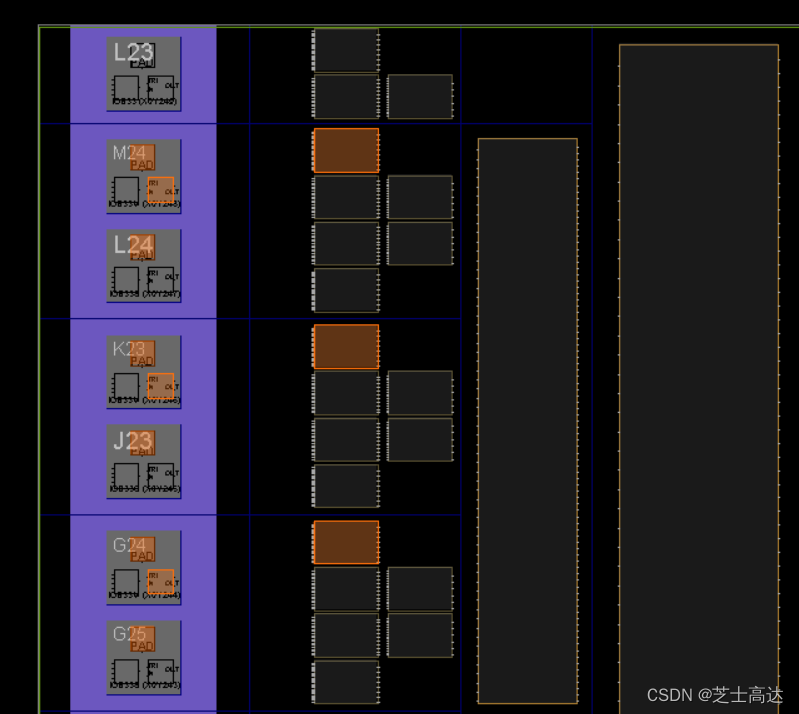

在芯片的边部包含了一些 I/O 的调节模块,以及接收数据可能用到的FIFO(先进先出寄存器),PLL(锁相环)等,在FIFO例化的时候可以将BLOCK RAM设置为FIFO,不会使用额外的CLB资源,并且这部分RAM是真双口RAM。因为刚开始学习所以对一些内部资源并不是特别关心,主要理解FPGA内部的工作原理即可,剩下的活就交给编译器来干。

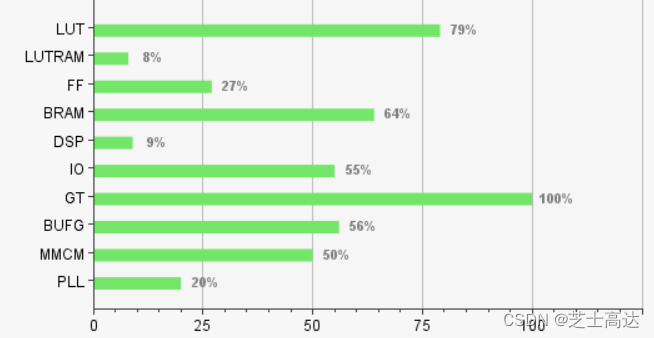

上面的图中可以看到有不少颜色不一样的部分,黄色的部分是被占用的部分,当一个程序综合完成后,以Vivado为例,综合之后能够看到资源的占用情况,比如占用了多少LUT资源,多少I/O被占用等等。

占用内部资源情况报告

对于新手来说,内部资源并不需要非常的了解,有很多的模块只要会使用就行,还是那句话,这些事情留给编译器来做就好,新手只需对内部的资源分配有一个简单的了解,首先还是需要将语法等等实现熟记于心。

有错误期待大佬指正,因为我也是个新手可能逻辑并不是十分清晰,写作不易点个赞走吧!!!

1046

1046

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?