一开始不是点灯,而是了解FPGA器件的内部结构,掌握硬件描述语言和内部单元和连线的映射关系。

这里以Altera FPGA为例,无论是Xilinx,Altera,Lattice和国产 ,它们的内部架构以及开发软件都大同小异,一通则百通。

参考的文档:Stratix II Handbook

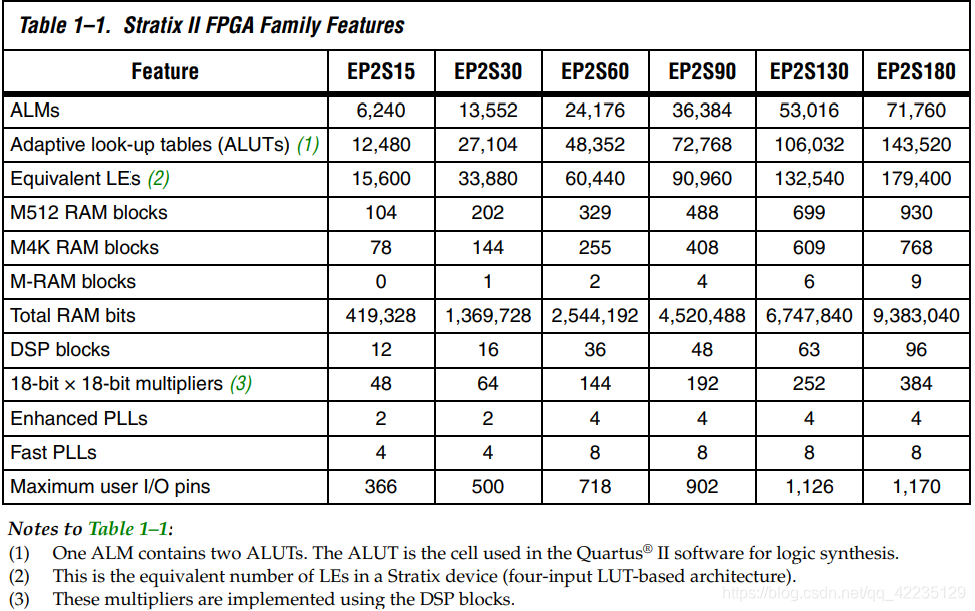

首先看一下Features,包含ALMs,LEs,RAM,DSP Blocks,Multipliers,PLLs等。

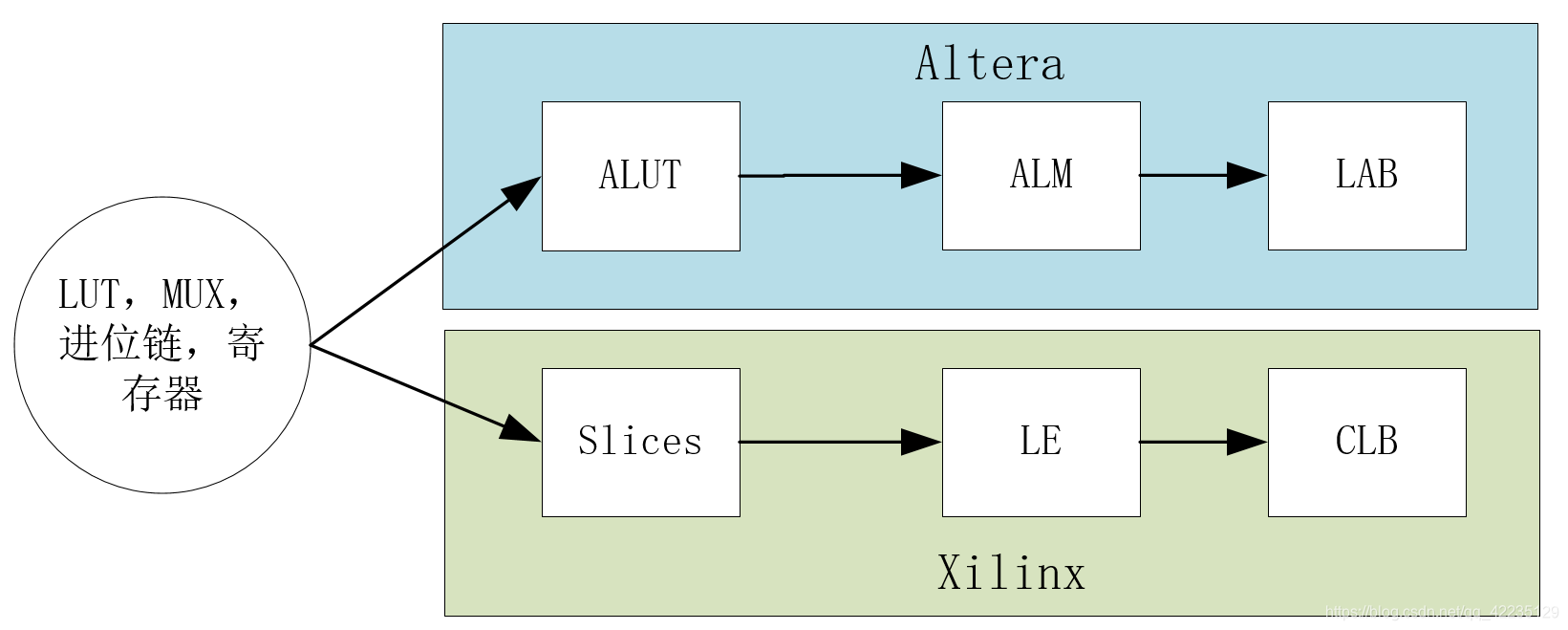

Xilinx FPGA中的CLB(Configable Logic Block)包含Slices和DRAM。LE(logic cells)是由Slices构成的,每一个Slices基本是由LUT(look-up table)、进位链、MUX和寄存器组成。

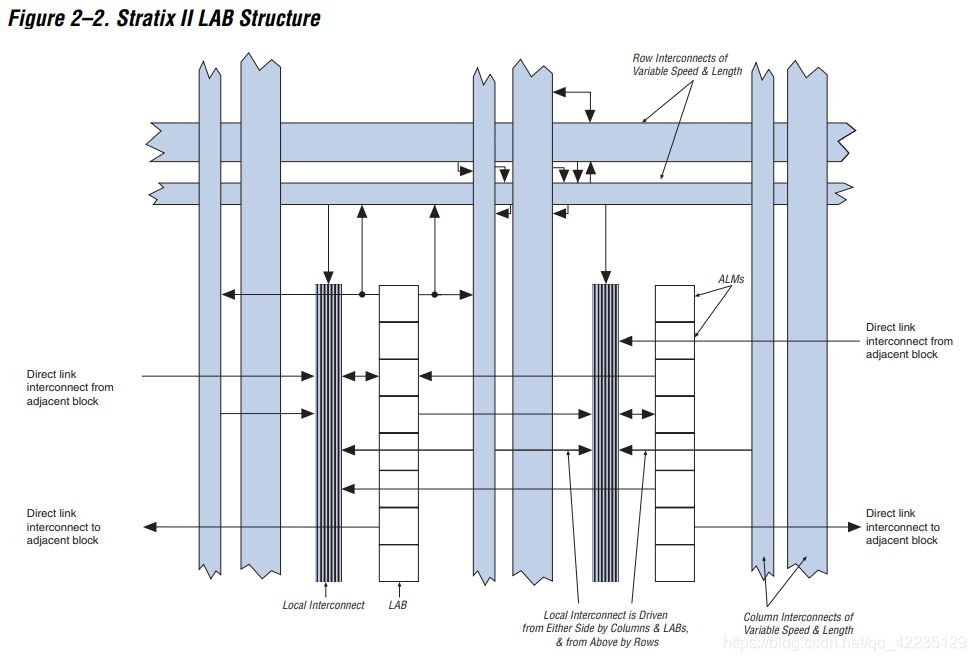

Altera FPGA中的基本单元是LAB(Logic Array Block),each LAB consists of eight ALMs, carry chains, shared arithmetic chains, LAB control signals, local interconnect, and register chain connection lines.下面是LAB的结构图。

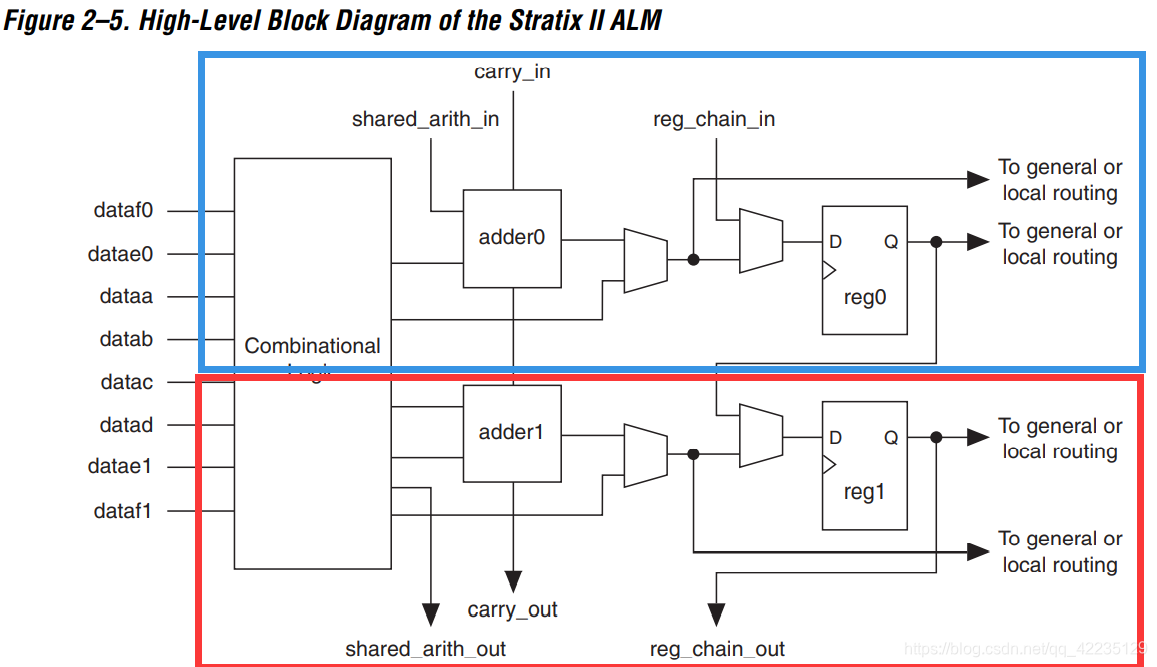

一个ALM包含两个ALUTs。下面是ALM的结构。

下面就是要分别弄清楚LUT,进位链,MUX;然后就可以理解ALUT,进而是ALM,最后理解LAB。

下面是Xilinx和Altera内部结构的对应关系,只是名字不一样罢了。

下面的内容是下一步需要去学习和实践的。

LUT

- 理解LUT与真值表的关系,明白FPGA为什么用LUT来替代门电路,以及这样做的好处。

- 理解FPGA 是如何通过两个相同输入的LUT5和一个MUX组成LUT6的。

MUX

- 理解MUX中输出与地址码,数据输入的关系。

- 理解硬件描述语言与MUX的对应关系。

- 理解FPGA中用LUT6组成的MUX4:1。LUT6和MUXF7,MUXF8组成的MUX8:1,MUX16:1。

进位链

- 理解什么是加法器,内容包括半加器,全加器,多位加法器。

- 联系多位加法器来理解XILINX FPGA进位链的结构以及功能。

存储单元

- 理解存储单元(触发器Flip-Flop和锁存器Latch)的结构

- 结合LUT、MUX和进位链,理解CLB的整体结构

了解了FPGA的内部结构之后,写HDL代码的时候就要想着代码和硬件电路的映射关系了。

参考:

1045

1045

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?