4位递增计数器的设计

任务描述

本关任务:设计一个4位二进制(十六进制)同步递增计数器,要求具有同步置数、异步清零功能。

相关知识

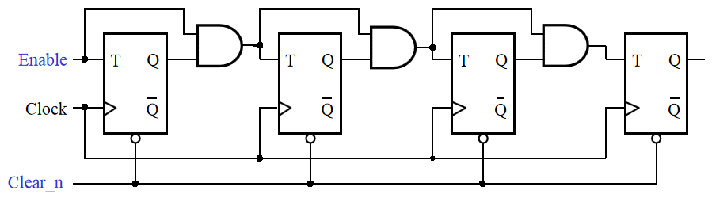

计数是一种最简单的基本运算。计数器就是实现这种运算的逻辑电路,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器在数字系统中应用广泛,如在电子计算机的控制器中对指令地址进行计数,以便顺序取出下一条指令,等等。 1)同步 2 n 2^n 2n进制递增计数器(用T触发器实现,图1“骨肉相连”模型)

图中n=4,T触发器的序号左起依次为0,1,⋯,n−1,Enable=0时保持,Enable=1时计数。

T触发器可以看成是 2 1 2^1 21进制计数器,Q既是状态又是进位输出。

T 0 = E n a b l e T_0 = Enable T0=Enable

T 1 = Q 0 ⋅ T 0 = Q 0 ⋅ E n a b l e T_1 = Q_0\cdot T_0 = Q_0\cdot Enable T1=

本文详细记录了4位二进制同步递增计数器的设计过程,包括同步置数和异步清零功能。通过介绍T触发器和D触发器的实现方式,阐述了计数器的工作原理。此外,还探讨了六进制计数器的设计,利用反馈原理实现同步置数和异步清零,并提供了设计中的注意事项和解决冲突的策略。

本文详细记录了4位二进制同步递增计数器的设计过程,包括同步置数和异步清零功能。通过介绍T触发器和D触发器的实现方式,阐述了计数器的工作原理。此外,还探讨了六进制计数器的设计,利用反馈原理实现同步置数和异步清零,并提供了设计中的注意事项和解决冲突的策略。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1560

1560

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?