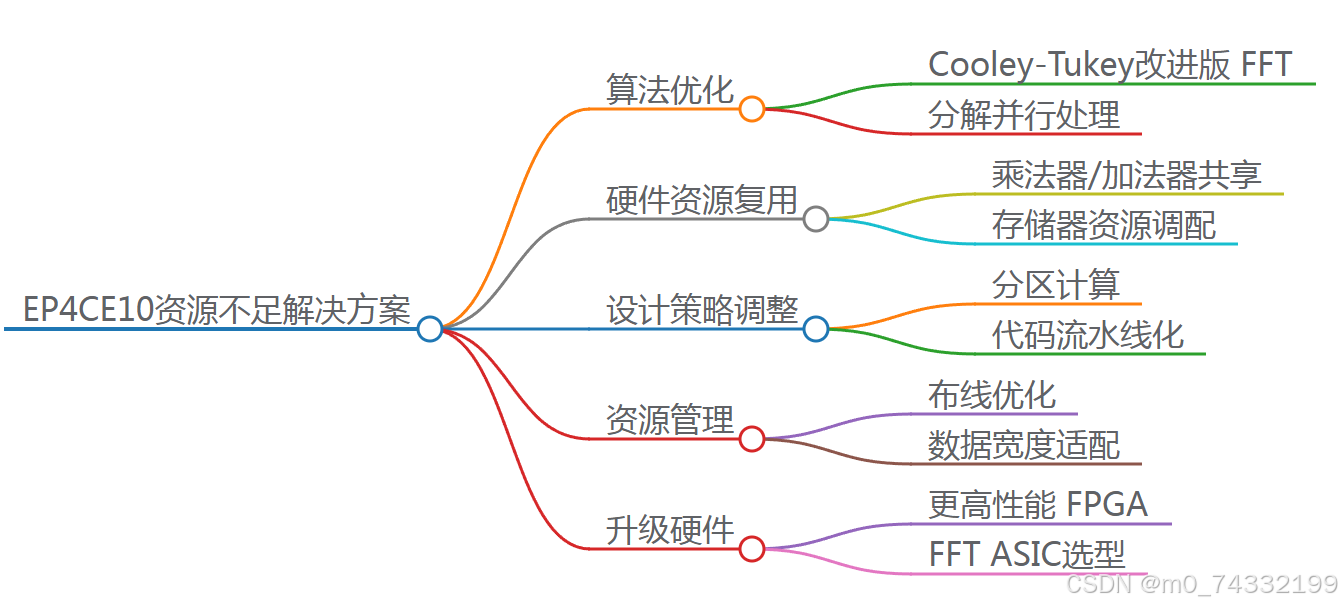

EP4CE10是一款FPGA芯片,用于数字信号处理(DSP)应用,但它在运行1024点FFT(快速傅里叶变换)时遇到资源不足的问题。解决这个问题可以考虑以下几个策略:

-

算法优化:尝试使用更高效的FFT算法,如Cooley-Tukey算法的改进版本,它们通常能减少计算量。比如,通过将大规模的FFT分解成小块并行处理,可以降低对资源的需求。

-

硬件复用:检查现有的硬件模块是否可以共享。例如,如果有多余的乘法器、加法器或者存储器,可以利用这些资源来提高FFT单元的性能。

-

分区设计:可能的话,可以将1024点的FFT拆分成几个较小的子任务,在多个可用的DSP核之间分配执行,减小单个核心的压力。

-

代码流水线化:通过流水线技术,可以在一条指令上同时执行多个操作步骤,提高运算效率,从而节省资源。

-

资源预分配和管理:在设计阶段合理规划,避免不必要的资源浪费。这包括在布线阶段优化数据流,以及选择适当的数据宽度以匹配硬件限制。

-

升级硬件:如果上述方法无法满足需求,可能需要考虑升级到更高性能等级的FPGA或采用专门针对FFT加速的专用集成电路(ASIC)。

-

什么是Cooley-Tukey FFT算法的优化升级版,以及它相比于标准FFT有哪些效率提升?快速傅里叶变换(Fast Fourier Transform,FFT)的Cooley-Tukey版本通常指的是一种分治法的并行算法,由J.W. Cooley和John Tukey于1965年提出。它是计算离散傅立叶变换的标准方法,尤其是对于大数组而言,它的效率远高于直接计算每个点的DFT。Cooley-Tukey FFT的核心思想是将复数信号分解成两个长度相等的子序列,分别对它们进行递归的FFT,然后合并结果。这个过程通过分割和重组(称为“蝴蝶”运算)的方式,减少了计算次数,从O(n^2)降低到了O(n log n),其中n是输入信号的长度。相比于标准的递归FFT,Cooley-Tukey FFT的优化体现在以下几个方面:并行化:由于数据的分解处理可以独立进行,这使得FFT在现代计算机系统(如多核处理器或GPU)上易于并行化,进一步提升了计算速度。存储效率:只需要存储中间结果,而不需要保存整个过程中所有的中间步骤,节省了内存空间。算法复杂度:通过分治策略,大大降低了计算工作量,尤其对于长信号来说,效率优势更为明显。

-

如何有效地将一个1024点的快速傅立叶变换(FFT)分解为多个子任务,并将其分布在多个可利用的数字信号处理器(DSP)核心上并行执行?要有效地将1024点的快速傅立叶变换(FFT)分解为子任务并分布式处理,可以采用以下步骤:分解 FFT 算法:将1024点的 FFT 分解为递归或分治的形式,如Cooley-Tukey算法,它将大变换分解成一系列小规模的子变换(比如大小为512、256等的子FFT)。确定工作负载:计算每个子FFT所需的计算量,以及在可分配的DSP核心数目下如何均衡分配这些任务。这可能涉及到划分数据和子变换的数量。创建并行结构:设计一个多线程或多核并行架构,每个DSP核心负责执行一部分子FFT。例如,在多核处理器上,可以将每个核心分配给一个独立的子序列;而在多处理器系统中,可以通过网络通信来交换数据和结果。数据分发:将输入数据分割成适当的块,以便每个核心都能接收到它们的工作部分。这可能涉及零填充或其他技术来保持信号完整性。同步与通信:为了保证最终结果的正确性,需要设计有效的同步策略,比如在每个子任务完成后进行全局加总,或者在某些节点之间交换中间结果。错误检测与恢复:并行计算中可能出现的数据竞争和同步问题需要考虑错误检测和恢复机制。优化性能:使用高效的并发库和调度算法,以减少数据移动开销和提高吞吐量。

1549

1549

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?