一、D-PHY MIPI 简介

MIPI C-PHY 是一种嵌入式时钟链路,可为重新分配链路内的通道提供很大的灵活性。它还提供高速和低功耗模式之间的低延迟转换。MIPI C-PHY 通过摆脱传统的两线通道差分信号技术,引入大约 2.28 位/符号的三相符号编码来实现这一点,以在三线通道或“三重奏”上传输数据符号,其中每个三重奏包括一个嵌入式时钟。该规范在标准信道上支持高达 6 Gigasymbols (Gsps) 的符号率,相当于 13.7 Gbps,在短信道上支持高达 8 Gsps。三个以 6 Gsps 运行的三重奏通过九线接口实现了大约 41 吉比特每秒 (Gbps) 的峰值数据速率。

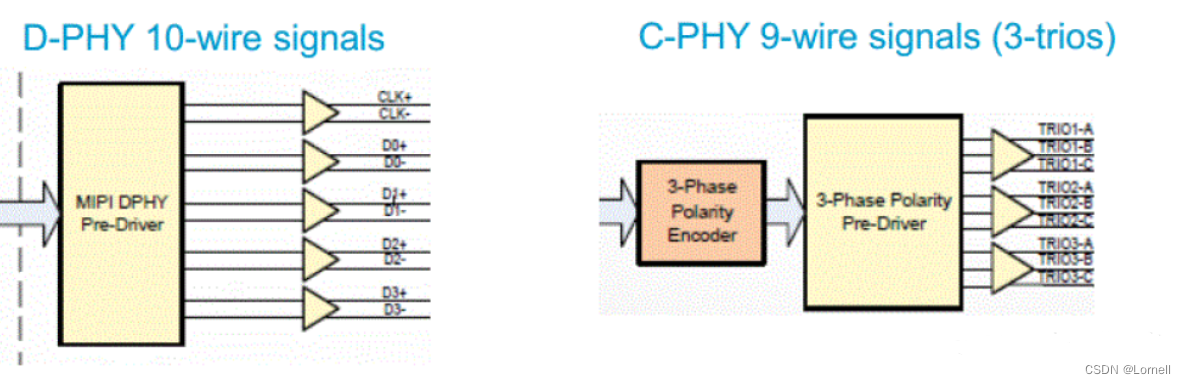

D-PHY由最多4组最少1组数据通道差分信号对和1组时钟差分信号对组成,这种设计非常常见,行业在PCB设计、布线积累了大量经验,等长、阻抗等设计很成熟。类比USB-C 3.1,也是包含了4组Super Speed的差分信号。

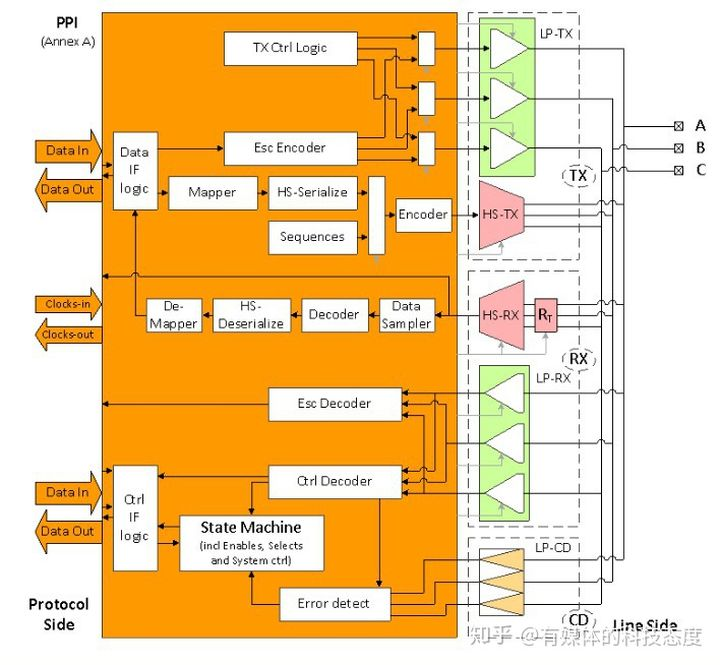

新版本的 MIPI C-PHY 2.1 版引入了 64 位 PHY 协议接口 (PPI),为物理接口和芯片核心逻辑之间的更宽总线提供选项,从而更好地支持更高性能的应用程序。C-PHY v2.1 与之前版本的 C-PHY 完全兼容。

二、C-PHY的原理和特性

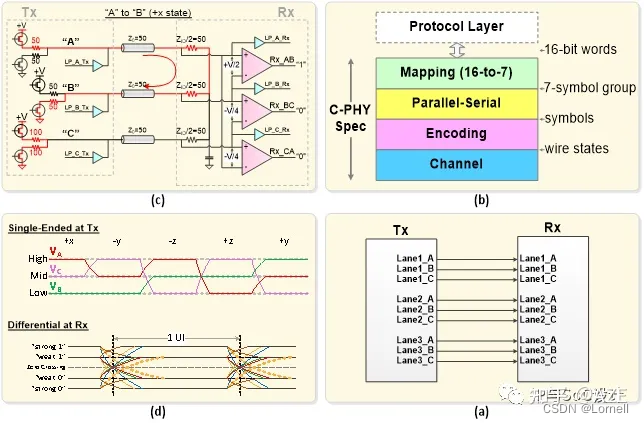

图a中的框图显示了一个三通道的C-PHY的TX和RX是如何连接的。图b显示了C-PHY子系统的不同子块,即映射、并行/串行功能、编码和通道。图c是TX和RX之间交互的更详细的图片,图4(d)说明了C-PHY的信令级别。

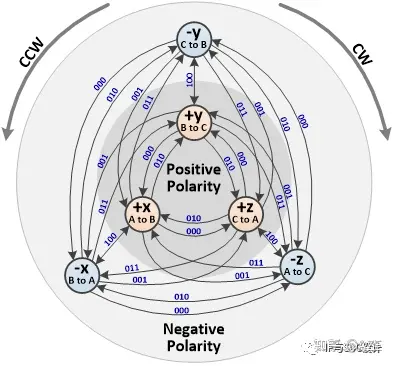

CPHY“线态”变化图

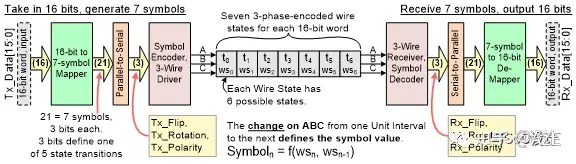

C-PHY 编码和映射功能概述

三、MIPI C-PHY与MIPI D-PHY差异

MIPI C-PHY 可以与MIPI D-PHY 共存于同一器件引脚上,因此设计人员可以开发双模器件。链路的运行数据速率可能是不对称的,这使实施者能够根据系统需求优化传输速率,并且还可以仅使用 C-PHY 的高速信号级别来实现链路运行。双向和半双工操作是可选的。

MIPI C-PHY 包括快速总线周转 (BTA) 以及备用低功耗 (ALP) 功能,该功能可仅使用 C-PHY 的高速信号电平实现链接操作。

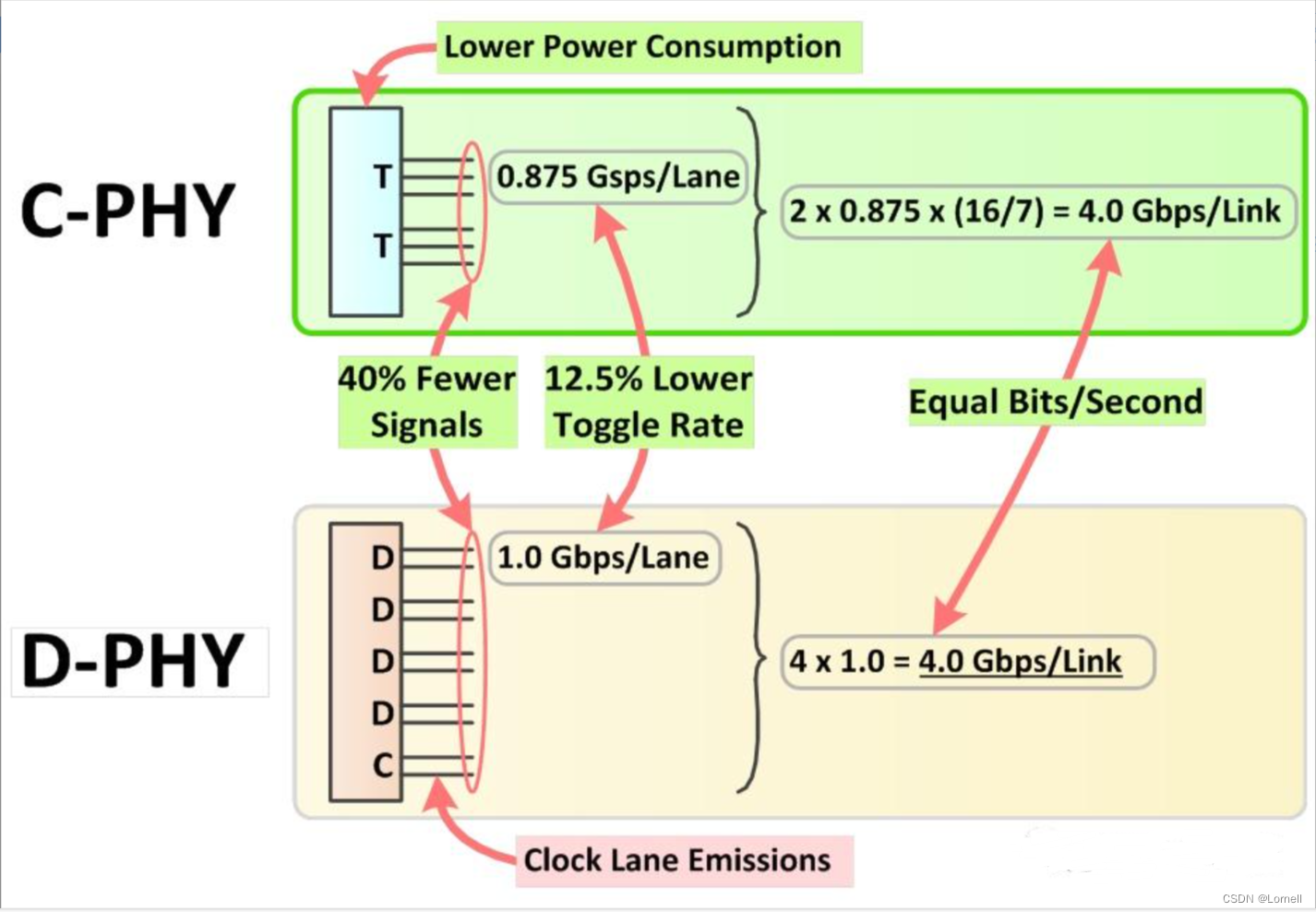

支持 4Gbps 聚合数据速率并使用相同转换速率的 D-PHY 和 C-PHY 之间的比较如下图:

C-PHY 与 D-PHY wire的区别

四、D-PHY与C-PHY参数计算

1、D-PHY应用时的计算方法:

以1902*1080p @ 60hz, raw10,2 lane为例:

像素时钟 = 2200 * 1125 * 60 = 148.5MHz

带宽/数据率 = 148.5 * 10 = 1.485Gbps

lane rate = 1.1485/2 = 742.5Mbps

bit clock = 742.5/2 = 371.25MHz

2、C-PHY应用时的计算方法:

C-PHY是〜2.28位/符号的三相符号编码,以1902*1080p @ 60hz, raw10,2 lane为例:

像素时钟 = 2200 * 1125 * 60 = 148.5MHz

带宽/数据率 = 148.5 * 10 = 1.485Gbps

lane rate = (1.1485/2.28)/2 = 326.7Msps

2073

2073

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?