一、常用的时钟源

如果把数字电路比作人体,时钟则相当于人体的血液,而时钟源则相当于人体的心脏,常用的时钟源包括RC振荡电路、晶体振荡电路、压空振荡电路(VCO)、PLL(锁相环)时钟电路和时钟分频电路等,其中:

(1)RC振荡电路由电阻和电容构成,通过电荷的充放电的过程来产生精确定时信号。它可以用作简单的定时器和计时器,但精度相对较低,一般集成于MCU的芯片中,常应用于低功耗、低成本的设计中;

(2)晶体振荡电路使用晶体作为振荡元件,通过晶体的特性来产生稳定的振荡信号。晶体振荡器具有高精度和稳定性,常用于需要高精度时钟的应用,常见用于MCU等处理器芯片外接电路;

(3)VCO是一种可以通过调节控制电压来改变输出频率的振荡器。它常被用于频率合成器、频率调制解调器等应用中,可以根据控制电压的变化来实现频率的可调;

(4)PLL是一种反馈控制系统,用于生成稳定的时钟信号。它包含一个参考时钟信号、相位比较器、锁定环路滤波器和控制电压控制振荡器(VCO)。PLL 可以将输入时钟信号锁定在特定频率上,并且具有抗干扰和抖动的能力,常见于高频模拟电路和高速数字电路中,例如通信电路的调制上变频与解调下变频电路、FPGA与CPLD及高速CPU等应用;

(5)时钟分频电路:时钟分频电路通过将输入的高频时钟信号分频,生成较低频率的时钟信号。它通常基于计数器和逻辑门实现,用于将高频时钟信号分解成系统所需的各种频率;

晶体振荡电路的实物形式有两种,即有源晶振和无源晶体,其中有源晶振是振荡电路和无源晶体的集成体,使用时仅需要提供电源即可正常使用,应用方法相对简单,但成本相对较高;无源晶体成本相对较低,但使用时需要MCU等提供外部的振荡电路驱动,并且设计必要的电路(匹配电容、串并联电阻等)保证晶体正常工作,该电路设计对晶体至关重要,下面将从原理与应用实践两方面进行重点分享。(原理部分为网络资料整理,应用实践部分为实际工作经历分享)

二、晶体振荡器相关原理

1、有源晶振与无源晶体

数字电路设计中常用的晶体振荡器分为无源晶体和有源晶振两种类型。无源晶体与有源晶振的英文名称不同,无源晶体为crystal(晶体),而有源晶振则叫做oscillator(振荡器)。无源晶体需要借助于外接时钟电路才能产生振荡信号,自身无法振荡起来,所以“无源晶振”这个说法并不准确;有源晶振是一个完整的谐振振荡器。

2、石英晶体的主要参数指标

(1)谐振频率:

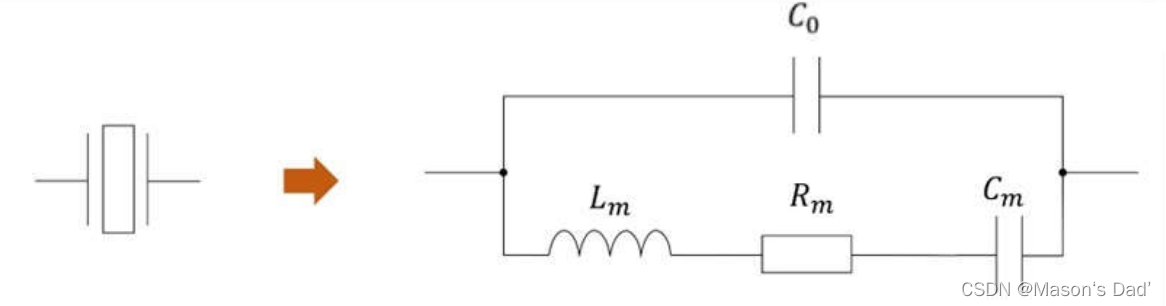

无源晶体通常指的就是石英晶体,石英晶体是一种可将电能和机械能相互转化的压电器件,能量转变发生在共振频率点上。它可用如下模型表示:

C0:等效电路中与串联臂并接的电容,也叫并电容,静态电容,其值一般仅与晶体的尺寸有关;

Lm:动态等效电感,代表晶体机械振动的惯性;

Cm:动态等效电容,代表晶体的弹性;

Rm:动态等效电阻,代表电路的损耗;

石英晶体电抗的频域特性如下曲线所示:

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7133

7133

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?